半导体产业的变化,使得Cadence的解决方案不仅完整,

更具备了前后连贯的特色,为的就是希望从问题的源头开始,

设法将每个环个环结所面临的问题,作一次性的解决。

过去大家对于EDA(电子设计自动化)的印象,大多停留在扮演芯片设计软件工具供货商的角色,随着全球半导体产业的不断变化,EDA产业也有了全新的样貌。其中Cadence(益华计算机)应该可以说是变化相当大的业者。

众所皆知,Cadence在既有的EDA与硅智财(IP)已经耕耘相当长的一段时间,在PCB(印刷电路板)设计领域,Cadence同样也有相当优异的成绩。由于PCB已经进入了终端系统设计整合的阶段,对Cadence而言,该公司已经从「协助IC设计」的定位,转变成「协助系统设计」,所以强化PCB设计软件的能力也成了Cadence十分重视的课题。

设计垂直流程的一次到位

由于从芯片到PCB设计,Cadence拥有完整的产品组合,在策略上,就是希望能从芯片设计一路贯穿到PCB设计,这中间包含芯片IO电路方块(IO Cell)、封装承载芯片接脚(die pad)、封装与PCB板间接脚(BGA)等,在考虑走线平顺前提下,自动完成优化处理。透过封装层级的自动布线功能 (APR) 及PCB层级的交互式自动布线功能 (Allegro Auto-Interactive Routing) 进行早期评估,就是希望能在芯片设计之初,就要考虑到封装与PCB设计的问题,以直接减轻PCB设计的负担,这种概念被Cadence称为「IC-Package-PCB Co-design」。

Cadence技术服务部资深应用工程经理林谓昌就表示,这个概念最早就是由Cadence所提出,许多芯片大厂也早已采用这样的概念平台进行芯片设计,上游的芯片或是设计服务业者可利用此协同设计概念来强化芯片与封装设计对各式PCB设计的兼容性;中下游的ODM与OEM业者则透过Allegro交互式自动布线工具来提升设计效能与质量。

| 图一 : 每个终端系统都会有芯片到系统设计的阶段,Cadence以完整连贯的解决方案来满足市场需求。 |

|

PCB设计 由Allegro担纲主角

若单以PCB设计来说,其相关系列的产品线,Cadence则是以「Allegro PCB Designer」作为代表。

林谓昌谈到,你可以把PCB想象成一座航空母舰,不同的芯片都放在同一个载板上,有主被动组件,高度有高有低,整个系统设计过程会牵涉到高速数字讯号布线问题(像DDR4、PCIE Gen3与USB3.1等,电源供应系统设计,因电生热问题,机构与电路板兼容问题及最终EMI(电磁干扰)设计。

一个好的设计平台,若能将物理层级(布线、机构)与电性层级(电源、热、EMI)整合考虑,达到首次设计成功,那将会大大降低成本并提升产品质量。Allegro PCB设计及Allegro-Sigrity电性协同分析平台即能达成此目的。

物理层级设计是一切产品的基础,布线质量与快速完成时间往往是产品设计的重点要求,而Allegro TimingVision正是为此诞生。

TimingVision克服高速数字讯号设计问题

Allegro TimingVision平台试图解决高速讯号的设计与电路布局所面临的挑战。林谓昌进一步谈到,芯片之间的沟通,是透过频率来调度数据传输与控制讯号,但问题在于,即便芯片之间讯号走线的距离相等,数据/控制讯号和参考频率(或strobe) 的抵达时间却不见得会相同,更甚者两者的误差之大,将十分容易造成讯号在电路接收端无法满足判断讯号逻辑所需最小的建置与维持时间(Setup/Hold time) 的情况。在PCB面积有限与线宽间距等诸多条件限制下达成时序收敛是一大挑战。林谓昌透露,一般大家所了解的「差动讯号」像是USB、PCI Express、SATA、以太网络及DDR3/4等技术,这类的电路是整个系统布局最为困难的部份。因此Cadence以Allegro TimingVision核心技术为基础,发展出AiDT (auto-interactive delay tune) 、AiPT (auto-interactive phase tune) 、AiBT (auto-interactive breakout technology) 等技术,能让传统的布线设计效率提升超过65%以上,像ODM厂和硕联合(Pegatron)即利用此技术提升设计效能。

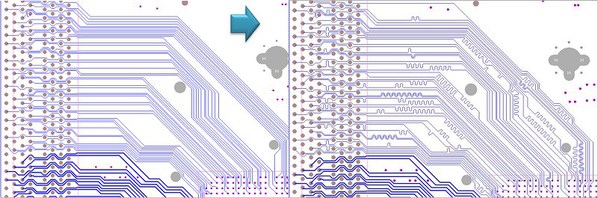

AiDT主要针对并行总线像DDR3/DDR4走线,选定参考频率或strobe讯号长度为依据,在走线长度与间距规范下 (Constraint Management) 自动调整数据/地址/控制讯号与其参考频率或strobe之间的长度关系以符合规范。

| 图二 : 利用AiDT较传统手动怖线调整长度效能至少快50%以上 |

|

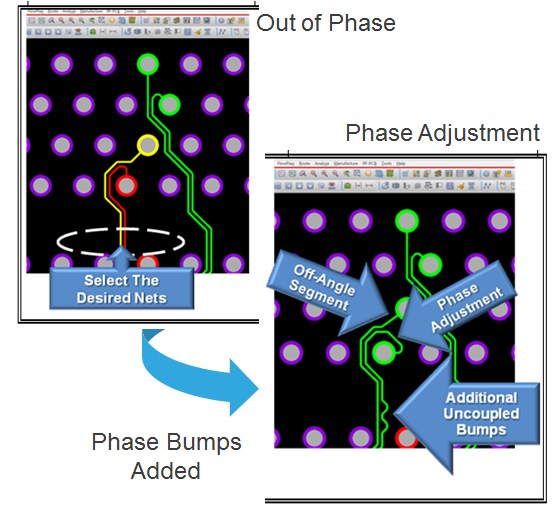

至于AiPT则是针对差动讯号对 (differential-pair) 两讯号间的静态或动态相位调整补偿以减少共模讯号的产生。

| 图三 : 透过用户选择欲调整的差动对进行自动相位补偿调整 |

|

AiBT是针对走线在IC出脚位处,考虑走线规范下在讯号连接的IC两端进行优化处理让走线顺畅不绞线。

在约束走线规范设定(如讯号阻抗要求,走线间距要求等)完成后再加上TimingVision技术即能将设计在第一版就符合要求的目标。最后再将零件与机壳机构图透过Step Model格式输入到Allegro Designer平台以检视机壳与PCB零件机构有否冲突之处,以达到所谓ECAD与MCAD设计整合考虑。

透过MCAD 3D Step Model在Allegro平台内检视,零件与机构干涉问题皆能提早发现。

电源与讯号完整性设计也要前后衔接

物理层级设计完成后,必须对PCB设计做最后签核(Sign-Off)工作,讯号与电源完整性及因电生热问题都必须在此签核阶段分析是否符合芯片正常工作所要求规格。而电源完整性是一切的基础。

传统的电源分析是侧重在严谨的分析芯片端电子漂移 (EM) 及静态与动态IR 压降上。但是,由于所有送往芯片的电力都是从电压源开始,在抵达芯片前至少会先流经PCB及芯片封装,所以许多假设是建立在忽略这两者之上。在更小的几何尺寸及更低的电力需求下,因忽略PCB与芯片封装的影响而引起的失准,可能会造成第一次便告成功与重启芯片设计的巨大差异。

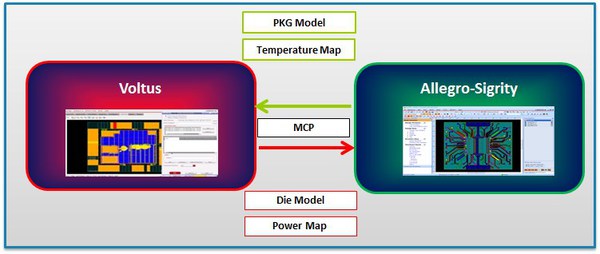

依循「IC-Package-PCB Co-design」的核心思想,Cadence在电源设计方面也是如此,Cadence现在将芯片、芯片封装及印刷电路板的电源整合解决方案合而为一,实现了提高精确度的共同分析解决方案,并且让设计团队可以预先判定芯片、封装体及印刷电路板的电源完整性。 Voltus? IC 电源分析解决方案可以与 Allegro-Sigrity电性协同分析平台链接,满足了整个系统电源与热共同分析解决方案。

| 图七 : 芯片端的电源模型、功耗分布图与封装及PCB端电源模型和温度分布图透过MCP协议来交换数据以达到协同分析的能力 |

|

另外,讯号完整性验证是无法独立于电源考虑,而是一个具有考虑电源效应下的讯号完整性。一般在系统SSO/SSN分析即是IO电源负载最重的情况下是否还能有良好的电源供应以确保讯号的质量。Allegro-Sigrity平台能将芯片、封装到PCB所有模型整合,并将系统电源从VRM,一路从PCB到芯片端,包含了板级电容与芯片电容效应完整考虑。

结论

整体来看,为了克服PCB设计的挑战,Cadence从芯片设计开始,就采取了行动,这也的确与Cadence朝向系统设计前进的作法一致。重点在于,Cadence充分考虑了PCB乃至于整体系统设计所面临的问题与关联性,所以各自在不同的设计环结提供了对应的解决方案,但解决方案之间又能彼此连贯,对于芯片设计甚至是系统整合等工程师们,不仅提供了完善的设计工具,也解决了设计流程之间的沟通问题。