15年前,连接网路最常见的方式是透过类比讯号数据机,经由标准电话语音通道发送资料。由于此技术采用已部署的标准双绞电话线,且无须在最终端的技术做任何更改,加上价格低廉,因此迅速主导通讯市场。就如同所想像的,无须挖路铺线或改变电信局,故使此方式更具吸引力!

数据机的最快速度为56Kbps。为何是56Kbps?为何速度无法再更快?简单来说:这在「理论上」是无法实现的。由于此理论的局限,为ADSL技术发展提供了更多空间。

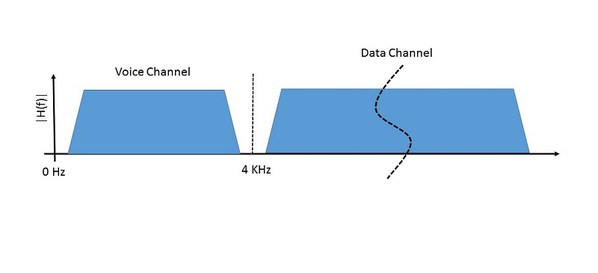

类比讯号数据机使用经ITU-T委员会严格制订的标准化现有语音通道。该通道具频宽限制(4KHz,包含保护频宽,如图1),因此在进入Muldex (多工器/解多工器)前,需在电信局进行硬体滤波。而Muldex则是用来连接电信局与电话的设备。

透过4KHz类比频道传输的最大资料速率为何?此问题的答案便是了解ADSL的关键。

Claude E Shannon于1948年给予正确答案:「取决于通道的杂讯等级」。只要杂讯等级够低,就能以任意的位元速率进行传输。此结果有时会让我们讶异,然而实际上,Shannon更精确地以量化方式,透过给予最大化的通道频宽速率与杂讯等级使其进行相连。

ITU-T规范语音通道的频宽和杂讯等级,并限制双绞电话线实际的最大位元速率;而56Kbps则相当接近通道容量。

ADSL并未使用标准语音通道,而是透过另一种通道,使其打破语音通道的 Shannon限制。

在电话系统中,每位使用者皆透过双绞线连接至电信局,而双绞线的使用时间很短,只在通话时才会用到,并仅占用低于4KHz的通道频宽。

而高于4KHz的频宽显然未被使用。 ADSL使用未被利用的频宽,并将低于4KHz的通道频宽留给标准语音通道,让使用者可在进行电话语音通话的同时交换资料。

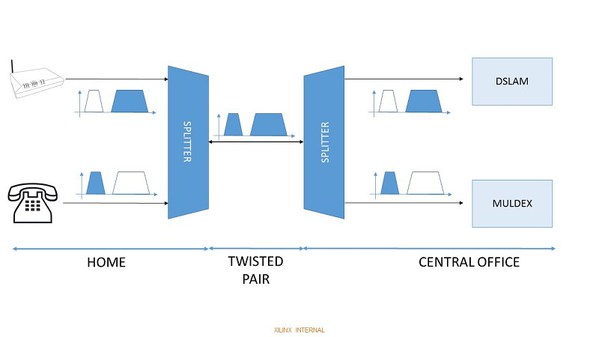

ADSL通道有多宽,杂讯有多大?这方面并未标准化,而这也是为什么每个 ADSL数据机都会在启动时测量线路杂讯,并根据使用者通道状况建立最佳位元速率,如图2所示。

| 图2 : 运用4KHz以上的频宽透过双绞线传输ADSL资料 |

|

每个使用者连接电信局的速度取决于通道本身,而使用者在家可透过ADSL数据机的控制台得知其线路速率。

ADSL是个完美的构想,不仅能善加利用已埋在地下的线路,并在无需对最终端做任何的修改下,使原有的电话还能与新技术相容。使用者仅需在家里安装一个滤波器(即「分歧器」),便能将电话语音频宽与ADSL频宽分离,而此方式更简单且便宜。

电信局中的每条线路亦配有类似的滤波器,其可将语音通道连接到Muldex,并将线路的高频宽部分连接至仅处理资料的新设备上,名为DSLAM(数位用户线路接取多工器)。电信业者只需在每个接近Muldex位置的电信局中建立一个DSLAM,即可提供ADSL服务。

DSLAM是一台具类比前端的纯资料通讯设备,其收集来自广大使用者的所有ADSL资料,而这些资料通常会被送到FPGA进行处理,并汇整至乙太网路中。

| 图3 : ADSL架构可作为以前纯语音网路的「升级」版 |

|

高速乙太网路通常连接到网路或经SDH或OTN传输。 ADSL的标准一直不断演进,而用于连接网路的DSLAM后端连结则根据不同的网路配置而可有多种选择,如乙太网路、XAUI、SDH和OTN等。

这些是使用FPGA的理想条件,因其可建立完全可编程设计的后端连接,并利用可编程设计元件,达到不断演变的ADSL标准。如同赛灵思Vivado设计套件中的IP Catalog进行验证一样,仅需点击按钮即可在赛灵思FPGA中建立几乎所有资料的通讯标准。

ADSL架构看起来如此出色,特别是其可以自然地升级电话网络,但ADSL仍有其局限性,而人们却还想有更多的需求,这也是为什么市场会朝向PON(无源光纤网路)的技术发展。

ADSL的局限由Shannon理论来决定。若透过双绞线让ADSL超过15Mbps是不容易的,这并非为ADSL技术本身的限制,而是从用户到电信局间的平均距离所产生的限制。若想提升速度,便必须改变最终端,并同时降低改变所需的成本。当然,我们可向每位用户提供SDH (乙太网路的传输方式)以满足这些需求,但此方式的价格过于昂贵。而PON则是解决此问题的最佳方案,因该技术能在升级成本、效能及最终端往返成本间取得最佳平衡。

以下为PON的详细工作内容。

电信业者将一条光纤通到距离客户半径几百公尺的「路边」,且并非提供予每位用户一条光纤,而是利用一条光纤来代替数十条的双绞线。透过无源光纤分歧器提供光纤给每位使用家庭,并受加密演算法限制,因此用户仅能使用来自电信局分配属于自己的多点传送资料。

如图4所示,从每位用户的家庭光纤连接到无源分歧器,再被连接到电信局的单条光纤上。而电信局内负责从光纤接收资料的设备称为OLT(光线路终端)。此架构与ADSL截然不同。 PON的优势在于街道上的接线盒是被动式且具光纤功能。 PON技术的关键优势是不含主动元件,因此能协助厂商维护成本降至最低。

此方法的缺点在于电信业者必须将原有的双绞线换成有限数量的光纤。而为了降低更换成本,且不得不降低效能作为代价,因此在许多国家PON多以混合技术的形式搭建。用户透过ADSL连接到路边的接线盒,而从路边到OLT则是透过光学连接。

ADSL可透过采用此混和方案提升速度,原因是DSLAM不在电信局内,而是与用户仅几百公尺的距离。唯一的缺点是,在路边的混和接线盒现在有效是因为安装小型DSLAM。

PON展现出成本与效能间的平衡,然而这并非像先前56Kbps数据机一般,是技术上的最佳解决方案,但PON在未来将可持续发展。

OLT的前端为其另一个关键技术。在上行方向,所有用户都透过被动式光纤分歧器连接至相同的接收器。由于用户共用一条通向OLT的光纤,因此必须进行突波,一次传输一批。所有突波均在相同频率下倚赖用户之阶段进行操作。 OLT接收器在每次突波开始时,会重新同步其传输阶段,以正确接收资料。

每次突波前皆有一个特定模式称之为前导码,其能协助OLT锁定每一次的突波。而OLT的前端接收器则称为「BCDR」(突发式时脉及资料恢复)单元。

增加前导码时间可更容易地设计BCDR,但较长的前导码将明显降低上行频宽的效率。 BCDR是OLT的关键元件,其直接影响PON线路的上行效率,并进而影响PON电信业者的每位元收入。

赛灵思的FPGA技术在OLT中相当普遍,不仅如DSLAM般使用在后端,更可运用于前端。透过赛灵思UltraScale All Programmable元件系列提供最全面的BCDR解决方案。这些解决方案可操作于1.25 Gbps和2.5 Gbps之间。每个UltraScale SerDes埠,包含最低速度等级,皆提供此两种速率,因此,UltraScale元件系列已成为GPON、XGPON 和 NGPON2 OLT的可扩展平台,并具备用于未来设计的附加功能。

具体来说,BCDR采用32位元固定锁定时间以实现高效能上行通讯,其功能超越ITUT G984、G987和G989的规范。此外,BCDR配有操作说明和附件,以协助用户解决以下问题:

如何模拟 BCDR?

对于整合型电信业者而言,首要问题是选择产品。 BCDR只能在PON环境中测试,而PON便是整合型电信业者的产品,但不可能先开发产品,再验证BCDR。若在开发周期结束后才发现BCDR未达预期结果,那么将会出现何种情况?

这是赛灵思推出以BCDR为基础架构的原因。连同BCDR,即可获得一个具有封包产生器和封包检验器的完整模拟测试平台,并用其证明BCDR得以正确运行。

此外,该开发环境不仅能测试BCDR,还能加压于它,并发掘其终极效能。下述为一些实例:

‧ 产生多个ONU

‧ 可强制让ONU运行于「锤子」模式,使封包至封包的阶段始终维持0.5%的UI,以确保BCDR完全不受波动的影响。

‧ 当多帧封包重启时,锤子模式下产生的所有封包皆需移动1微微秒,以确保BCDR阶段检验器没有死角,而锁定时间则始终维持短且明确的32位元。

‧ 可于0-8K+间更改封包的前导码长度,如此将能同时满足最严格的ITU.T PON和较宽松的IEEE PON要求。

图5描述XAPP1277 中与BCDR搭配所提供的模拟环境架构。

该模拟环境需透过脚本运行。无需编写任一行代码,即可在数分钟后看到波形。该环境主要提供予想选择特定产品,但尚未整合该产品的客户。

对于硬体厂商而言,软体压力测试架构便是一个非常好的起点。然而,需看到硬体在作业时,这正是第二个BCDR架构的工作;该架构使用Kintex UltraScale FPGA的KCU1250描述性套件。该架构在硬体中不断生成并检验封包,以避免任何错误或丢失任何封包。

如何使用Demo卡模拟PON环境?如何用1个BCDR进行锤子模式测试?

上行资料总以双倍速率合成,而TX串列器总在每个上行位元产生两个同样的位元。如此,在架构层面,硬体架构可在任两个连续封包之间,模拟一个0.5UI差别,此亦为PON环境中最差的情况。硬体架构透过在任意两个封包之间,插入一个最差情况,以对BCDR施压。

该架构中的负载量是被截短的PRBS,其于每个封包的定义后重新开始。若BCDR跳过任何一个封包,将会在负载量上产生错误。

同时亦可在运行中更改前导码长度。

整个硬体测试平台可支援脚本编写,并将Vivado硬体分析器内建其中,使其具备一套完整的控制功能,如图6所示:

除了锤子模式测试、错误馈入和累积外,亦可在运行中更改很多SerDes和BCDR特性,例如数位频宽等。

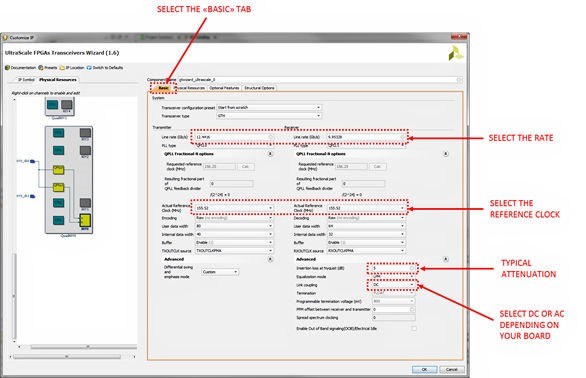

对不熟悉FPGA技术的使用者来说,SerDes配置则是另一个会让使用者感到困惑的地方。因此BCDR架构提供了使用说明,一步步介绍如何配置SerDes,并说明用户要如何设置PON OLT介面。图7显示「GT(GT收发器)向导 GUI」示意图,展示架构如何指导配置,以及如何避免硬体复杂性:

| 图7 : 用于设置多速率OLT介面的SerDes配置。 |

|

这些技术让使用者仅需透过GUI便能选择如BCDR般复杂的产品。原则上,即使不了解基础技术细节也能做这些工作。

一旦对BCDR完成评估,硬体测试平台将成为启动实际项目的最佳起点。仅需删除Demo封包的产生器/检验器,并用真实的PON MAC替代这些模组,即可嵌入BCDR。

(本文作者Paolo Novellini、Antonello Di Fresco任职于Xilinx赛灵思公司)