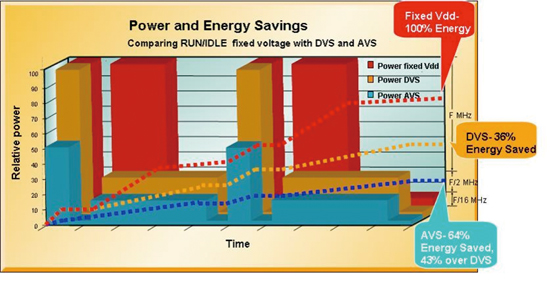

調整可攜式電子裝置處理器的電壓和頻率的作法已變得相當普遍。由於可攜式裝置的功能愈來愈多,因此要求處理器具有更高資料處理效率。透過閉迴路(closed loop)方法,自適性電壓定比(Adaptive Voltage Scaling , AVS)可以在一個既定處理器頻率下提供最低的操作電壓。在調整處理器性能方面,AVS迴路能夠自動調整電源的輸出電壓,以便為處理器的溫度變化作出補償。此外,AVS迴路還可以降低電源的容限。與開放迴路式的電壓調整技術如動態電壓調整(Dynamic Voltage Scaling , DVS)等相較之下,AVS可多節省45%的用電。

| 《圖一 比較固定電壓、DVS和AVS在節省處理器用電上的能力》 |

|

系統級自動電壓調整

AVS是一個系統級的方案,它的元件同時分布在處理器和電源兩個部份。當中,安置在處理器上的先進功率控制器(Advanced Power Controller , APC)負責提供AVS迴路控制,而安置在電源一方的從屬功率控制器(Slave Power Controller , SPC)則負責處理從APC來的指令。在APC和SPC中提供的IP會自動地處理牽涉在頻率和電壓調整的訊號交換,進而簡化了設備的系統整合度。

AVS採用一種創新的閉迴路方法來調整電壓,當中AVS迴路圍繞著處理器的性能被封閉,消除了所有多餘的電壓裕餘(Voltage Margin)。這與以表列為基礎(table based)的DVS系統剛好相反,因為DVS必須包括額外的電壓裕餘。此外,AVS迴路由於可以真正感測到負載中的電壓,因此可以為穩壓器的回饋提供一個優秀的凱氏檢測(Kelvin sensing)連接,從而消除了因電源和處理器間的接地差而導致的電壓誤差。正如前面所述,AVS迴路能夠自動縮窄電源的容限,使裕餘電壓進一步減少。所有這些出現在供電電壓上的節約都可將處理器的用電量大幅減少,原因是動態能源的消耗是與電壓的平方成比例。

AVS系統迴路架構

圖二所示為系統中的主要區塊,當中由美國國家半導體授權使用的先進功率控制器(APC)為系統提供AVS迴路控制和所有電壓/頻率調整的訊號交換處理。圖中的PowerWise介面(PWI)是一個開放的標準介面,這個兩線的串列介面能為AVS提供所需的頻寬和協定。最後,能量管理單元(Energy Management Unit , EMU)則負責電壓調整和穩壓。

可適性功率控制器能夠處理各方面的電壓控制,而且可以有效地降低主控制器的功耗。它是以可合成的RTL實現並具備有以下的功能組件:

- ●硬體性能監視器(Hardware Performance Monitor , HPM)

- ●數位迴路濾波器和

- ●PowerWise介面(PWI)主模組

這些元件一起發揮作用時,能夠為外部的電源執行簡單和準確的電壓控制。

應用在AVS的硬體性能監視器(HPM)和數位迴路濾波器的工作是根據既定的性能要求對數位電路的性能進行測量,而從HPM量度出來的資料會先交由數位迴路濾波器處理,之後再送到PWI主模組並向電源發出一個電壓請求。

在閉迴路AVS系統中,同時存在著連續時間(電源)和離散時間(HPM和離散補償)的成份,因此可以採用取樣資料原理來替系統進行分析。HPM輸出一個數位訊號字,而輸入則同時包括要求性能(運算時脈)和類比電壓。這個數位訊號字是矽片性能的一個相對性測量。取樣資料控制迴路會嘗試根據參考輸入來調整這個量度出來的輸出,而這個參考亦是一個數位訊號字(digital word)。迴路的穩定性將會取決於離散時間的補償,而這方面可以有幾個方法來實現。

設計實現之方法

透過將SoC的設計分割成若干獨立的電壓域,便能夠進一步加強節能的效果。例如,處理器的核心和硬體加速器可以在不同的調整電壓域下工作。APC 2.0可促使控制多個AVS域,而這種功能在現今尖端的SoC設計中是很普遍。透過PWI 2.0介面,APC 2.0最多可以容納16個從屬AVS域。

PWI是一個開放式的標準介面,它可容許串列資料通過SCLK和SDAT接腳進行傳輸。高至15MHz的資料傳輸率可滿足閉迴路AVS在頻寬上的要求,而這個頻寬是必須的,而且介面亦必須能確保可以提供,以免迴路在工作時不會出現太多的落後。

AVS迴路的最後一個組成部份是能量管理單元(EMU)。EMU能夠為處理器核心提供穩定的電壓調整和穩壓作用,以及比如是支援PLL和邏輯電源等的電壓。為了在AVS迴路內工作,EMU必須包含有從屬功率控制器(SPC),以便解譯PWI的指令。EMU的規格可以影響AVS迴路的性能,並且一如PWI必須能提供足夠的頻寬一樣,EMU亦必須符合頻寬上的要求。

AVS不單可大大節約能源,而且還可簡化系統的整合度。對於處理器來說,AVS迴路能夠自動地操作,除了少數的一次性配置設定外,期間無需任何的軟體協助。此外, APC具備有一個電壓監視器,它的工作是監視電壓直至它到達既定工作頻率所需的適當電平,從而簡化了出現在電壓和頻率調整間的訊號交換過程。

協調工作頻率與電壓

對頻率和電壓調整進行檢討可有助理解AVS的優點。基本的概念是將頻率按處理器的工作量要求而調整,然後再將電壓調整到可以在該電流頻率下工作的最低要求。這種做法的好處是使到既定處理(以處理器的週期次數作量度單位)所需的動態(開關)能量能與供電電壓的平方成比例。例如,無論工作頻率是多少,在1.2V下的100個時鐘週期所需要的能量會大於在0.9V下的100個週期。對於任何的頻率/電壓調系統來說,都會有兩種轉變出現,分別是上升和下降頻率/電壓的調整事件。

一個上升頻率/電壓調整事件是由工作量監視器發出的更高工作頻率要求而觸發。為了支援這個較高的工作頻率,系統必須首先透過某種方法(AVS和DVS是兩個例子)來提升供電電壓,一旦電壓到達要求的水平後,即較高電壓時,系統便會占用較高的時鐘頻率來工作。

同樣地,一個下降頻率/電壓調整事件是由一個較低工作頻率要求而觸發。可是,在這個情形下,供電電壓的大小已經足以支援較低頻率的工作,因此工作時鐘可以即時下降。現在,系統降低了供電電壓以配合新的和較低的工作頻率。下降與上升頻率/電壓調整事件的最主要分別是出現在供電電壓暫態中的任何欠壓 (undershoot)都必須計算在內,亦作為系統的額外裕餘(extra margin)(圖三)。因此,最好還是把欠壓消除。

設定配置AVS迴路系統

AVS系統之所以能達到準確和可控制的電壓調整,全賴將一個可配置的回饋迴路與電源一起使用。透過改變參考電壓,便可改變某特定工作頻率下的電壓裕餘。假如改變迴路的增益,就可改變電壓調整事件的迴轉率。AVS迴路甚至可以區分上升和下降電壓調整事件,因此不同的增益以至不同的迴轉率會被使用,這樣在下降轉變時便可將欠壓減到最小,而在上升轉變時則可把上升的時間減到最小。正如以上所述,減少欠壓量便可直接降低供電電壓和用電量。對於這種以及其他的靈活性,APC都可提供。

AVS迴路是一個真正的閉迴路系統,它們只有幾個參數需要配置。正如所有的回饋系統一樣,迴路必須獲得補償才能提供穩定的回應。APC具備可以設定迴路增益的暫存器,而增益的大小必須適中,它必須夠大才能提供足夠的上升和下降時間,但同時卻要夠低以確保過阻尼響應(overdamped response)(沒有過壓或欠壓)。此方面的設定其實可透過一些練習來完成,因為其只會影響到迴路的增益,而且可以在實驗室進行又或透過ACP IP檔提供的數式來計算。

除了迴路的增益需要設定外,參考亦必須被設定。AVS迴路的參考是一個數位訊號字,它對應於與由HPM量度出來的處理器性能要求。實質上,它就像是調整設置時間規格中的延遲裕餘(delay margin)。由於迴路是直接對處理器的性能作出調整,因此任何所需的裕餘量都可透過編程來獲得,這便可為不同的設計要求提供高度靈活性。透過設定AVS迴路的增益和參考,迴路便可自動處理電壓的調整。

APC的另一重要功能是電壓監視器。電壓監視器可為每一個電壓調整事件提供一個 「功率優良」 的標籤訊號,從而大大簡化了電壓和頻率的調整過程。當系統要調高電壓和頻率時,這項功能便顯得尤其重要。然而,新的較高頻率不會被採用直至電壓上升到可以以支援較短的延遲時間。一旦電壓上升到新的水平,電壓監視器便可即時允許處理器轉換到新的較高時鐘頻率。這樣不單可使系統運行得更快,而且無需設定電源的上升和下降時間(它們會隨元件的容限而變化)。

由於已經知道電壓轉變所需的正確時間,因此電壓監視器可促使系統以較快的速度來調整電壓,而同樣地亦可使系統的頻率調整速度較快,而由於花在調整到較高電壓上的時間較少,因此可提升系統的效能。

結語

AVS系統可以為一個給定的處理器提供最佳的電壓調整方案。配合閉迴路調整的優點,系統可在既定的工作條件下選擇最低的電壓來工作。迴路的增益可以同時配合上升和下降電壓調整事件來配置,從而進一步減少欠壓所需的裕餘。此外,APC內的電壓監視器可為系統提供一個電壓已到達新水平的提示,大大降低了系統的集成複雜度。整體來說,AVS系統可為電壓調整和頻率調整之間提供一個自動的訊號交接。透過閉迴路控制和可配置的增益,系統便能達到最佳的節能效果。

(作者Mark Hartman任職於NS美國國家半導體)