隨著FPGA元件尺寸的增加和內部設計密度提升的需求,時序收斂面臨前所未有的挑戰。由於各種建置工具難以跟上日益複雜的FPGA元件設計,這也讓完成不同設計建置所需的時間越來越長[1]。為了加快完成設計案的速度,有些設計人員正採用雲端運算的方法,比較和分析不同建置選項和使用者規範決策帶來的影響。

最近,我們在南非的科學及產業研究協會(CSIR)完成了這樣的一個分析過程。我們採用Plunify公司的雲端加速晶片設計方法,為我們的設計找到了既可提供最快完成建置的時間,而且可得到最佳時序評分的各項參數。在深入探討更多分析細節及所使用的工具前,讓我們先瞭解一些背景。

開發板升級

在最近一個專案中,我們需要將負責處理作業的Xilinx Virtex-5 FPGA更換成新一代Virtex-6元件以便升級現有的開發板。第一塊開發板出現了幾個問題,其中最嚴重的是目標應用所需的引腳(pinout)並不理想,而且元件尺寸過小,不能滿足系統需求。

當時已有大部分可運作新型開發板所需的RTL程式碼,可以說是佔有絕對優勢,因為這樣可分析在PCB電路圖設計的引腳分配階段所作的決策。由於FPGA設計的建置作業需要較長的時間,因此必須限制PCB設計階段中所執行的建構次數,以作出最終決策。

在設計硬體測試的階段中,我們增加了一些原來Virtex-5開發板沒有的功能。不出所料,這為佈局和佈線工具增加更多工作,因此我們進行了詳細的佈局規劃,同時也執行了多次運作,目的是要找到最佳種子佈局(placement seed)。最後我們決定採用Plunify公司的雲端建置服務來管理我們所需的大量執行作業。

四個約束集

由於採用的是Plunify服務所提供的處理效能,所以我們決定運用四個不同的約束集來分析最終設計。前兩個約束集共用相同的引腳,其中第一個約束集沒有佈局規劃,而第二個則有一個詳細的佈局規劃。在這兩個約束集中選擇的引腳是要複製我們在第一版開發板上所遇到引腳分配不當造成的問題;而另外兩個約束集則共用新版開發板上元件的引腳,並採用同樣的做法——其中一個約束集沒有佈局規劃,而另一個則有詳細的佈局規劃。

我們藉由這四種約束集來驗證FPGA 引腳的改變是否會影響時序收斂的結果,以及單在第一版開發板上改變種子佈局是否不足以達到時序規範要求。每個約束集執行100次建構,而且在1-100次中採用不同的種子佈局。

採用工具

在FPGA設計軟體方面,我們採用Xilinx ISE設計套件邏輯版本14.4來完成設計人員在現有工作流程中的各項任務,並在雲端的環境完成合成和佈局佈線任務。

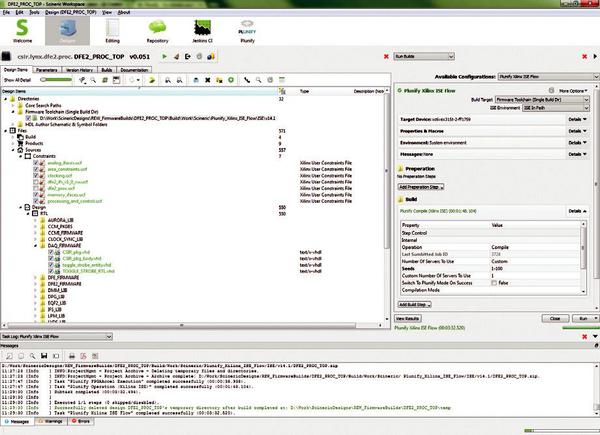

在前端,CSIR 的 Scineric Workspace(圖一)以IP-XACT為基礎,而且是一個快速的輕量級全新整合式開發環境,適用於FPGA設計管理。該工具採用全新「檔案管理員」方法來進行設計管理,有助設計人員隨時全面掌握設計的每個面向,而其多項設計融合功能可將Scineric整合到現有,而且使用者已設定偏好特定設計環境的工作流程中。

我們可使用Scineric Workspace圖形介面載入ISE專案並在雲端進行配置、提交和檢索建構。然而,這個前端作業並非硬性要求,Plunify用戶端也可順暢地將Scineric Workspace整合到ISE和Vivado工作流程中。

| 圖一 : 將專案上傳後的Scineric Workspace畫面 |

|

在後端,Plunify的FPGAAccel用戶端是一個軟體API,工程師們可通過它在遠端伺服器上同時定義、分配和執行FPGA綜合以及佈局佈線建構,並在完成所有建構後對結果進行分析。在這個例子中,我們採用一個雲端運算伺服器群(server farm)執行400次建構的處理作業。 Scineric Workspace支援包括FPGAAccel用戶端在內的多種配置。

圖二顯示了設計人員在工作中如何使用這些工具,其具體流程如下:

- 1. 開啟Scineric Workspace;

- 2. 匯入ISE專案;

- 3. 為每個ISE專案設定100次實驗。

- 4. 上傳建構需求

- 5. 建構完成後,您會收到一封電子郵件通知。

- 6. 用您的工作ID登入到http://www.plunify.com查看報告。

- 7. 對各個ISE專案重複以上步驟。

Scineric Workspace可讓用戶從賽靈思ISE和Vivado專案以及IP-XACT元件定義檔等多種來源里匯入設計。每個設計都可以有不多種建構配置,可讓設計人員設定 Plunify實驗定義,並可隨後上傳至Plunify。

Plunify 的外掛程式首先會對設計人員的身份進行認證,然後才會將ISE專案中的所有設計檔進行加密。接下來,才會用安全的方法一起將檔案與建構參數傳輸至遠端伺服器群。Plunify軟體會在雲端產生所需的建構,分配400台伺服器並運行ISE,以在每台伺服器上為各個不同的實驗進行綜合與佈局佈線。

同時完成400次建構

我們將這400次建構的結果用於多個標準測試,包括平均執行時間、不可佈線的解決方案數量,以及最重要的可佈線解決方案的時序評分。圖三顯示了四個約束集的時序評分分析結果。

我們透過四個約束集可再次證明目標應用的無效引腳會嚴重影響設計的時序評分。另外,我們可為該設計確定最佳的種子佈局,並在這個特定案例中,我們了解到建置工具在不受佈局規劃引導的情況下能有最佳的表現。圖四顯示了四個約束集的執行時間。

從前,這樣的作業需要30多天才能完成,但透過我們所說的方法,只需一天便能得到結果和分析。這個方法的另一個優點是全部資料都能由Plunify管理,這是當我們進行400次運作後從所產生(200千百萬位元組)資料後才發現的。我們只需要下載感興趣的特定執行作業的結果。

最佳時序評分

時序收斂在任何FPGA設計中都是重要的一環,而我們已經證明有很多參數都會對時序評分產生影響。藉由全新的工具和雲端運算技術,我們可以比以往更快速地分析這些影響。我們能夠明確了解哪種約束集和種子佈局能為設計帶來最佳的時序評分。透過使用最佳參數,我們可以了解執行中的建構能否達到其時序要求以繼續下一階段的系統開發。

(作者J.P. Naude為科學及產業研究協會(CSIR)硬體與FPGA設計師;Harnhua Ng為Plunify公司工程研發主管)