东芝(Toshiba)公司成功研发出一款适用于类比功率半导体应用的静电放电(ESD)保护装置,产品采用先进的0.13μm制程技术制造,最佳化了电晶体结构,显著提高了静电放电特性。静电放电保护稳固性提高多达四倍,标准差仅为传统结构的十二分之一。 3D模拟分析也有助于东芝发现一种机制,最佳化电晶体结构,提高静电放电稳固性。东芝在2016年6月14日于捷克举行的国际半导体研讨会ISPSD2016上公布了这些创新成果。

|

| 新款静电放电保护装置平台嵌入CMOS、DMOS、双极型电晶体等电晶体及电阻器和电容器等被动元件。 (Graphic: Business Wire) |

注入来自人体或设备的静电放电电涌,有可能毁坏半导体元件,因为静电放电电流引起矽材内局部温度上升。需要静电放电保护元件来保护内部电路。这对需要施加 10V-100V电压的类比功率半导体元件来说尤为重要,这些半导体元件需要高额定电压。在这种情况下,静电放电保护装置必须确保大电流,进而导致晶片尺寸增大。缩小静电放电保护装置尺寸成为让晶片更为紧凑的一个问题。

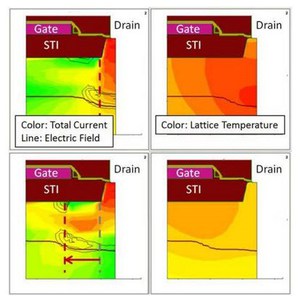

透过静电放电事件3D模拟分析,东芝发现,流经最高电场点的电流导致晶格温度上升,进而导致静电放电诱发的破坏。修改电晶体结构,将漏极低电阻区延伸向源 极方向并抑制横向矽电阻,将来自漏极底部的电流转移向源极方向并从最高电场点将其分离。经发现,这一最佳化设计使静电放电稳固性提高多达四倍,而标准差减少到十二分之一。此外,该装置确保HBM +/-2000V(注)所需的尺寸减少了68%。

东芝利用0.13μm制程技术,提供先进的类比流程平台,可在该平台嵌入CMOS、DMOS、双极型电晶体等电晶体以及电阻器和电容器等被动元件。使用者可从以下三个流程平台中选择适用于每个应用的制程:BiCD-0.13主要用于汽车(DMOS最高可达100V);CD-0.13BL主要用于马达控制驱动器(DMOS最高可达60V )以及CD-0.13制程主要用于电源管理IC(DMOS最高可达40V)。

东芝计画于2017年推出采用CD-0.13制程技术的产品并继续积极将该制程技术推广至其他流程平台,以提高静电放电特性。

注:HBM(人体模型):指示静电放电稳固性的参数之一