随着设计规模变得越来越大,功能越来越多,复杂性也在持续呈爆炸式增加。对於整个设计和验证团队而言,无论是在时间、工作量和经费上,运作的成本都呈现指数性增长。

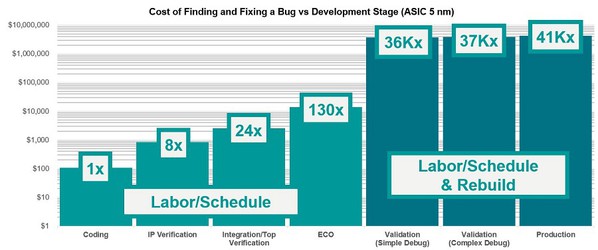

| 图一 : 若未能尽早发现问题,就需要花更多精力来寻找并修复问题。(source:Wilson Research Group and Siemens EDA, 2020 Functional Verification Study) |

|

造成预算超出和计划延迟的一个重要原因是设计错误,而这些错误原本是可以在设计过程中修正的,且不需要用到精密复杂的验证程式,也不必具备深奥难懂的验证技术知识。但是,如果这些错误转给验证和整合团队时,会导致设计流程停顿下来,迫使验证工程师将有错误的区块送回至设计工程部门。

解决此问题的最隹方式是,在区块和子区块设计期间从源头修正错误。要做到这点,设计师必须改变他们看待并处理验证和除错的方式,并且需要工具来帮助他们将合理品质的产品尽快地交给验证团队,让验证工程师能够调教区块并予以整合。

错误造成的麻烦

在一份《 Wilson Research Group 功能验证研究》中,设计错误被认为是造成 ASIC 和 FPGA 重新设计的一个主要原因。在这些错误当中,有许多类型都可以很容易由「以设计师为中心」的解决方案所捕捉。此调查还显示,除错是最消耗时间的一环;从逻辑上讲,除错时间的长短取决於错误的数量。

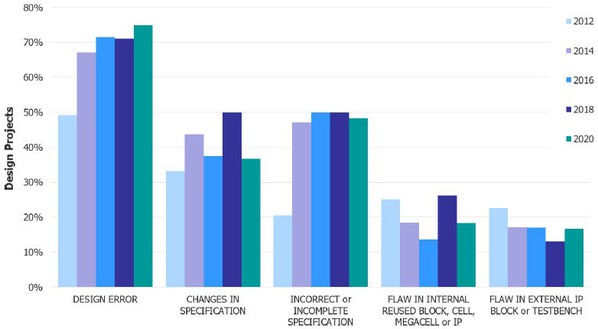

| 图二 : 设计错误仍然是导致功能缺陷的主要原因。(source:Wilson Research Group and Siemens EDA, 2020 Functional Verification Study) |

|

电路设计错误的爆量增加只会带来越来越多的麻烦。这取决於我们熟悉的电子设计演进??产品,亦即逐渐增加的复杂性。不只是设计变得规模更大、更拥挤和密集,设计团队也大幅扩充,设计中的区块也越来越多。随着设计和设计团队的规模扩大,设计阶段的错误,如滚雪球般地从设计阶段进入验证和整合阶段。

在问题还没那麽复杂的时候,设计团队有能力承担成本并找到暂时的解决方法,使验证工作继续向前推进。一些设计师的思维模式是尽快完成设计工作,并将工作成果传给验证团队。他们并不关心覆盖率是否达到 100%,只想确保结果符合规格。但是,我们都知道,即使程式码符合规格,一定还有那些隐藏在 RTL 远处角落、不易被察觉到的错误。

当验证小组发现电路设计错误时,他们必须耗费很多时间自行除错或者将设计送回设计者。在这两种情况下,都会不可避免地对晶片 tapeout 时间和设计品质造成高昂的代价。正如我们前面所看到的,Wilson 调查结果显示,这些成本正急剧增加,并导致整个设计和验证流程都受到拖累。

解决方法的第一步是改变设计工程师的思维和工作方式。设计师需要藉助相关工具,帮助他们在能够很容易以低成本快速解决错误的设计早期阶段,修复这些错误。在编写程式码时找到错误,会节省许多成本。为了使此策略有效,这些工具必须容易设定,不需要验证专业知识,并且设计师必须能够以最轻松的方式使用这些工具。

在初步阶段找出错误

然而,我们目前却看到有很多的错误都是在流程的後期被发现,源於作为一个产业,我们仍缺乏合适的工具,特别是针对设计阶段的工具。目前市场上有很多出色的验证工具,但传统上,CDC、RDC 和其他功能验证工具并不是专门为设计师所打造。Linting 属於例外情形,但没有人将这些所有技术结合在一起。因此,在为设计师打造的共同环境和方法论中,有必要将所有的这些技术整合。

工作团队不应等待验证程式,而是应该从源头消除设计错误,因为在验证前修复错误能够提高一致性、效率和可预测性。

| 图三 : Questa 设计解决方案可产生建造时即正确的设计,证明设计符合设计师意图,并在整个开发过程中保护设计。 |

|

针对此需求,西门子EDA 推出一系列以设计师中心的技术。Questa 设计解决方案是一组专为设计工程师打造的验证工具,提供了一个易於使用的平台,其中包含一个可继续在验证中使用的共用资料库,并且提供验证所作假设的能力。这些以设计为中心的技术,会在实际发生错误时告诉设计师,让设计师不必在验证程式设定上消耗许多时间。现在,设计师可以确保进入验证的设计具有足够好的品质,因此验证团队可以快速上手完成验证工作。

Questa 设计解决方案的重点在於让设计师获得所需资料,不但能确保设计良好,而且能让设计师将设计与验证之间的交接标准化。方案的最终想法是建立正确的设计,并确保设计之後在开发周期中移动时,能够保持正常运作。Questa 设计解决方案可确保资讯会被??送到验证中。

Questa 设计解决方案还可帮助设计师在很容易修复错误的设计阶段找出错误。如果设计师可以在设计当中捕捉到错误,就不必在模拟中将它们找出并予以修复。这不仅可以节省时间和精力,而且还提高了设计品质。如果我们能以更高的品质加快验证调教的速度,验证工程师就能拥有更多时间的专注於功能与覆盖率验证。

对於想要及早发现错误的设计师,Questa 设计解决方案可以为其带来新的思维方式。此方案可为设计师提供一组工具,使用一致的 UI 和一致的资料库,将设计师的假设标准化,并将该设计知识推送给验证团队。这将引导验证团队使用该资料,让验证更早启动和执行,从而使整体工作更高效。

(本文作者Neil Hand为西门子EDA IC验证解决方案策略总监)