隨著設計規模變得越來越大,功能越來越多,複雜性也在持續呈爆炸式增加。對於整個設計和驗證團隊而言,無論是在時間、工作量和經費上,運作的成本都呈現指數性增長。

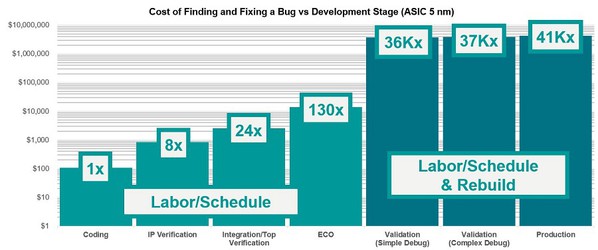

| 圖一 : 若未能儘早發現問題,就需要花更多精力來尋找並修復問題。(source:Wilson Research Group and Siemens EDA, 2020 Functional Verification Study) |

|

造成預算超出和計劃延遲的一個重要原因是設計錯誤,而這些錯誤原本是可以在設計過程中修正的,且不需要用到精密複雜的驗證程式,也不必具備深奧難懂的驗證技術知識。但是,如果這些錯誤轉給驗證和整合團隊時,會導致設計流程停頓下來,迫使驗證工程師將有錯誤的區塊送回至設計工程部門。

解決此問題的最佳方式是,在區塊和子區塊設計期間從源頭修正錯誤。要做到這點,設計師必須改變他們看待並處理驗證和除錯的方式,並且需要工具來幫助他們將合理品質的產品儘快地交給驗證團隊,讓驗證工程師能夠調教區塊並予以整合。

錯誤造成的麻煩

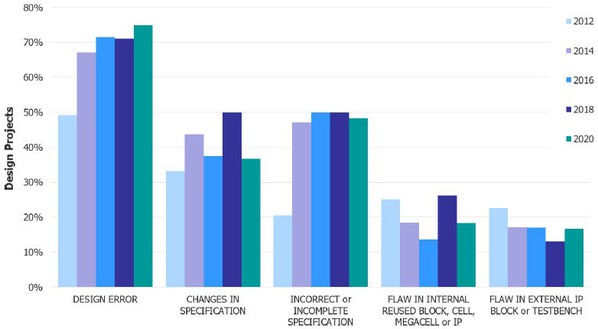

在一份《 Wilson Research Group 功能驗證研究》中,設計錯誤被認為是造成 ASIC 和 FPGA 重新設計的一個主要原因。在這些錯誤當中,有許多類型都可以很容易由「以設計師為中心」的解決方案所捕捉。此調查還顯示,除錯是最消耗時間的一環;從邏輯上講,除錯時間的長短取決於錯誤的數量。

| 圖二 : 設計錯誤仍然是導致功能缺陷的主要原因。(source:Wilson Research Group and Siemens EDA, 2020 Functional Verification Study) |

|

電路設計錯誤的爆量增加只會帶來越來越多的麻煩。這取決於我們熟悉的電子設計演進副產品,亦即逐漸增加的複雜性。不只是設計變得規模更大、更擁擠和密集,設計團隊也大幅擴充,設計中的區塊也越來越多。隨著設計和設計團隊的規模擴大,設計階段的錯誤,如滾雪球般地從設計階段進入驗證和整合階段。

在問題還沒那麼複雜的時候,設計團隊有能力承擔成本並找到暫時的解決方法,使驗證工作繼續向前推進。一些設計師的思維模式是儘快完成設計工作,並將工作成果傳給驗證團隊。他們並不關心覆蓋率是否達到 100%,只想確保結果符合規格。但是,我們都知道,即使程式碼符合規格,一定還有那些隱藏在 RTL 遠處角落、不易被察覺到的錯誤。

當驗證小組發現電路設計錯誤時,他們必須耗費很多時間自行除錯或者將設計送回設計者。在這兩種情況下,都會不可避免地對晶片 tapeout 時間和設計品質造成高昂的代價。正如我們前面所看到的,Wilson 調查結果顯示,這些成本正急劇增加,並導致整個設計和驗證流程都受到拖累。

解決方法的第一步是改變設計工程師的思維和工作方式。設計師需要藉助相關工具,幫助他們在能夠很容易以低成本快速解決錯誤的設計早期階段,修復這些錯誤。在編寫程式碼時找到錯誤,會節省許多成本。為了使此策略有效,這些工具必須容易設定,不需要驗證專業知識,並且設計師必須能夠以最輕鬆的方式使用這些工具。

在初步階段找出錯誤

然而,我們目前卻看到有很多的錯誤都是在流程的後期被發現,源於作為一個產業,我們仍缺乏合適的工具,特別是針對設計階段的工具。目前市場上有很多出色的驗證工具,但傳統上,CDC、RDC 和其他功能驗證工具並不是專門為設計師所打造。Linting 屬於例外情形,但沒有人將這些所有技術結合在一起。因此,在為設計師打造的共同環境和方法論中,有必要將所有的這些技術整合。

工作團隊不應等待驗證程式,而是應該從源頭消除設計錯誤,因為在驗證前修復錯誤能夠提高一致性、效率和可預測性。

| 圖三 : Questa 設計解決方案可產生建造時即正確的設計,證明設計符合設計師意圖,並在整個開發過程中保護設計。 |

|

針對此需求,西門子EDA 推出一系列以設計師中心的技術。Questa 設計解決方案是一組專為設計工程師打造的驗證工具,提供了一個易於使用的平台,其中包含一個可繼續在驗證中使用的共用資料庫,並且提供驗證所作假設的能力。這些以設計為中心的技術,會在實際發生錯誤時告訴設計師,讓設計師不必在驗證程式設定上消耗許多時間。現在,設計師可以確保進入驗證的設計具有足夠好的品質,因此驗證團隊可以快速上手完成驗證工作。

Questa 設計解決方案的重點在於讓設計師獲得所需資料,不但能確保設計良好,而且能讓設計師將設計與驗證之間的交接標準化。方案的最終想法是建立正確的設計,並確保設計之後在開發週期中移動時,能夠保持正常運作。Questa 設計解決方案可確保資訊會被饋送到驗證中。

Questa 設計解決方案還可幫助設計師在很容易修復錯誤的設計階段找出錯誤。如果設計師可以在設計當中捕捉到錯誤,就不必在模擬中將它們找出並予以修復。這不僅可以節省時間和精力,而且還提高了設計品質。如果我們能以更高的品質加快驗證調教的速度,驗證工程師就能擁有更多時間的專注於功能與覆蓋率驗證。

對於想要及早發現錯誤的設計師,Questa 設計解決方案可以為其帶來新的思維方式。此方案可為設計師提供一組工具,使用一致的 UI 和一致的資料庫,將設計師的假設標準化,並將該設計知識推送給驗證團隊。這將引導驗證團隊使用該資料,讓驗證更早啟動和執行,從而使整體工作更高效。

(本文作者Neil Hand為西門子EDA IC驗證解決方案策略總監)