本文詳細探討如何使用比較器來實現電路保護中的欠壓/過壓閉鎖,並利用電阻分壓器調整電源欠壓和過壓閉鎖閾值,同時透過導入遲滯設計來提高整個電路抗雜訊能力。

在電子設備的實際應用中,可能會遇到輸入電壓不穩的情況。例如使用電池的可攜式設備應用,輸入電壓Vin可能很難保持非常穩定。為了防止電壓過低或過高影響後續電路,有時有必要增加欠壓/過壓閉鎖設計。

欠壓閉鎖(UVLO)/過壓閉鎖(OVLO)兩個概念的定義如下:

‧ 欠壓閉鎖(UVLO):輸入電壓達到某一閾值,後續電路導通,可防止下游電子系統在異常低的電源電壓下工作。

‧ 過壓閉鎖(OVLO):輸入電壓超過某一閾值,後續電路斷開,可保護系統免受極高電源電壓的影響。

本文探討如何使用比較器來實現欠壓/過壓閉鎖,並利用電阻分壓器調整電源欠壓和過壓閉鎖閾值,同時透過導入遲滯設計來提高整個電路抗雜訊能力。

欠壓閉鎖(UVLO)電路設計

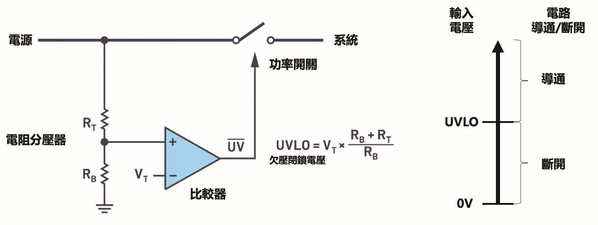

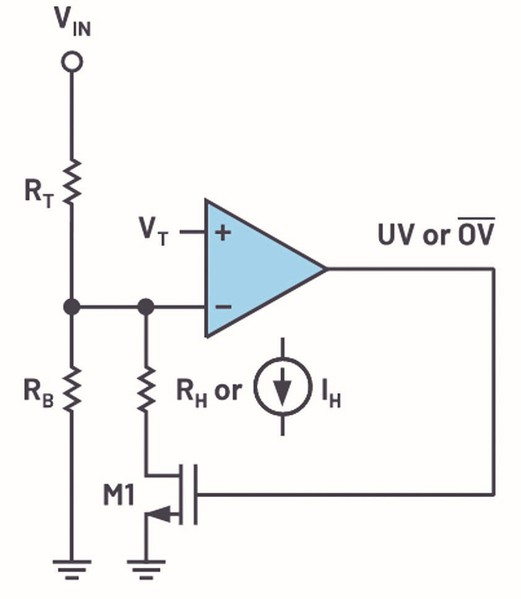

如圖1所示,為了實現欠壓閉鎖(UVLO)電路設計,我們需要:

‧ 一個比較器

‧ 一個基準電源VT

‧ 一個功率開關(比如MOS電晶體)

‧ 分壓電阻,用來調節閾值

‧

| 圖1 : 電阻分壓設計中的欠壓閉鎖電路(source:ADI) |

|

當輸入電壓從0 V開始上升到UVLO閾值電壓之前,功率開關保持斷開狀態;超過UVLO閾值電壓,功率開關導通,整個電路正常工作。

欠壓閉鎖(UVLO)+ 過壓閉鎖(OVLO)電路設計

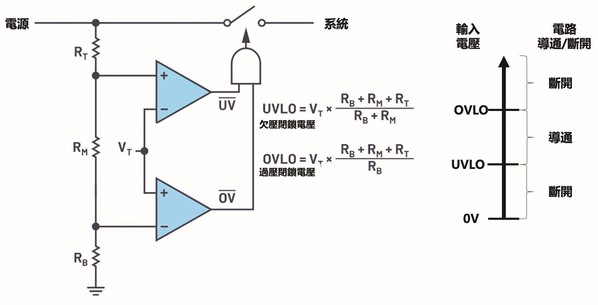

與使用兩個電阻串聯相比,三個電阻串聯可設置欠壓和過壓閉鎖閾值。

| 圖2 : 欠壓閉鎖(UVLO) + 過壓閉鎖(OVLO)電路設計(source:ADI) |

|

如圖2所示,兩個比較器輸出連接到邏輯及閘,邏輯及閘再連接功率開關。

當輸入電壓從0V到UVLO閾值電壓,電路斷開;從UVLO閾值電壓到OVLO閾值電壓,電路導通;超過OVLO閾值電壓,電路斷開。

■ 功率開關的選擇:N溝道MOS電晶體 vs. P溝道MOS電晶體

在欠壓/過壓閉鎖設計中,功率開關可以使用N溝道或P溝道MOS電晶體來實現。

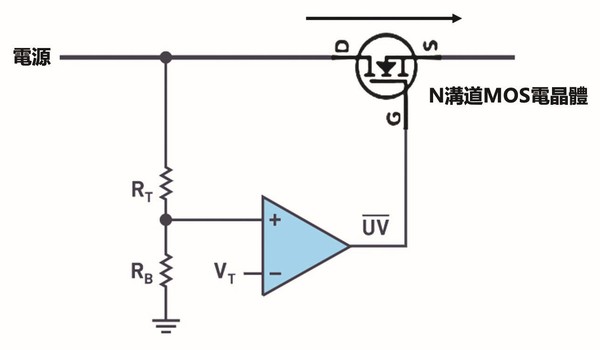

使用N溝道MOS電晶體做為功率開關時,會有一個小問題,如圖3所示:

| 圖3 : 使用N溝道MOS電晶體,做為欠壓閉鎖電路功率開關(source:ADI) |

|

當柵極(G)電壓為低電壓(例如:0 V)時斷開(高電阻)。當柵極(G)電壓為高電壓時導通,為了完全導通(低電阻)N溝道MOS電晶體,柵極(G)電壓必須比源極電壓(S)高出MOS電晶體閾值電壓。而導通時,MOS電晶體源極(S)與漏極(D)電壓一致,也就是要求柵極(G)電壓必須比電源電壓高出MOS電晶體閾值電壓。因此,這需要使用電荷泵來解決這個問題。

當然,使用一些專用的欠壓/過壓保護晶片—例如LTC4365、LTC4367和LTC4368整合了比較器和電荷泵。可驅動N溝道MOSFET,同時靜態功率消耗較低。

P溝道MOSFET不需要使用電荷泵,但閘極電壓極性相反;亦即低電壓時開關導通,而高電壓時斷開P溝道MOS電晶體。

帶有遲滯功能的欠壓閉鎖電路/欠壓閉鎖電路

對於上述應用,如果輸入電壓上升緩慢並且有雜訊,或者在電池的應用場景中,電池本身的內阻導致電壓隨著負載電流變大而下降,比較器輸入電壓可能會在閾值電壓附近波動。

為了避免這種類型的波動導致電路的反覆振盪,需要導入遲滯來避免這種振盪。比如使用有磁滯的比較器,或者加一些被動元件來實現磁滯功能,進而提高比較器抗雜訊能力。

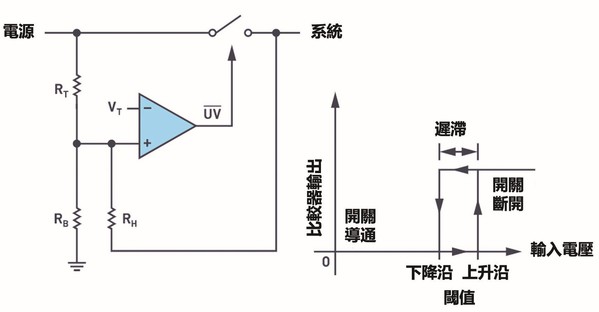

如圖4所示,欠壓閉鎖電路中,在比較器的正輸入與輸出之間增加一個電阻(RH),來實現延遲。

| 圖4 : 帶有遲滯功能的欠壓閉鎖電路(source:ADI) |

|

舉個直觀的例子,假設VT=1V,RT=10 × RB:

‧ 不加RH時,則上升和下降閾值為11 V。

‧ 增加RH= 100 × RB,則上升輸入閾值為11.1V,下降閾值為10.09V;亦即遲滯為1.01V。注意該方法對OVLO無效。

如果過壓OVLO需要帶有遲滯功能,該如何實現呢?增加遲滯的另一個方法是,可以加一個開關來改變底部電阻有效值。

| 圖5 : 帶有遲滯功能的欠壓/過壓閉鎖電路(source:ADI) |

|

如圖5:當VIN高於閾值之後,比較器低電平輸出,斷開M1,進而使RH與整個電路斷開

該方法在欠壓閉鎖電路和過壓閉鎖電路中均可使用。

■ 帶磁滯功能的比較器

要實現磁滯功能,一種簡便的方法是直接使用帶磁滯功能的比較器。

可以在Digi-Key篩選器中,在類型欄中選擇「窗口」,即是帶磁滯功能的比較器。

| 圖6 : 在Digi-Key網站中搜索帶磁滯功能比較器 |

|

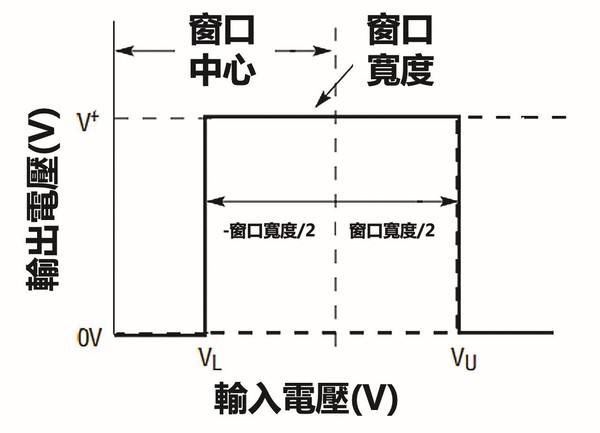

這類比較器會針對上升輸入(例如:V +視窗寬度/2)和下降輸入(例如:V - 視窗寬度/2)提供不同的閾值。

| 圖7 : 帶磁滯功能比較器的輸入輸出關係(source:ADI LTC1042CN8#PBF數據手冊) |

|

結論

依據比較器的相同控制電路,利用電阻分壓器,可以輕鬆實現欠壓和過壓電路設計。面對電源雜訊,可以使用帶有遲滯功能的比較器,也可以調節回饋來實現遲滯功能,以防止電源超過閾值時出現電源開關打開和關閉顫振。

(本文由Digi-Key Electronics提供;作者Alan Yang任職於得捷電子Digi-Key)