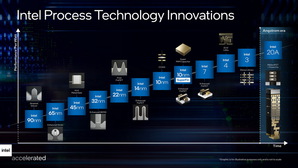

英特尔首次详尽揭露其制程与封装技术的最新路线规划,并宣布一系列基础创新,为2025年及其之后的产品注入动力。除了首次发表全新电晶体架构RibbonFET外,尚有称作PowerVia之业界首款背部供电的方案。英特尔亦强调迅速转往下一世代EUV工具的计画,称之为高数值孔径(High NA)EUV。英特尔有望获得业界首款High NA EUV量产工具。

|

| 英特尔揭晓制程与封装创新路线规划,为2025年及其之后的下一波产品注入动力。 |

产业早已意识到,目前以奈米为基础的制程节点命名方式,并不符合自1997年起采用闸极长度为准的传统。英特尔公布其制程节点全新的命名结构,创造清晰并具备一致性的架构,给予客户更为精确的制程节点认知。随着英特尔成立Intel Foundry Services,这种重要性更胜以往。英特尔所揭晓的各种创新,不仅开展了英特尔的产品路线规划,它们对于晶圆代工的客户也相当重要。

英特尔技术专家们以新的节点命名方式,详述下列未来制程与效能蓝图规划,以及各节点所具备的创新技术:

‧Intel 7:植基于FinFET(鳍式场效电晶体)最佳化,相较Intel 10nm SuperFin每瓦效能可提升大约10%~15%。 Intel 7将会使用在2021年的Alder Lake用户端产品,以及2022年第一季量产的Sapphire Rapids资料中心产品。

‧Intel 4:全面使用极紫外光(EUV)微影技术,透过超短波长的光,印制极小的形状。伴随每瓦效能提升约20%,以及面积改进,Intel 4将于2022下半年准备量产,2023年开始出货,client用户端Meteor Lake和资料中心Granite Rapids将率先采用。

‧Intel 3:进一步汲取FinFET最佳化优势与提升EUV使用比例,以及更多的面积改进,Intel 3相较Intel 4约能够提供18%的每瓦效能成长幅度。 Intel 3将于2023下半年准备开始生产。

‧Intel 20A:以RibbonFET和PowerVia这2个突破性技术开创埃米(angstrom)时代。 RibbonFET为英特尔环绕式闸极(Gate All Around)电晶体的实作成果,亦将是自2011年推出FinFET后,首次全新电晶体架构。此技术于较小的面积当中堆叠多个鳍片,于相同的驱动电流提供更快的电晶体开关速度。 PowerVia为英特尔独特、业界首次实作的背部供电,藉由移除晶圆正面供电所需回路,以达最佳化讯号传递工作。 Intel 20A预计将于2024年逐步量产。英特尔也很高兴公布Qualcomm将采用Intel 20A制程技术。

‧2025与未来:Intel 20A之后,改良自RibbonFET的Intel 18A已进入开发阶段,预计于2025年初问世,将为电晶体带来另一次的重大性能提升。英特尔也正在定义、建立与布署下一世代的EUV工具,称之为高数值孔径EUV,并有望获得业界首套量产工具。英特尔正与ASML紧密合作,确保这项业界突破技术能够成功超越当代EUV。

英特尔拥有基础制程创新的悠久历史,推动产业前进并破除限制。在90奈米领衔转换至应变矽,于45奈米采用高介电常数金属闸极,于22奈米导入鳍式场效电晶体,Intel 20A将会是另外一个制程技术的分水岭,提供2个突破性创新:RibbonFET和PowerVia。

英特尔新的IDM 2.0策略,对于实现摩尔定律优势而言,封装变得越来越重要。英特尔宣布AWS将是第一个采用IFS封装解决方案的客户,并同步提供下列先进封装蓝图规划的远见。

‧EMIB:自2017年产品出货开始,以首款2.5D嵌入式桥接解决方案持续引领产业。 Sapphire Rapids将会是首款量产出货,具备EMIB (embedded multi-die interconnect bridge) 的Intel Xeon资料中心产品。它也会是业界首款具备4个方块晶片的装置,提供等同于单一晶片设计的效能。 Sapphire Rapids之后,下一世代的EMIB将从55微米凸点间距降至45微米。

‧Foveros:汲取晶圆级封装能力优势,提供首款3D堆叠解决方案。 Meteor Lake将会是Foveros在client用户端产品实作的第二世代,其具备36微米凸点间距,晶片块横跨多种制程节点,热设计功耗从5至125瓦。

‧Foveros Omni:采用晶片与晶片连结与模组化设计,提供不受限的灵活高效能3D堆叠技术。 Foveros Omni允许混合多个顶层晶片块与多个基底晶片块,以及横跨多种晶圆厂节点的分拆晶片(die disaggregation)设计,预计将于2023年准备大量生产。

‧Foveros Direct:为降低互连电阻,改采直接铜对铜接合技术,模糊了晶圆制造终点与封装起点的界线。 Foveros Direct能够达成低于10微米的凸点间距,提升3D堆叠一个量级的互连密度,为原先被认为无法达成的功能性晶片分割开启新页。 Foveros Direct是Foveros Omni的补充技术,同样预计于2023年问世。