先进的CMOS制程技术使IC设计人员能够提供更高性能的元件,但也增加了额外电路板级静电放电(ESD)保护以确保终端产品可靠性的需求。

IC制程技术趋势

先进的CMOS技术使半导体供应商能够生产特征尺寸日趋减小的积体电路(IC)。减小IC特征尺寸的优势不计其数。特征尺寸越小,就使电路可以占用更小的面积,使IC能够以更小的矽片面积承载更多功能,而且每颗IC的成本更低。

特征尺寸更小的CMOS电晶体的性能也更高。结果就是功能更多、性能更高、成本更低的「三赢」局面。 CMOS制程尺寸已经大幅缩小;成熟的0.18μm或0.13μm制程可为订制类比/混合讯号专用积体电路(ASIC)项目提供高性价比的选择,与此同时,领先的数位IC设计已经瞄准诸如45nm 、32nm甚至是28nm等几何尺寸。

更小几何尺寸的副作用是要求更低工作电压。如果不能降低IC工作电压,将可能导致门氧化物失效及电晶体老化等其它可靠性问题。更低的电压同时带来正负两方面的影响。正面影响是更低的电压导致功率耗散更低,这也是当今流行电池供电手持电子设备所注重的一项主要优势。

负面影响是带来诸多电子设计挑战,如减小动态范围,以及伴随供电电压降低而来的讯号杂讯比(SNR)降低。此外,从电脑到手机等电子装置易于遭受的静电放电(ESD)等电气应力并未随着IC技术进步而改变电压或电流的数量级。结果就是较低电压的ESD事件可能损坏先进的IC。这就预示了应当如何设计电子系统来承受ESD。

为了理解这些,就有必要理解电路设计中如何纳入ESD保护。 IC级和系统级的ESD设计准则类似,因此我们将先探讨IC级的ESD保护,然后扩充讨论至系统级。我们然后就来了解电路板级ESD保护及恰当的电路板设计怎样在系统级ESD设计中发挥重要作用。

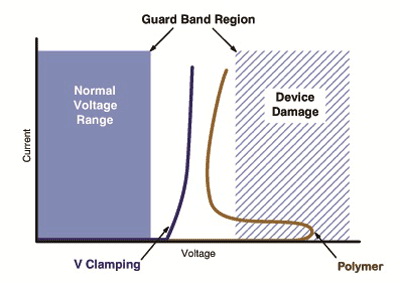

所有电子元件及电路都有预期的工作电压范围及安全防护带,如图1所示。超出此防护带的电压将引发电路损坏。由于先进的制程技术要求更低的工作电压,安全防护带也变得更窄。 ESD保护元件用于在遭受ESD应力期间将电压维持在安全防护区域内。

随着安全防护区域缩减,就需要导通阻抗更低的ESD保护元件,从而使电压维持在安全防护区域内。过压保护的典型实现途径是使用通过提供低阻抗路径将电压钳位至安全防护带区域内的元件,如图1中的电压钳位所示。

| 图一 : Operating-voltage regions for ICs and ESD-protection devices |

|

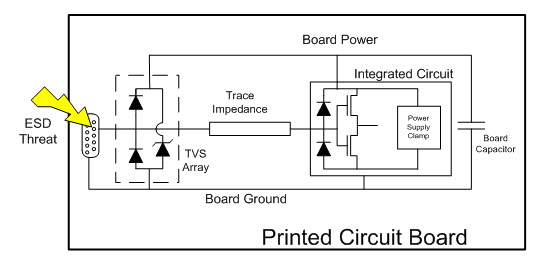

图2所示的是I/O接脚片上ESD设计的例子。

在图2左侧,电压钳位元件置于输入接脚,用于在电压超过正常工作电压范围时导通及提供通往IC接地汇流排的低阻抗路径。这就保护敏感的接收器免受电压及电流过大的影响。

这些钳位元件可以是单颗齐纳二极体、如图所示的背向齐纳二极体,或是特别设计的由nMOS电晶体构成的骤回(snapback)结构。

第二种流行方法是使用控制二极体(steering diodes)及电源钳位,如图2右侧所示。 I/O对地的负向应力将通过控制二极体传递至地,防止应力施加在输入门上。对地的正向应力将通过控制二极体传递至VDD及电源轨。

在VDD与地(GND)之间的电源钳位元件将把电流应力从VDD汇流排传递至地。电源钳位元件可以是简单的齐纳二极体或是有源电路,此电路检测VDD与GND之间的意外电压,并导通VDD与GND之间的大电晶体,提供低阻抗路径。在I/O与VDD之间遭受应力的情况下,此电路的工作特性类似。

图中右侧中的两组控制二极体及电阻是初级及次级保护策略的一部分。提供初级保护的最接近I/O接脚的一组二极体,旨在承载大部分应力电流。提供次级保护的是最接近敏感MOS电晶体门的一组二极体。某些应力电流将流经次级保护电路,但电路不仅对流入次级保护电流的电流进行限流,电阻上的压降也将帮助启动初级保护。在探讨系统级保护时还会注意到这种策略。

IC安全操作ESD设计与系统ESD设计之间的主要区别在于应力的大小。构建在大多数IC内的ESD保护旨在确保IC在ESD受控的生产厂(ESD事件鲜有发生,而且强度低)中能以高良率得到处理。如今,针对先进IC的ESD保护目标是1000V人体模型(HBM)及250V充电元件模型(CDM)。 1000V HBM的峰值电流约为0.67A,相应的衰退时间为150ns;CDM电流可达数安培,但持续时间可能仅为数奈秒(ns)。

这可以与测试系统在ESD事件下强固性的IEC61000-4-2标准规定的8kV应力条件下30A峰值电流、特征时间约为50ns进行对照。显而易见的是,如果没有特别的设计考虑,先进IC的输入及输出(I/O)接脚在系统级ESD脉冲条件下无法存续。

如果IC安全操作ESD测试及设计与系统级ESD测试及设计之间的区别主要是数量级问题,何不在实际连接至USB、乙太网、HDMI及Display Port等系统级I/O的I/O接脚中设计系统级ESD强固性?在某些情况下,这是有可能的,但通常并不明智。 ESD保护结构无法扩展到较小的区域,因为较小几何尺寸IC中能够用于ESD保护的空间有限。

系统级ESD电流大,不会扩展到较新世代的技术。以最先进技术设计系统级ESD结构需要的矽片面积大体上与以更成熟技术设计相同。采用更新技术的矽片面积的成本要高得多,因此,随着技术变得更加先进,系统级ESD保护的成本也随之升高。

此外,对于高速资料线路而言,有必要在保护设计中维持极低电容。对于通常拥有极高矽掺杂等级并导致大电容的大多数先进技术而言,这可能极为困难。因此,使用置于电路板上的ESD保护,如图3所示的暂态电压抑制器(TVS)元件,就变得极为可取了。

| 图三 : 置于印制电路板(PCB)的板载ESD保护示例 |

|

ESD保护元件

系统设计人员可以根据应用及预计会出现的过大应力类型,从多种保护产品中进行选择。

一种保护产品示例就是金属氧化物压敏电阻(MOV)。 MOV对暂态事件快速反应,但它们的大电容在讯号线路上施加了大量额外负载。晶闸管浪涌保护元件(TSPD)通常用于电信及乙太网设备保护,使其免受大电流承载能力导致的浪涌影响,但他们的反应速度通常太慢,而且其导通电压对于有效地ESD保护而言也太高。

TVS二极体

图3所示的是使用TVS产品。 TVS置于邻近I/O连接器的地方。在理想的状态下,TVS元件将先于IC的内部电路导通,并检测完整的对地浪涌电流。实际上,通常TVS产品与IC内部构建的ESD保护结构会共同承载电流。这种配置极类似于前文探讨的片上ESD保护的初级及次级保护(如图2所示)。

置于电路板上的TVS产品相较于片上ESD保护具有优势,因为走线电感及匹配电阻等电路板相关元件能用作ESD保护策略的组成部分,限制ESD电流流入IC,并提供帮助导通初级板载ESD保护元件的额外电压降。安森美半导体生产宽广阵容TVS产品,用于多种应用,而且设计提供业界领先的低钳位电压。

TVS二极体产品相较于MOV及聚合物ESD保护产品拥有优势。 MOV及聚合物对于正向及负向应力拥有对称特性。 TVS元件可以设计为提供对称及不对称特性。单齐纳二极体拥有不对称特性,以某种极性作为正向偏置二极体导电,并相反极性用作齐纳击穿二极体。这非常适合用于保护只包含单极性(如0至3.3V)的电路节点。背向二极体提供对称回应,以正向及齐纳击穿导电的串联组合导电,同时用于正极性及负极性。这非常适合用于保护相对于0V的对称(如-3.3 V至+3.3 V)电路节点。

使用电源解耦

ESD保护阵列可以在保护策略中整合电源解耦电容。在ESD频率,电源与地电平之间的μF范围解耦电容提供了低阻抗的对地通道。 TVS阵列中的控制二极体可将ESD电流引导进入电路板上的电源及地电平线路,大幅减小电路板上的电压暂态,如图4所示。

TVS阵列中的齐纳二极体进一步限制电压暂态。构建地阵列封装中的齐纳二极体也有极低电感,因此在消除ESD事件期间可能出现的电感型电压尖峰方面极为有效。为了发挥效用,电路板级电容需要邻近TVS阵列,且TVS阵列及电容的位置布设都需要避免高阻抗连接,如既长又窄的走线。安森美半导体生产适合众多应用的TVS阵列产品。许多产品针对特定应用,且其设计旨在简化电路板布局。

| 图四 : TVS数组及解耦电容用作ESD保护策略组成部分的示例 |

|

保护高速资料线路

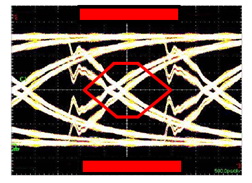

当TVS二极体用于保护高速资料线路时,TVS二极体的电容将导致讯号干扰,导致资料完整性降低。图5及图6所示的眼图比较了未采用保护及采用了65pF电容TVS二极体的USB 2.0讯号线路,展示了电容性负载如何使讯号转换失真。图6中穿过USB 2.0范本(mask)的迹线彰显了增加电容性负载时令人不可接受的讯号完整性。设计人员必须鉴别出能够保护敏感线路而不会增加降低讯号品质之电容的ESD保护方案。

| 图六 : 采用了65pF ESD保护二极管的USB 2.0数据线路眼图 |

|