对于介于放大器与ADC之间的抗混迭滤波器设计而言,

系统性的做法将有助于设计人员处理涉及其中的各种因素、参数与设计取舍。

以主动式前端放大器驱动高速转换器时,抗混迭滤波器的设计是相当困难的任务。对抗混迭滤波器的正确理解很重要,因为反锯齿的特性能防止主要频段以外不要的噪声落入频段内,所以了解好的抗混迭滤波器的必须性乃是完善高速模拟讯号链设计的关键。在实作阶段必须审慎考虑各种细节因素。

中频取样与奈奎斯特(Nyquist)考虑

中频取样 (IF ; intermediate frequency)允许设计者从讯号链省去一个混频降频(mix-down)级,又可提升性能,此其经由减少整体组件数量而降低了系统噪声,从而维持良好讯号噪声比(SNR)。某些特定条件之下,又能因此降低混频器造成的本地振荡器讯号泄漏(local oscillator (LO) leakage )现象,达到增进无杂散动态范围(SFDR)的效果。

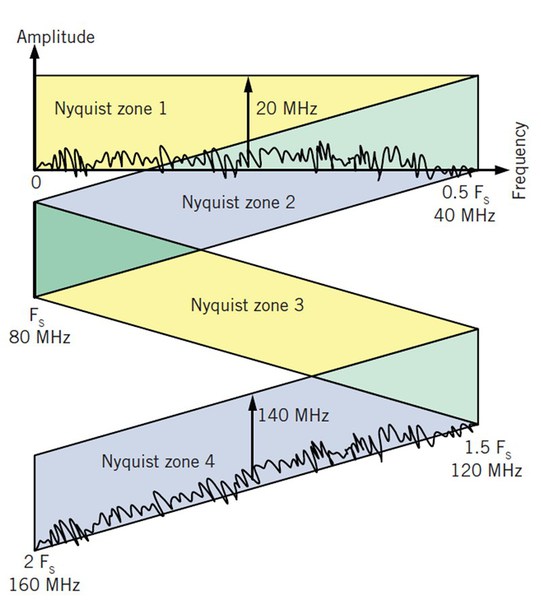

基频取样适用于主要讯号或频率落在第一奈奎斯特区域( first Nyquist zone)的状况,但某些转换器仍然可在高于第一奈奎斯特区取样,这被称之为欠取样(undersampling )或中频取样 (IF sampling)。如图1所示,其讯号落在第四奈奎斯特区,可看出此讯号影像或锯齿被反射回第一奈奎斯特区上,就像是个20MHz讯号。

| 图一 : 欠取样(undersampling )或中频取样 (IF sampling) 适用转换器在高于其两倍取样频率(F_S)之奈奎斯特区进行取样。举例而言,若ADC取样频率为80 MHz 而量测频率为140 MHz 则其讯号落在第四奈奎斯特区。 |

|

而大多数快速傅利叶转换(FFT)分析器,例如Visual Analog,只会描出第一奈奎斯特区(0到0.5F_S)的傅利叶转换。因此,假如主要频率高于0.5F_S,则影像会被向下反射至第一奈奎斯特区(或称为基频) ,而这很可能会因为混附波(spurious tones)出现在主要频段内而让情况变得混乱。

根据Walt Kester在 High-Speed Design Seminar书中所述,模拟数字转换器(analog-to-digital converter ; ADC)可大于0.5F_S取样率且不违背奈奎斯特准则:讯号必须以不少于自身带宽两倍的速率来进行取样方能保有其完整内容。关键在于讯号带宽的所在位置,只要讯号不重迭并保持在单一个奈奎斯特区之内即符合奈奎斯特准则,而唯一动到的是第一奈奎斯特区域至其上层的位置。

@大標:开始抗混迭滤波器的设计

设计开始

抗混迭滤波器有助于减少来自于不需要的奈奎斯特区讯号内容,避免频带内(in-band)锯齿及破坏讯号链的动态效能。抗混迭滤波器的设计通常使用LC网络,加上明确定义的信号源与负载阻抗,以达到所需相关停止带(stop-band)与通带(passband)特性。滤波器网络实作上可沿用各式各样的滤波器合成做法的参考书,其中常用柴氏(Chebyshev) 或巴氏(Butterworth)多项式来定义滤波器转换函数。

滤波器转换函数的格式完全取决于应用特性的需求,例如巴氏滤波器显现大致浑圆响应,具有最佳通带平坦度(0 dB 的涟波)与良好相位响应。反之,柴氏滤波器可达到较佳阻带衰减或滚降(roll-off),却牺牲些通带平坦度(涟波增大)。

有些以软件为基础的滤波器程序可以简化这些问题,诸如Filter Free 4.0(Nuhertz Technologies) 、QUCS( Quite Universal Circuit Simulator)或ADS(Advanced Design System, Agilent Technologies)。初步可用放大器/ADC接口设计,假设其使用的带通滤波器(bandpass filter)可在带宽、讯号噪声比(SNR)与无杂散动态范围(SFDR)等指针达到最佳效能:

.放大器必须以其数据手册所建议的正确dc负载运作以达最佳效能。

.放大器与滤波器所呈现的负载之间必须配置合适的串联电阻以避免出现通带内的异常峰值。

.使用外部并联电阻可降低对ADC的输入,并且在ADC与滤波器之间配置合适的串联电阻,可降低通带峰值。

模拟前端电路的设计其实有点「牵一发动全身」的味道,

举例来说,调整电阻就会影响到SNR值的变化。

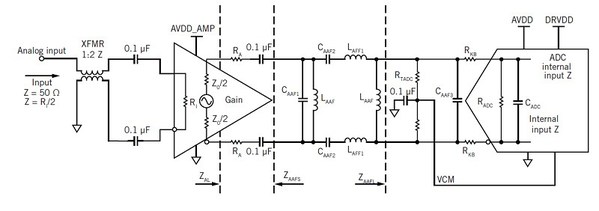

抗混迭滤波器设计运用在相对较高输入阻抗的高速ADC与低阻抗驱动源(放大器),若以一组广义电路(图二)进行理解,其核心设计过程具有以下七个步骤:

| 图二 : 这种广义电路类似多数高速差动放大器/ADC接口,用于解释经由使用多数高速ADC的相对高输入阻抗与相对低驱动源阻抗以优化滤波器全插入损耗。 |

|

.设定外部ADC终端电阻R_TADC 使并联组合R_TADC 与R_ADC 其值介于200 Ω 与400 Ω之间。

.根据实验或ADC数据手册建议选择R_KB ,其值一般介于5 Ω 与36 Ω之间。

.根据下式计算滤波器负载阻抗:Z_AAFL=2R_TADC | | (R_ADC+2R_KB )

.设定放大器外部串联电阻R_A 。若放大器差动输出阻抗介于100 Ω 与200 Ω之间则将R_A 设成低于10 Ω;若放大器差动输出阻抗不高于12 Ω则将R_A 设成介于5 Ω 与36 Ω之间。

.根据下式设定Z_AAFL 使放大器全负载Z_AL 可被特定的差动放大器优化:

Z_AL=2R_A+Z_AAFL

.计算滤波器源极电阻:Z_AAFS=Z_O+2R_A

运用设计程序或表设计滤波器时,使用相同源阻抗值Z_AAFL 与负载阻抗值Z_AAFS ,此其有助于降低滤波器损耗,而任何两端阻抗之差距会造成10*log(input Z/output Z)的损耗。例如输入阻抗为50 Ω输出为200 Ω时,滤波器损耗为-6.0 dB 或10*log(50/200)。并且增加 10%带宽以确保频率展开的平坦度。

经过上述初步计算阶段,还必须根据下列规格快速检阅电路细节:

.C_AAF3 之值应至少为10 pF使其大于C_ADC 值数倍,如此可优化滤波器对于C_ADC 变动的敏感度。

.Z_AAFL 与 Z_AAFS 比值不可高于7,使滤波器不超过多数设计程序的限度,理想上这两个值应该设相等以优化损耗。

.C_AAF1 之值至少为5 pF以优化滤波器对于寄生电容与其他组件值变动的敏感度。

.L_AAF 电感之合理设定值约在数个nH。

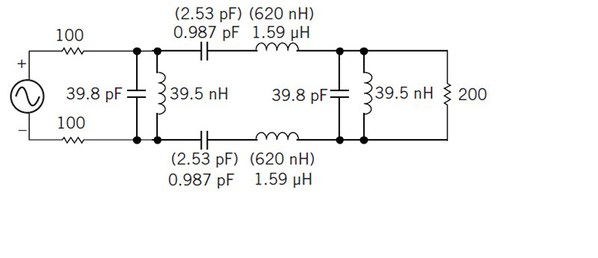

.C_AFF2 与L_AAF1 值应合理设定,必须留意有时电路仿真器会把这两个值设成过高或过低。通常将其与较佳标准组件值保持一定比率以维持相同共振频率(如图3)。

| 图三 : 若C_AFF2 与L_AAF1不为合理设定,则使用标准L与C值并保持一定比率以维持相同共振频率。 |

|

有些状况下滤波器设计程序会跑出多种解,特别是那些高阶滤波器,而采取最合理组件组合值的解法应是其中最适宜可行的,并且还得选择相符于并联电容器末端的组态。使其能与ADC的输入电容结合。

设计取舍

接口电路的参数彼此之间有高度互动性,因此绝难针对特定规格指针(如带宽、带宽平坦度、讯号噪声比与无杂散动态范围、与增益)加以优化。然而带宽响应常发生的峰值现象可经由调整R_A 与R_KB 值加以最小化,

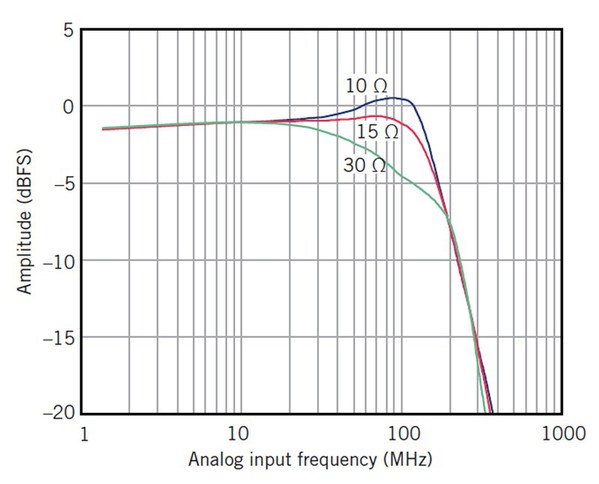

图四指出通带峰值高低与输出串联电阻值R_A升降之间关系。但随着电阻升高造成更严重的讯号衰减,放大器须驱动较大讯号以填满ADC的满量程输入范围。

| 图四 : 增加输出串联电阻R_A可降低通带峰值,然而却同时造成讯号衰减,放大器须驱动较大讯号以填满ADC的全部输入满量程。 |

|

调整R_A也会影响讯号噪声比(SNR),调高R_A 值而降低带宽峰值,因减少带宽内不要的噪声可能会些微增加SNR。

设定ADC的输入端串联电阻R_KB 可优化ADC内部取样电容剩余电荷注入所造成的失真现象 。调高R_KB也会降低带宽峰值,却也会造成讯号衰减效应,放大器须驱动较大讯号。

对于通带中心频率的优化可经由微调C_AFF2串联电容达成,由此设计者可安排应用所需的最佳频率覆盖。

一般来说,终端电阻R_TADC 的设定必须维持ADC净输入阻抗在200 Ω至400 Ω之间,与多数典型放大器负载相符,太高或太低都会影响到放大器的线性度。

设计整合

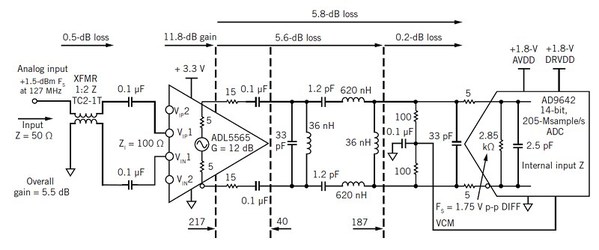

经由这些步骤来到窄通带接收器前端设计,基于ADI的超低噪声差动放大器驱动器与ADC (14位,取样率250-Msample/s) (图五)。

三阶巴氏抗混迭滤波器以效能与接口需求进行优化。滤波器网络与其他组件全插入损耗仅5.8 dB。此ac耦合设计采用0.1 μF电容以阻挡放大器、终端电阻与ADC之间的共模电压。

整个电路具有18 MHz带宽与3dB通带平坦度,讯号噪声比(SNR)与无杂散动态范围(SFDR)分别是71.7 dBFS与92 dBc(以127 MHz输入之下)。取样频率为205 Msamples/s,中频讯号所在的第二奈奎斯特区域介于102.5 MHz 与205 MHz之间。

其电路以宽广的带宽(3 GHz)1:2变压器接收单端输入并转为差动讯号。ADI的差动放大器(6 GHz) 在12 dB讯号增益运作之下具有100 Ω输入阻抗,以补偿滤波器网络与变压器的插入损耗(约5.8 dB),整体提供5.5 dB讯号增益。

输入讯号具有+1.5 dBm可在ADC输入端产生满量程1.75 V p-p差动讯号。根据标准设计程序采用的抗混迭滤波器为三阶巴氏滤波器,乃是由于其通带平坦特质,而三阶滤波器可获致1.05的ac噪声带宽比。为了达到最佳效能,以净差动负载 200 Ω加载差动放大器, 所串联的15 Ω电阻区隔滤波器电容与放大器输出。 以100Ω 电阻并联下游阻抗,再加入30 Ω串联电阻获致 217 Ω净负载阻抗。

ADC输入端串联的5 Ω电阻隔离滤波器与放大器内部开关瞬时,2.85 kΩ输入阻抗乃是由ADI的ADC(14位,取样率250-Msample/s)数据手册所定。可单纯采用并联追踪模式(parallel track mode)值定出中频中心。

三阶巴氏滤波器设计以差动式200 Ω讯号源阻抗与200 Ω负载阻抗优化滤波器损耗,具有中心频率127 MHz、3 dB通带平坦度与20 MHz带宽。图三显示经由标准滤波器设计程序所计算的结果。以较高串联电感前提之下,1.59 μH电感减低至620 nH,而0.987 pF电容随之增为2.53 pF,维持相同的127 MHz共振频率,并且具备更切实际的组件值。

以电容器置于ADC附近以减低或吸收输出入相互干扰电荷,其电容为37.3 pF,由第二并联电容值减去ADC内部2.5 pF电容而得。

图五显示实作调整寄生回路后滤波器被动组件设定值。其总结所测系统效能为:18 MHz带宽(中心频率127 MHz)与3 dB通带平坦度,网络全插入损耗为5.8 dB。图六显示频率响应与SNR/SFDR对应图 。

| 图五 : 文中所述过程获致基于三阶巴氏抗混迭滤波器的窄通带接收器前端设计,其中 0.1-μF电容用以阻挡放大器、终端电阻与ADC之间的共模电压。 |

|

以曲线图显示不同频率之下的通带平坦度效能(上图)与SNR/SFDR效能(下图),二者取样率皆为205 Msamples/s。

结论

对介于放大器与ADC之间的抗混迭滤波器设计而言,不同因素、不同参数取舍设定的困难程度甚高。在先前设计之中,所有参数皆被赋予相同的权重,而从参数的取值上就直接反映在系统整体接口效能上。而有些设计则会针对系统应用所需,从SFDR、SNR或输入驱动等级各方面考虑来进行特定参数优化。

(本文作者现任ADI 军事航天应用工业与仪器部门资深应用工程师,曾在转换器接口、转换器测试与模拟讯号链等相关应用领域发表诸多论文。)