過往在晶片開發上,晶片業者為了能與其他競爭對手抗衡,甚至是超前,在自有技術與矽IP的開發上,一直都投入相當大的心力與資源,但製程不斷向前推移,為了確保良率與因應晶片推出時程的壓力,晶片業者無法兼顧自有IP的研發,所以ARM與Imagination等IP授權業者的趁勢而起,多少也解決了晶片業者在自有IP研發上的困境。

但衍生的另一個問題在於,正因為系統單晶片內部IP有不少是透過IP授權業者取得,不論是在品質或穩定性,相對不易掌握,所以晶片開發後期的驗證流程上,所花費的時間與成本就增加許多,其最終目的,還是希望在進入光罩程序後,能一次到位,避免不必要的開發成本出現。所以EDA三大業者在這幾年的市場重心之一,都是放在驗證流程上。

另一方面,除了與IP授權業者保持密切合作外,與主要的晶圓代工業者配合,也是必要的策略之一,只要能取得晶圓代工業者在製程上的認證,在晶片設計公司的眼中而言,對EDA業者們就是一種加分效果。所以廣泛來看,IP授權、EDA與晶圓代工三方之間的緊密合作關係,在這幾年可說是業界的常態。

驗證只是概念 無縫接軌的平台才是關鍵

談到驗證領域,Cadence亞太區系統解決方案架構師暨驗證平台總監張永專說,其概念就是從輸入訊號之後,來觀察輸出端的表現是否符合工程師的期待而已。不論是仿真(Emulation)、模擬(Simulation)或是原型建造(Prototyping)等,它們都是屬於驗證方法的一種而已,只是依其功能的不同,會給予使用者不同的圖表似參考之用,以原型建造為例,它就是偏重後端軟硬體整合的驗證工具為主,所以嚴格來說,使用者不太可能使用同一套工具來滿足所有驗證需求。

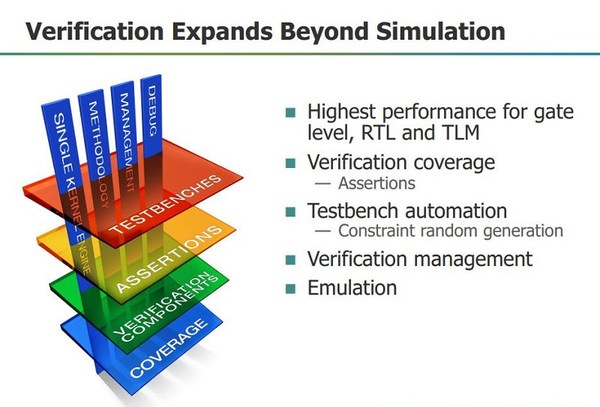

| 圖1 : 驗證成了EDA業者近年來十分重視的市場,如何提供友善的環境與工具,成了大廠們所思考的重點。(Source:明導國際) |

|

明導國際亞太區技術總監李潤華指出,不論是模擬、仿真或是原型建造等,就明導國際的立場,是希望提供單一平台(亦或是環境)給客戶,舉例來說,近年來,業界在驗證流程已經開始出現統一協定:UVM (Universal Verification Methodology),三大EDA業者皆可以支援,但明導的工具可以協助客戶在無需轉換的情況下,就可以與UVM無縫接軌。反之新思科技的產品,在部份的格式不相容的情況下,就仍需要有格式轉換的工作,而這樣的情形也容易出現資料缺漏的情況。

呼應了李潤華的看法,Cadence執行副總裁暨系統與驗證事業群總經理黃小立博士似乎也頗為認同,黃小立博士認為,驗證本身就是一個相對複雜的流程,各家業者都在開發不錯的工具,問題是,彼此之間如何無縫連結,倘若無法連結,資訊溝通上就會產生一定程度的差距。另一方面,晶片驗證用硬體仿真跟原型建造的方式來處理,就會產生不同的RTL(Register-Transfer Level),在不停地來回修正之下,只會造成更多不必要的BUG,即便採用對應的工具來進行驗證,在生成RTL之後,在進行整合時,就是會有問題產生,所以解決RTL的整合問題,成了EDA業者們的共同考驗,而Cadence早在幾年前就已經著手處理相關課題,近期也看到其他的EDA業者們,在因應相同的課題。

所謂的驗證只是一種概念,

它其實包含很多方法,像是模擬、仿真,

都是屬於驗證的方法之一,

而關鍵在於如何將這些工具有效加以整合?

張永專表示,就Cadence在驗證方面的工具組,依其不同的設計流程,會提供對應的工具,一般來說,從最底層的IP驗證,就需要先經過形式驗證(Formal Verification)、模擬與加速/仿真(Acceleration/Emulation)等三道程序,其後是原型建造與軟體驗證等程序,但僅有這些流程的相關工具還不夠,如黃小立博士與XXX所言,提供單一平台或是環境,將這些工具加以串聯,有其必要性,所以Cadence有Indago與vManager等工具各自協助前述所提到的流程,扮演除錯與管理之責。

軟硬整合只求速度提升

李潤華進一步談到,軟硬體共同驗證,其處理的速度就要夠快,考量硬體驗證方案需要耗費大量電力與極佔面積的情況下,明導在相關方案的作法,採用虛擬化的概念,與一線的IT業者相同,提供類似於伺服器的硬體機箱與模組化板卡,可以進行抽換,同時採用氣冷式架構,在散熱能力上能有較佳的表現,所以也能省下不少電費,對於晶片設計業者來說,營運成本也是相當重要的一環,在這方面,明導的表現算相當不錯。同樣的,在原型建造領域也是秉持軟硬整合的概念,如新思科技可說是代表之一。

Design Rule確認 亦是箇中關鍵

除了驗證之外,先前已經提到,EDA工具若能取得晶圓代工業者的內部認證,對於EDA業者,有直接的加分作用。

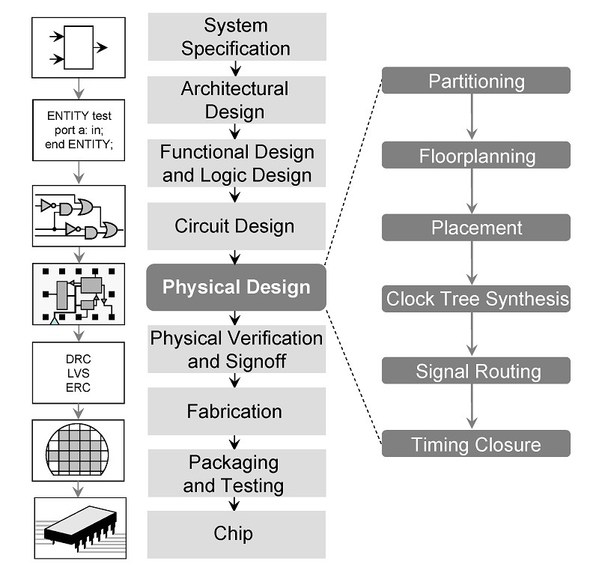

李潤華直言,不論是在哪個製程節點,明導國際的Calibre都是最早導入台積電的,在先進製程上,像是線寬線距的調整或是雙重曝光等這類的問題,都必須用Design Rule(設計規則)來加以描繪,不過並不是每一代的製程節點都適用,只要Calibre工具完成驗證,才能交由客戶進行新一代製程產品的設計。所以嚴格來說,Design Rule的制定某種程度上可以視為該製程節點的標準程序,因此,即便是IP授權業者,也需要對應的Design Rule,如此一來,其IP方案才能順利導入晶圓代工業者的先進製程,簡言之,在先進製程的Design Rule尚未定案之前,IP方案是無法發揮作用的。也因此,即便是競爭對手的新思科技與Cadence的IP團隊,都必須要與明導國際有適當地配合,才能與台積電的先進製程無縫接軌。

| 圖2 : 引進先進製程後,若要讓晶片良率有所提升,Design Rule與設計流程的重要性不言可喻。(Source:www.wikiwand.com) |

|

結論

可以確定的是,EDA三大業者努力耕耘驗證領域,或多或少都已經明白,單一工具雖然有其重要性,但各種工具之間的整合與接軌也是極為重要的一環。另一方面,在IP導入晶圓代工業者的先進製程前,Design Rule亦有其舉足輕重的地位,從這一點來看,即便是競爭關係的EDA業者們,也必須採取合作,以確保與晶圓代工業者之間的伙伴關係。未來在合作大於競爭已經成為唯一的生存法則的情況下,未來EDA市場的發展,值得繼續留意。

刊頭圖片(Source:www.perceptionsoftware.com)