多年來,軟體於嵌入系統設計中扮演越來越重要的角色。而從定義及描述基礎硬體平台的程序,以至於使用者介面及應用層級中,程式碼已經成為工程學加值及任何產品進行差異化的要項。

這個趨勢形成了硬體及軟體 (經常是硬體設計者及軟體程式設計者之間健康的緊張關係)角色間的複雜交互作用。昔日每塊晶片都是全客製元件以建置所有功能於硬體中,而於製造(fab-binding)時便擁有其功能組合的日子已不復見了。另一方面,具備以高階語言撰寫之傳統程式來定義行為的元件之「處理器」架構,同樣也以可編程核心加入SoC元件中,周邊則是具備特定功能的硬體。

軟體較容易修改、更新及維護

跨越「可編程」及「硬線」之鴻溝的方法,為可配置式解決方案(如FPGA)。其部署一套通用硬體資源而可進行功能化配置,因此本質上並未改變。硬體描述語言可用來描述所需的行為, 而功能則是於通電(field-binding)時設定。無論用什麼方法,目前幾乎所有硬體都擁有某些軟體元件。設計者們均認同軟體較容易修改、更新及維護,這是關鍵要求,尤其是於具成本壓力及擁擠的市場環境中。

這種雙重特性致使在設計流程中越來越難達到一貫性及整合性。儘管如SystemC之開發便是企圖跨過硬體及軟體主導的領域, 但每一類型的設計仍然大量保留了自身獨特的設計工具及方法學。對於此問題的解決方法,是展開對軟體化的晶片(SDS)矽晶架構方法之進程,其能提供大量軟體驅動設計流程,並使用相似的軟體開發範例。

SDS的實體建置,係根據多核心陣列處理器架構。概念性而言,此組成可視為建置大量獨立操作連續程序。此陣列透過訊息傳遞溝通,可加以配置來高效率地執行相關功能,包括作為較初始程序的平行結構,或連續操作的連續組成。

SDS軟體架構

SDS 架構需要用來做為程序排程、同步化、通訊及輸入/輸出任務的硬體資源。雖然各個核心的指令集必須為相同的協同處理、通訊及I/O功能提供便利性,此以傳訊為基礎的通訊仍保留了各個初始程序的獨立性,並使其能建立高效率、可擴展至百個程序的多核心晶片。其協同成本可有效率的降低,以支援負載、儲存、分立及算術運作。

SDS方法的優勢之一,是其支持各種編程技術,範圍從靜態配置網路至動態再配置等。協同程式可直接編寫入處理器指令集,其不須OS內核,並且於處理器建置時無微碼。

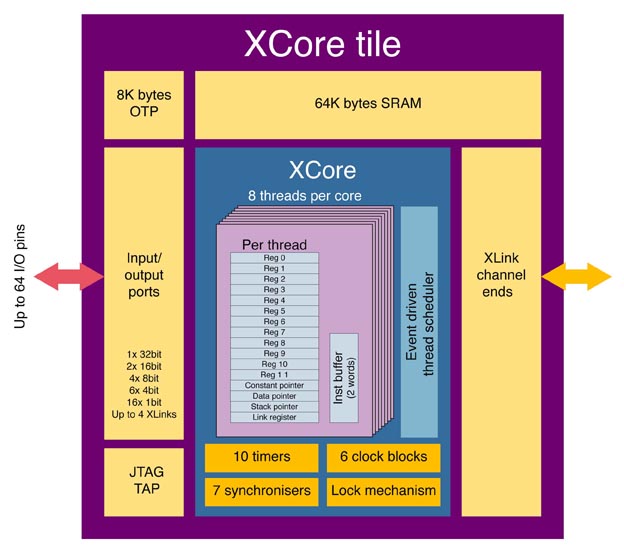

每個XMOS處理單元(或tile)包括處理器、本地指令及數據記憶體、處理實體介接之I/O架構,及一個處理執行緒交互及核心交互通訊的基礎設施,如圖一。造就了透過動態訊息定線網路通訊的處理器陣列:將此方法與常用於FPGA的方法比較是值得的,其包括藉由靜態配置互連而通訊的look-up表列。

| 《圖一 XMOS XCore tile以四個主要的元素來建置軟體化的矽晶。XCore 32位元8路多執行緒處理器,其為一個緊密整合的I/O埠架構;XLink執行緒交互通訊協定及基礎設施,以及64KB單一周期本地記憶體。》 - BigPic:623x552 |

|

I/O處理功能在SDS結構中尤為重要。其允許整個系統被轉譯成執行於vanilla矽晶的軟體圖像,而這就是用於SDS 的處理單元與傳統嵌入式處理器不同之處。欲建置I/O介面,此處理器必須對晶片外部針腳所產生的即時事件明確回應,無論所執行的是何種軟體。

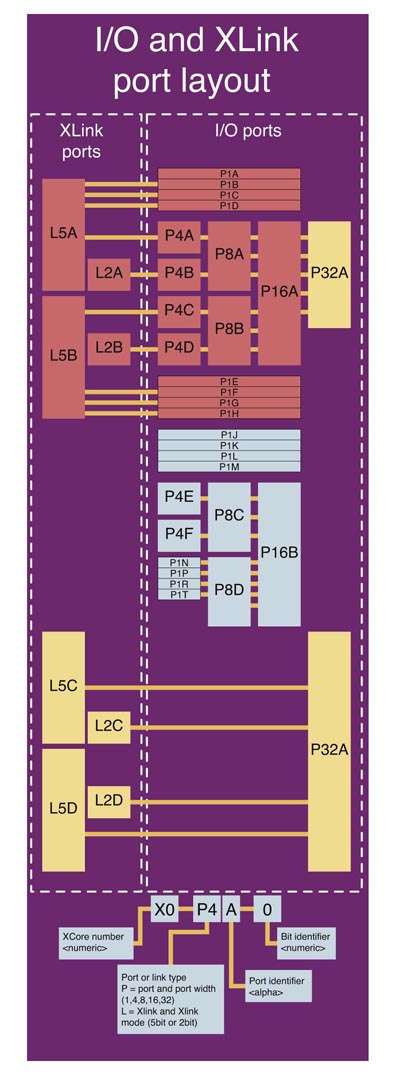

相對的,I/O應擁有足夠的智能以將針腳及處理器間的延遲降至最低,如圖二。於軟體中建置多重介面同樣會提高平行程式設計的挑戰,此軟體必須能快速切換內容,以使多重任務能有效率地同步執行。

EDA工具及硬體描述語言(HDL)須兼顧

雖然SDS方法適用於嵌入式軟體設計流程, 需留意的是, 這不代表須放棄已經建立在EDA 工具及硬體描述語言(HDL)的可觀知識與技術。特別是標準編程語言,如C語言,並不以其既有的平行性,在積體電路內容中以一有意義的方式處理事件或計時。

另一方面,無容置疑地,理想中硬體設計應該更像軟體編輯,這有許多理由可以解釋。首先, 針對具備數百個op-code的目標處理器,編寫一個具備數百個可變數的C程式是一個本來就完全可預期的過程,因此其只具備有限的「正確」答案。相反的,即使是一個小型50k系統閘極FPGA,都擁有50萬(大部份為獨立)個配置位元,所提供的可能組合範圍相當大,完全客製化的ASIC甚至有更多選擇。

| 《圖二 建置XCore的主要元素,是增加智能至I/O。為達到建置硬體介面所需的I/O延遲及頻寬, 此XCore上的埠緊密的耦合至核心,並支援廣泛的特性以降低軟體負荷。》 |

|

硬體設計者的這些窘境,使其需要在設計意向的描述中加入對目標元件的瞭解,以此可限制工具的使用,使其只考慮已知的最佳選擇,而避免已知的不良建置也同樣重要。軟體編輯是比HDL方法更短的程序。以HDL工作需要在直通(first-pass)目標矽晶定義前便完成綜合、配適、佈局與繞線 (P&R)。每一個步驟跟整個軟體編輯程序本身一樣複雜,而最後會產生許多等效結果。

如同前述提示,當相關設計需增加或需在最後一秒進行更改時,軟體化的流程一定有其優勢。在HDL方法中,既使模組從綜合至netlist之角度而言已充分地被隔絕,設計上的變更仍可在P&R過程中引發妥協,而重建時間(及增加中的功耗)方面,廣為人知的挑戰只有在設計變動後才會結束。

相反的,可編程元件以處理器引擎及程式計數器的暫時時間調擴效應,取代了P&R流程。於此情況下,自足式程式模組對於設計的其他部分衝擊有限,因此不需要任何本質上的妥協。

結論

自從硬體工程師接受邏輯綜合,並了解設計工具可被用來將高階定義的功能轉譯成低階製造細節,至今已超過20年。今日,嵌入式設計者正準備採取相似的信念。SDS 架構使他們能更趨近軟體工程的工作模式,將設計意向以更直接、編譯器型式轉譯成元件指令。

但僅採用軟體化的流程是不夠的。關鍵將是部署一個包含正確矽晶架構、謹慎設計指令集與彈性工具組之組合。而唯有能提供此三項優勢之供應商,才能在硬體及軟體的統合中獲致成功

<作者為XMOS Semiconductor行銷執行副總裁>