伺服器有許多不同類型,包括機架式、刀鋒式、直立式、以及適用於高密度計算的模組化配置類型。理想情況而言,每台伺服器皆會針對執行特定任務進行優化。然而,多數伺服器設計皆具備許多共同特徵,包括具備多個處理器和熱插拔記憶體、不同透過PCIe連接至CPU和PCH的周邊設備、以及安全服務和電源管理解決方案。儘管設計工程師為各種應用創建不同解決方案,多數案例皆針對基本伺服器架構進行客製。

圖1為上述常見架構。一般而言,為滿足不同市場需求,伺服器設計工程師會對此基礎架構進行客製。周邊硬體塊、系統級介面塊、BMC介面以及其他重要元件會因伺服器設計而所有差異。然而,電源管理、控制和膠合邏輯功能塊(圖1中功能一)在客製設計中扮演關鍵角色,以滿足特定應用需求。設計工程師需為不同伺服器類型客製功能,如電源管理、電路板專用的膠合邏輯或I/O擴增。儘管功能一無法協助CPU、硬碟或網路等承載業務,但有助於確保電路板上所有主要的元件在正常範圍內工作。設計工程師不斷致力於降低上述功能的成本和複雜性,並同時確保維持電路板的可靠性。

本文將探討在舊型伺服器設計中實現功能一的傳統方法,並將其與新型伺服器設計方法進行比較,也就是使用PLD整合上述功能。此外,本文更將討論其他可編程設計邏輯元件如何實現伺服器其他常用功能,以降低複雜性和成本。

| 圖1 : 8個PLD功能的伺服器設計框圖(設計實例) |

|

功能一:電源管理、控制和膠合邏輯功能

過去幾年,設計工程師使用多種分離元件實現電源管理、控制和其他膠合邏輯功能,此方法具有一定程度的成本效益。然而,隨著伺服器設計日益複雜、功能逐漸增加,此類設計所需元件亦越來越多。目前,設計工程師若要將功能一設計於多種類型的伺服器,採用分離元件將會增加時間和人力。例如,若改變電路板上複雜SoC元件數量,電源數量、膠合邏輯以及其他控制功能的數量也會隨之改變,就可能要進一步更改邏輯和基本時序。

因此,分離元件解決方案不僅會降低新型伺服器硬體產品的上市進程,更會隨著所需元件數量增加而提升成本。此外,更改設計有時會需要重新更改整個電路板,不僅拖延專案進程,更增加成本。

新型伺服器系統通常會將功能一與非揮發性PLD整合,PLD會在電路板通電後立刻開始運作(即時啟動)。 通常,實現功能一所需的邏輯資源和I/O數量取決於伺服器類型。因此,能提供豐富I/O數量和邏輯資源選擇的PLD元件,十分適合用以實現功能一。

萊迪思MachXO3 FPGA系列與上一代MachXO2系列(簡稱MachXO2/3)都能夠實現所需功能。MachXO2/3元件為支援即時啟動的非揮發性PLD,提供640 LUT到9400 LUT與22個I/O到384個I/O元件選擇。這些PLD可在系統中透明地進行更新,並提供雙重開機支援,以便修復不同系統更新錯誤。這些元件僅需單一3.3V電源即可運作,當電源電壓高於2.2V,即會啟動伺服器主機板電源管理演算法。

因此,MachXO2/XO3同時是電路板上第一個啟動與最後一個關閉的元件。這些元件支援多個I/O Bank,可在不影響其他模組運作下,單獨進行通電與斷電,此優勢使其能夠整合多種異構功能,例如多個電源塊控制、頻外訊號發送以及電源待機控制。藉由上述元件,設計工程師更能夠將SPI、I2C以及計時器/計數器介面增加至傳統設計中,並支援多次在可編程設計邏輯元件上配置快閃記憶體。

將功能一整合至控制PLD(MachXO2/3)

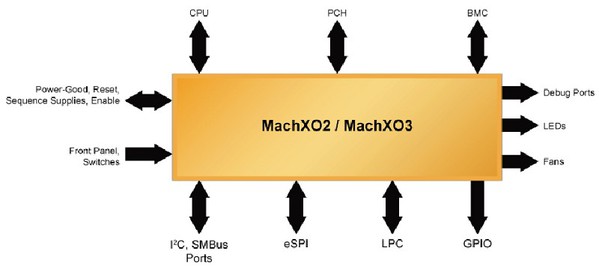

圖2說明MachXO2/3元件適用於實現控制PLD功能,如電源/重定時序、各種類型的串列匯流排(I2C、SPI、eSPI、SGPIO等)、調試埠、LED磁碟機、風扇PWM磁碟機、前板開關感測以及其他一般GPIO功能。 MachXO2/3元件支援1V訊號,可在無需外部GTL收發器的條件下,實現頻外訊號功能整合。當晶片運作時,設計工程師可使用萊迪思套裝軟體中Reveal工具調整控制PLD電路,Reveal於PC上運行,可作為監視和獲取各種狀態的邏輯分析器,藉以控制故障事件。例如,設計工程師透過Reveal調試工具,能夠獲取許多導致故障狀態的事件資訊(包括暫存器、節點和引腳狀態),並將其顯示於PC顯示器,以減少系統電路板排除故障的時間。

| 圖2 : 基於MachXO2/MachXO3的控制PLD |

|

Hitless I/O

控制PLD能夠有效協助設計工程師加速產品上市進程,在有限時間內滿足市場對全新客製硬體的需求。通常,實現控制功能時會產生bug或系統整體結構所需的新功能。此時,常用方法是透過系統更新、系統電源重新通電,於載入經重新編程圖像時針對設計進行修改。此方法需重新設定電源,中斷整個伺服器硬體的運作,並降低可用性。為確保高可用系統不斷運作,MachXO3元件可以維持I/O狀態,同更新配置並初始化新配置,該功能稱為Hitless I/O。

Hitless I/O運作方式(圖3)

為實現零停機更新,MachXO2/MachXO3元件透過「後臺更新」將新配置資料載入至配置快閃記憶體。載入完畢後,「TransFR」會將新PLD圖像檔案自配置快閃記憶體傳遞至PLD配置SRAM。在執行「TransFR」指令的同時會觸發「保持目前狀態」功能,以確保傳遞過程中所有I/O數值皆保持不變。最後,「邏輯初始化」階段,狀態機器將開始重新開啟電源管理並重新設定電源分配,導致電源供電中斷,迫使電路板啟動電源通電過程。

當建立新圖像的狀態機進行初始化,系統該如何使控制電源與其他邏輯訊號輸出保持不變?為使關鍵I/O在初始化過程中保持原有狀態,萊迪思為每個關鍵I/O增加鎖存MUX,不僅在狀態機初始化過程中將輸出作為最終已知狀態,並在初始化過程完成後將輸出控制交給狀態機。該電路能夠使用「Hitless_I/O_Enable」輸入區分正常(通電)啟動和重新配置,可避免正常通電過程中鎖住關鍵輸出的情況。

此新功能的優勢顯而易見,可協助製造商實現即時配置更改,立即修正設計缺陷或為產品增加新功能。同時,也能為產品開發過程提供重要作用,使設計工程師在伺服器安裝過程中,快速調試產品或在調試過程中更改特定產品數值。

PLD具有便利性和成本優勢,成為實現系統設計更新、電源管理、監控和控制關鍵訊號以及基本內務處理功能的理想選擇。

功能二:實現磁碟機熱插拔所需的邏輯功能

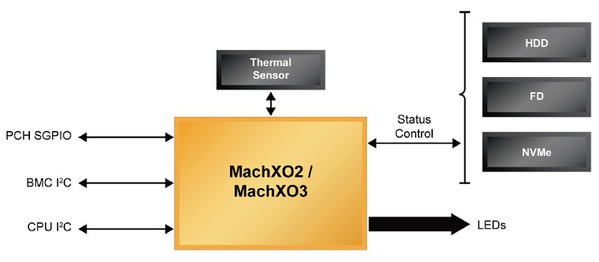

機架式伺服器支援熱插拔HDD/FD/NVMe磁碟機。磁碟機可插至背板,背板透過序列介面(如SGPIO和I2C)與主機板連接。設計工程師可使用MachXO2/3元件整合成圖4的邏輯功能,以實現背板控制。例如,當NVMe磁碟機插入磁碟機插槽時,MachXO2/3元件中的邏輯會自動將狀態和控制訊號發送至I2C匯流排,而非SGPIO匯流排。

| 圖4 : 使用MachXO2/MachXO3 PLD簡化熱插拔磁碟機的背板控制功能 |

|

功能三:主機匯流排配接器電路板的硬體管理

另一個萊迪思MachXO2/3元件的潛在應用為整合主機匯流排配接器控制邏輯。如圖5所示,該解決方案整合SGPIO和其他頻外訊號,管理電源/重定時序和其他PLD功能,包括即時電源故障檢測和狀態保持。設計人員更可在現場即時對MachXO2/3元件實現邏輯增加功能和修復錯誤,透過Hitless I/O功能和I2C介面避免中斷系統運作。

功能四:電壓電流和溫度遙測

一般情況下,系統會不斷針對重要的電源電壓、電路板、元件溫度以及當前負載量進行檢測。為檢測這些數值,伺服器主機板使用模數轉換器IC增加BMC、外部溫度檢測IC、以及電流檢測IC所需的通道數量。此外,該電路板使用I2C緩衝器IC和I2C多工器IC管理遙測I2C匯流排(圖6)。電路板上的DC-DC轉換器是為IC供電,並由控制PLD元件控制。控制PLD更監控來自DC-DC轉換器的「Power-Good」數位訊號。

設計工程師可使用萊迪思ASC(類比感測和控制)元件與控制PLD整合ADC IC和某些溫度感測IC。同時,該元件可將「Enable」和「Power-Good」訊號自控制PLD傳遞至ASC元件,以解放控制PLD上的I/O,使被解放的I/O可整合I2C緩衝器和I2C多工器IC,達到降低遙測電路的總體成本和BOM的目標。另外,透過檢測電源電壓的「Power-Good」狀態與斷電狀態,ASC更有助於提升斷電時序的可靠性,並最大限度地降低電路板擁堵程度。

功能五:Bios和BMC韌體驗證

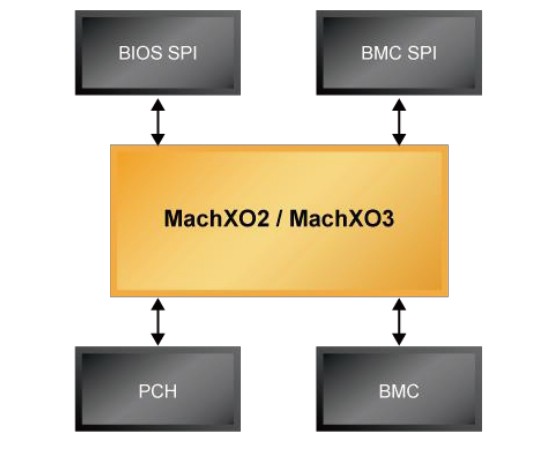

為實現BIOS和BMC韌體驗證,MachXO2/3元件可作為硬體的安全信任根(root-of-trust)(如圖7)。該配置中,此元件可實現橢圓曲線簽名驗證(Elliptic Curve Signature Authentication),以驗證系統BIOS和BMC韌體。當運作中的圖像遭到入侵,此元件亦可管理自動黃金圖像轉換。

| 圖7 : 基於MachXO2/3的解決方案可管理和驗證BIOS與BMC元件 |

|

功能六:PCH上TPM/TCM和單一SPI介面之間的橋接

萊迪思MachXO2/3元件提供各類橋接解決方案。例如,伺服器設計工程師可使用此元件將PCH SPI介面與TPM模組(除了中國以外的國家使用)或TCM模組(中國使用)連接至同一硬體(圖8),該橋接可與各種輸入和輸出的工作頻率相容。

功能七:擴充卡整合多種功能

伺服器通常採用擴充卡增加LED磁碟機、控制以及感測功能,以減少主機板元件連接數量。一般情況下,透過分離邏輯IC實現上述功能會需要不同類型的擴充卡,而每類型的功能皆有所不同。減少所需擴充卡類型的方法之一是將每個擴充卡的功能整合至MachXO2/3 PLD,然後在生產製造過程中簡單修改整合在MachXO2/3元件的邏輯,以客製擴充卡邏輯功能。

功能八:整合多個I2C緩衝器

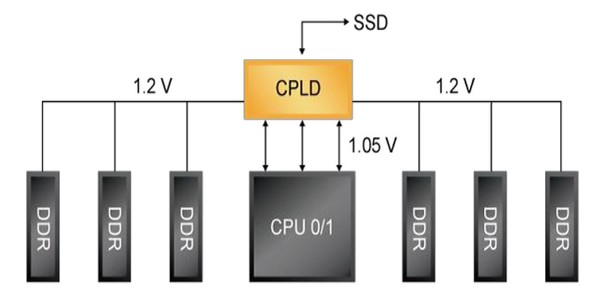

伺服器系統中,CPU透過一對I2C緩衝器與DDR記憶體DIMM進行通訊(圖9),同時,CPU更透過另一個I2C介面監視SSD磁碟機。為將CPU的1.05V I2C介面、1.2V DDR記憶體和3.3V SSD磁碟機進行相互轉換,設計工程師需使用電壓轉換器緩衝器。CPU更使用1.05V邏輯訊號生成多個頻外訊號,這些頻外邏輯訊號會需要與使用2.5V或3.3V訊號介面的其他元件進行通訊,因此,電路板上需採用GTL緩衝器。

低成本MachXO3元件採用小尺寸QFN封裝(5 mm x 5 mm),可實現整合訊號轉換,包括1.05V I2C與其他1.2V、3.3V和2.5V邏輯訊號,以減少電路板面積、BOM以及實現成本的重要目標。

| 圖9 : MachXO2/O3 1V I/O支援I2C緩衝器整合 |

|

總結

目前,伺服器設計工程師如同過去20年的工程師盡可能透過快速、符合經濟效益的方式在電路板上整合更多功能。控制PLD為經常被忽視的重要方法,提供設計工程師將所有控制路徑功能整合至單一可編程元件的簡單方式,同時增加新功能,使設計工程師實現即時設計修改,並透過控制PLD大幅簡化電路板設計和調試。

**刊頭圖(source:SecurityInfoWatch.com)