为了协助客户做好专利??避、完整提出该层电路图找异常点(Defect),宜特推出独家晶片去层技术,将样品如魔术般放大,直接在晶片封装(Package)还存在的情况下进行去层工程,不仅可以大幅提升工程上的良率,完整提出电路图,还可衍生应用在合金PAD、精密IC及其他无法取Die却需要去层的晶片样品上。

|

| /news/2020/03/29/0906268410S.jpg |

宜特观察发现,随着摩尔定律,制程演进至7奈米、5奈米甚至达3奈米,晶片??头的die,几??是接近蚂蚁眼睛大小,一般人眼无法辨识。因此,希??藉由一般的晶片层次去除(delayer)来完整提取die??头每一层的电路,难度是非常高,硬是下去进行一般层次去除(delayer)技术的後果,不只是良率偏低,更可能发生连die都去除到不见遗失的窘境。

宜特说明,以往一般的取die後去层(Delayer)的技术,会因为样品过小等因素,导致die不见或crack而无法进行制程分析;当无法去层(Delayer)到金属层(Metal) M1时,记忆体(memory block)仅能以推测得知,电路模组分析图亦无法完整绘制。

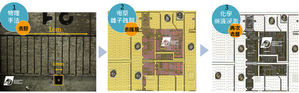

宜特的独家去层技术,共分为三步骤,第一步骤,利用物理手法去除胶体,首先,在晶片封装(Package)还存在的情况下,以物理方式去除晶片die正面多馀的胶体。相较以往须先去除package仅在裸die上去层,此法可在较大的面积/体积上施作,可大幅减少後续去层时die遗失的机率,并保持die面的平整度。

第二步骤则是机台去层,藉由离子蚀刻机,将IC护层(Passivation)与隔绝层(Oxide),用适当叁数以离子蚀刻方式,将不需要的部份移除,藉由宜特独家的控制叁数方式,使得下层金属层(Metal)不受伤。

第三步骤,药液去层,IC护层(Passivation)被去除後,宜特再以药水蚀刻,蚀刻该层需去除的金属层(Metal),即可完整提出电路图。