毫无疑问的,资讯产业正积极于消费性电子化,Comdex Fall(国际电脑展)式微,业者将心力焦点转向CES(消费性电子展),Dell(戴尔)也开始贩售LCD TV(液晶电视),甚至Apple(苹果)改名去掉「Computer」一字等,都是此趋的例证。

资讯产品朝CE化发展,连带的过去在资讯领域的晶片设计业者也必须因应风气,设计出更切合消费性需求及市场的晶片,不过这对晶片业者可说是一大挑战,因为消费性电子领域有别于资讯产业,CE市场变化快速、产品少量多样、产品生命周期短、价格低廉,相对的,过去的资讯产品变化较缓、多量少样、生命周期长、价格较高,虽说两种产业都根基于半导体/电子工程技术,但特性取向却是天差地别。

更简单地说,晶片设计业者必须能提供应用业者更低廉的晶片、更快速提供切合需求与应用的晶片、以及能更灵活弹性运用的晶片,重点就在「成本、速度、弹性」等三项表现,而晶片业者如何因应与满足更高标的要求,本文以下将对此进行更多的讨论。

OTP(一次性烧录)

许多简单的消费性电子内都会使用微控制器(Microcontroller,简称uC),多数微控器的内部具有程式记忆体,记忆体内存放着应用设计者的控制程式,并搭配上微控器外部的控制电路,以此来实现一项应用产品。

重点就在于控制程式,由于CE产品少量多样、市场变化快速且讲究低价,控制程式若是要以Mask ROM的型态放入uC内必须建立光罩,而建立时间须等上数十天,且光罩成本高昂(视制程而定,先进制程达上百万美元之谱),必须有足够的量产规模才足以均摊光罩成本,同时光罩缺乏弹性,倘若程式验证不足而出现错误,或需要调修改版等,都必须重新建立光罩,并再次等待数十天、再次支付百千万以上的光罩花费。

很明显的,Mask ROM作法的漫长等待与CE市场的快速、及时上市相左,最低量产规模的要求也与小量需求相违背,而不能再变动的程式内容也无法满足多样性的需求。

如果不用Mask ROM,而使用可进行多次烧录的EEPROM、Flash Memory记忆体,如此虽然可让uC具有修改弹性,且不用等待数十日的时间,但却有成本增加的麻烦,所以可重复烧录的EEPROM/Flash Memory型uC多用于前期验证试制,或做为投入市场的先期尝试,或用来满足少量的个别专案,但仍难以用于CE的主流市场。

| 《图一 OTP型微控器即是将原有透光窗式的EPROM型微控器,改以非透光的传统封装而成,由于刚出厂的芯片内是全新未用的EPROM,因此仍可进行一次程序刻录,之后无法将数据清除,图为传统使用透光窗封装的微控器:8749(2KB EPROM型的8048微控器)。》 |

|

真正更适合CE市场的作法是OTP(One-Time Programmable)的一次性烧录,OTP是用EPROM记忆体,EPROM特性上允许多次烧录,但需要紫外光的照射以清除原有已写入的程式才能进行令一次的写入,而为了让紫外光能照到EPROM表面必须使用具有透光窗的晶片封装,且此种封装成本较高,而OTP方式是将EPROM以不透光的方式进行封装,如此刚出厂的EPROM仍是空白未曾写入过,仍可写入一次程式。

OTP型的uC在写入次数上不如EEPROM型、Flash型,但在价格上却更低廉,同时也不用等待光罩建立时日与受限于最低量产需求等,是最兼顾「成本、速度、弹性」的选择。

如果各位难以体会箇中特性,或许也可用今日的光碟片来比喻,店头所卖的音乐光碟、影片光碟是在出厂前就已决定内容,无法再改变内容,这如同Mask ROM,而CD-R 、DVD-R/+R等可以烧录一次的光碟则类似OTP,至于可重复烧录的即是CD-RW、DVD-RW/+RW/RAM,很明显的目前用量最大的是CD-R 、DVD-R/+R,因为弹性胜过工厂压制的光碟,同时成本低于可重复烧录的光碟,CD-R、DVD-R/+R的成功原因与OTP相同。

FPGA(现场可程式化逻辑阵列)

与ASIC相较FPGA具有灵活改变电路组态的特点,然相对的它的电路面积利用率较低(意味著成本较高、功效较高)、电路执行速度较慢等,使的FPGA过去很长一段时间只适合用在一些特殊运用,例如特定的专案、大幅且频繁改变电路设计的应用、ASIC设计完工后的试制验证等,除此之外没有太多的应用,也很少用于消费性电子领域。

不过,就特性表现而言,FPGA满足弹性修改变化、快速交付生产等要求,只有在成本上较不合CE市场的需求,但是这样的情形在逐渐在改变,由于光罩成本随先进制程而不断增高,许多ASIC晶片产品已无法像过往般用较高的价格或较大的用量来均摊光罩成本,相对的FPGA却因先进制程而让价格更加低廉,如此致使许多价格与用量较低的晶片放弃开光罩,而改以FPGA方式量产,改以FPGA方式量产的结果是让FPGA的用量增加,量价均摊后使FPGA的成本更加低廉,目前为止FPGA仍持续在此一良性循环的路子中发展。

FPGA价格更低廉后,在CE的「成本、速度、弹性」三取向上都能切合,如今正有愈来愈多的晶片设计者及CE产品设计者舍ASIC而就FPGA。

| 《图二 美国国家半导体公司(National Semiconductor, NS)的COP8SAC家族微控器即有提供一次性刻录用的EPROM型版本,图为COP8SAC微控器与回形针的尺寸比较。(图片来源:National.com)》 |

|

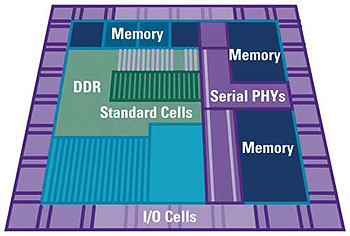

Structured ASIC(结构化ASIC)

Structured ASIC(也称Platform ASIC)可说是ASIC业者的一种修正作法,Structured ASIC依然要开设光罩,然光罩的张数减少,在一颗多层电路的晶片上,部分电路层仍使用光罩式的订制作法,但也有部分电路层改采FPGA的标准制式量产作法,如此使Structured ASIC的各项特性都介于ASIC与FPGA,好处是执行上比FPGA省电、比FPGA快速,缺点则是弹性程度不如FPGA、仍不可免除光罩的花费与时间,只是花费及时间因光罩层数的减少而获得部分缩减。

| 《图三 光罩成本不断高升的结果,使许多中低价位、中低用量的芯片开始改以FPGA型态供货,图为赛灵思(Xilinx,过去称为智霖)公司的FPGA:Virtex-5 LXT家族系列。(图片来源:Xilinx.com)》 |

|

所以,Structured ASIC是介于ASIC与FPGA间的晶片,对晶片设计者而言等于多一项选择,针对CE领域中不同的产品与不同的市场风向,适时使用ASIC、FPGA、或Structured ASIC。或许有人认为特性居中的Structured ASIC将如同OTP一样最具优势,但目前来看似乎相反,由于Structured ASIC是2001、2002年开始的产物,在开发工具、验证程序等方面都不如已成熟运用多年的FPGA与ASIC,因此发展空间仍待观察,最终无论Structured ASIC是否为CE市场接受,短时间都不影响FPGA在CE领域的扩展使用。

| 《图四 由于先进制程的光罩成本呈指数攀升,使芯片设计业者(在此指无晶圆厂的半导体业者,Fabless)开始寻求其他低廉化量产的方案,「结构化ASIC」即是可选方案之一,图为AMIS公司的结构化ASIC:XPressArray-II,XPressArray-II使用0.15um制程、1.5V工作电压,适合取代原属中等密度、高速执行的ASIC应用。(图片来源:AMIS.com)》 |

|

IP(矽智财)

消费性电子除了多样化的特性外,近年来也积极强调多功能,如此也意味着晶片必须整合更多的功效,然更多功效使晶片电路更加复杂,此不单是增加设计心力,包括验证心力也高度攀升,连带使晶片的开发时间、心力、成本也攀升。

如果不增加开发人手,那么开发时间就会增长,使晶片较晚发表并丧失市场获利先机,然增加人手也会增加成本。

关于此,解决的方式多半是向外寻求矽智财电路,由其他业者提供成熟、已完成验证、甚至是已经过市场实证考验的电路,将电路做为新开发设计晶片中的子模块,以此来加速开发时间、减省验证程序。

额外一提的是,矽智财电路又概分成两种型态:软式与硬式,软式智财电路只针对逻辑功效等进行描述,而没有最后真正实制投产的具体电路,反之硬式智财电路则是已完成实制电路的型态。对晶片设计者而言,软、硬各有其优缺点,软式具备较大的再修改空间(与硬式相较),且与晶圆制程技术的相依性低(较具换厂、换制程弹性),缺点是需要比硬体更多的设计与验证心力,相对的硬式的设计与验证需求少于软式,但电路再修改的自主性与修改弹性就较低。

就过去而言,晶片业者多半为了自主性与更佳的整合度,因而偏向选择软式,不过近年来产品及时上市的时间压力愈来愈大,自主弹性修改的主张逐渐在降低,并逐渐选择较无弹性但立即可用的硬式智财电路。

| 《图五 适当运用硅智财电路可加快芯片的开发时程、减省验证心力,而近年来芯片及时上市的压力日增,硅智财的需求也从自主修改性较高的软式硅智财,逐渐转向更快速合用的硬式硅智财,图为ARM公司收并Artisan公司后所推展的外围硅智财电路示意图。(图片来源:ARM.com)》 |

|

Design House(设计代工业者)

除了寻求现成矽智财电路外,如果需要设计的电路功效并没有现成矽智财合用时,且又有上市时间压力,是否有其他的加速、省力法?关于此答案是肯定的,那就是寻求设计代工业者的合作。

「设计代工」言下之意是依据客户的需求来设计电路,之后再将设计完成的电路交付给委托客户,且代工业者多半要对委托内容保密,完成的设计成果也完全归委托业者所有,代工完全是不具名的背后工作。

如前所述,当晶片所含括的功效、设计的构面愈来愈大时,晶片设计业者很难完全用自有的技术团队来完成设计,为了加速开发时间与程序,在使用矽智财电路外,寻求设计代工也是可搭配选用的一种方案。

当然,设计代工业者虽然要对每个委托内容守密,但如果晶片设计业者委托的是新晶片产品中的关键性电路,则难保日后代工业者不会将此次委托设计的技术经验与实务复制运用到其他客户的委托案中,也因为有这一层顾虑,目前委外设计的电路多半不是关键性电路,关键部分多半仍是由自有团队负责。

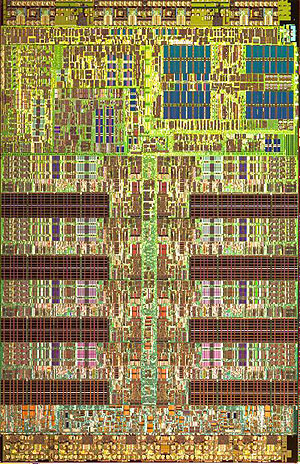

| 《图六 芯片电路的不断庞杂化发展,如今已少有单一业者能独自在时限内完全自主设计,因此逐渐需要借重其他业者的智财电路,以加速整体设计进度并减少验证心力,图为IBM、Sony、Toshiba等共同合作研发的Cell 处理器,该处理器就使用上Transmeta公司的LongRun2省电技术功效的智财电路,以及Rambus公司的高速内存接口智财:XDR,以及高速I/O接口智财电路:FlexIO。(图片来源:www-03.ibm.com)》 |

|

多组团队并行研发

「多组团队并行研发」的作法事实上也行之有年,甚至在过去的资讯用晶片就有例证,例如Intel的x86 CPU就同时有两组设计团队,一组团队专门从事运算架构的变革,另一组团队则专注在效能的提升,两团队交替推出新的CPU,例如A团队推出80386、Pentium,B团队则推出80486(加速型的80386)、Pentium Pro/II(加速型的Pentium)等。

类似的,设计一套晶片组可能需要9个月的时间,但面市之后真正能在市场卖的时间只有6个月,为了解决研发时间长,可卖时间短的问题,同时启动两组以上的研发团队成为不得不的作法。

更多因应CE市场的技术、策略

在上述的各种市场因应策略中,OTP、FPGA、Structured ASIC等是较偏向量产选择面的策略,而外购IP、委托Design House、多组团队并行研发等则偏向设计面的策略,除此之外其实还有许多的变通策略,例如在效能与功耗允许下可借重嵌入式软体来增加晶片的功效弹性,或善用封装技术来降低设计风险,或运用介面标准来增加变换弹性等,在此无法逐一详述。

不过,无论是何种因应策略与技术,都仍然必须合乎前述的「成本、速度、弹性」三项要求,在三种取向上获得最高且最均衡的表现,该项策略与技术才能适用在CE市场中。