隨著科技的進步,市面上各式各樣的電源管理IC如雨後春筍般大量的湧現、迅速的發展,提供給使用者更多應用的範圍與規範,但如何化繁為簡、去蕪存菁,將是考驗一個電源設計工程師最根本議題。

有鑑於此,筆者在此利用所學,將降壓式電源應用設計分為三個章節:DC/DC小訊號穩定與迴路補償、Buck元件的選用以及PCB Layout效率提升一一去探討,並使用AIC2862輕載高效率電源IC,期望設計出一組極至完美的電源模組。

DC/DC小訊號穩定與迴路補償

設計DC/DC轉換器的補償器時,所要補償的對象是DC/DC轉換器的開路小信號轉移函數。而就DC/DC補償器的設計上,主要有Type-I、Type-II以及Type-III三種補償方式,以下就三種補償方式近一步探討。

Type-I補償器是最簡單且最單純的補償方式,可提升低頻增益,但是無法提升相位,圖一為Type-I補償器及其波德圖。而Type-II補償器為Type-I補償器的進化版,將圖一的Type-I補償器增加RF及CCF後,便形成圖二的Type-II補償器。Type-II補償器有一個零點Wz1及一個極點Wp1,可以提升最多90度的相位,另外就原件選擇上,Type-II補償器其CF>>CCF。

最後要介紹Type-III補償器,其可視為Type-II與Type-I的再進化版,圖三為典型的Type-III補償器與其波德圖。就交流訊號而言,Type-II補償器的交流增益為RF/R1,若Type-II補償器的增益RF/R1依然無法滿足需求時,則此時可在RF之處串連CF以提昇交流阻抗;如果要避免高頻的雜訊被放大,則可在RF、CF旁並連一個CCF,以降低高頻增益。

經由加入了RF、CCF的Type-I補償器即為Type-II補償器,其中CF>>CCF,它有起始相位-90度,及最高90度的相位提昇(phase boost)。若要提昇更多相位提昇,可在R1加入R2與C,其中R1>>R3,此時形成Type-III架構。Type-III補償器,它有起始相位-90度及最高達180度的相位提昇。

而就目前DC/DC轉換器的架構,有電路簡單不容易補償的Voltage Mode與電路較複雜容易補償的Current Mode兩種。筆者設計的AIC2862電源模組則是採用Current Mode的轉換器架構,使用在較小電流、內建Power MOS的電源模組。

至於補償器的選擇上,小電流Current Mode的降壓轉換器,大部份還是採用Type-II補償器,原因在於電路簡單、容易實現,同時可以補償起始相位-90度,至最高90度的相位提昇。

圖四為AIC2862電路補償波德圖,其中DC/DC轉換器開迴路,將會產生受輸出負載與輸出電容所影響的極點(FP1),以及輸出電容所產生的ESR零點(FESR)。

利用Type-II補償器的方式將DC/DC開迴路轉換器,再補入一個極點(FP2)與一個零點(FZ1),設計上筆者建議補償器的零點盡量往低頻設計,補償器的極點則往高頻設計,其目的在使完整閉迴路DC/DC轉換器,可以盡可能工作在穩定(Stable)條件。

Buck元件的選用

元件的選用上,AIC2862已將大部分的元件放入IC中,設計上只要考慮如何選用較佳的電感、適當的輸出入電容以及分壓電阻設計的輸出電壓。當然,如果注重電源啟動(Start-up)升壓瞬間的品質,我們還會特別選定緩啟動(Soft-Start)的電容。

圖五為AIC2862正常情形下的應用線路,其電路架購可工作在PWM與PSM兩種模式:輕載下,可以工作於輕載高效率的省電模式(Pulse Skip Modulation;PSM);重載下的定頻模式(Pulse Width Modulation;PWM),可以高效率提供負載使用。

PCB Layout效率提升

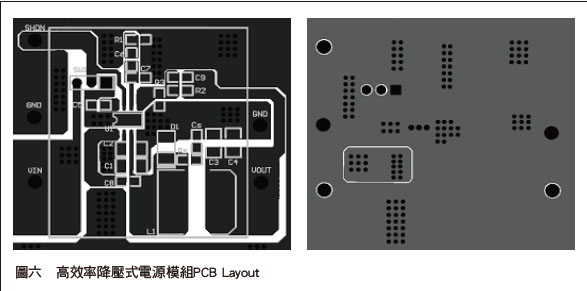

PCB Loyout在應用設計上是很重要的,如何讓電源模組在有限的PCB版子上達到最佳效率,往往考驗設計者的功力與經驗。首先,在製作這個PCB電路設計技巧上,要將大電流(High di/dt)迴路的元件先擺上,以利大電流迴路的佈線為最短距離,同時佈線要寬,以提昇類比式降壓穩壓電路的效率。至於接地面的多個導孔並聯可以有效降低PCB銅板上的電感與電阻性,而使整個接地面(Ground)具有完整性。

| 《圖六 高效率降壓式電源模組PCB Layout》 |

|

如圖六為整個降壓式電源模組PCB Layout,設計上將其列為以下重點,希望幫助讀者快速的去檢查自己的降壓式電源模組,以利設計出更好、效率極佳的降壓式電源模組。

- (1) 輸入電容必需與IC VIN輸入端和接地面(Ground),形成一極短的閉迴路,以防止整個電源模組輸入端,較大的輸入鏈波與雜訊(Ripple and Noise)流入IC,造成IC誤動作與電壓不穩。

- (2) 輸出迴路上,請將大電流路徑的電感與IC內部Power MOS放近一點;如果在較大的電流輸出情形下,也可以放置蕭特基二極體(Schottky Diode;D1),以降低內部Power MOS的RDS(ON)以及提升電流放電路徑,當然,這顆Diode Layout上必須與IC內部Power MOS和電感擺放近一點。

- (3) IC的FB接腳直接連接至回授電阻,這個回授路徑必須遠離雜訊源,以確保輸出電壓不受其他訊號干擾。

- (4) 整個接地面(Ground)需要與IC的GND接腳形成一個大面積、完整迴路,以預防及防止電路的雜訊,由輸入的旁路電容Cover進入電源模組的接地面。

- (5) 大電流路徑必須保持短而且銅線面較大,PCB鋪銅路徑必須保持順暢,以防止影響到其他訊號源。

文至於此,您心動了嗎?要不要自己設計一個簡單又便宜高效率降壓式電源電路,那就著手設計看看吧!