英飛凌在 2013 年 2 月推出於奧地利維拉赫 (Villach) 廠全新 12吋生產線製造 的首批CoolMOS 系列產品。英飛凌為此進行超過三年的密集研發活動,並與全歐洲各個領域的合作夥伴合作,其中包括製程技術、生產技術,以及進階功率技術 (以 12吋晶圓為基礎) 的處理和自動化。英飛凌是全球第一家以 12吋薄晶圓上生產功率半導體的公司。12吋薄晶圓的直徑比標準的 8 吋晶圓更大,每片晶圓所生產的晶片數是後者的兩倍半。英飛凌投入大量資本及工程人力,大幅提升先進功率半導體裝置的產能,未來將能達到永續支援市場的目標。

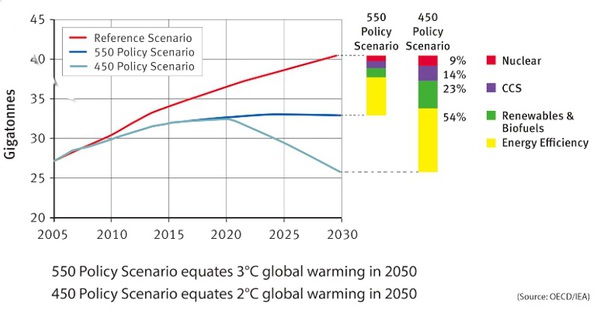

電力電子在協助全球朝向更有效運用能源的方向發展中扮演重要角色 (請參閱圖 1 的 OECD 情境)。效率隨著世代發展逐漸提升,轉換效能將成為減少排放溫室氣體的關鍵推動因素。

| 圖一 : 不同情境下的 CO2 減量。提升能源效率可獲得最高的 CO2 減量效果。 |

|

電力在全球能源組合之中的比例日漸增加,這將進一步提升電力電子的重要性。其中最重要的部分,就是電力電子將在協助大幅減少主要能源來源及能源終端使用者之間大量的能源損耗上,扮演不可或缺的角色。目前市場上甚至出現高達 90% 的損耗情形,而 50% 的損耗仍是司空見慣。圖 2 說明從第一次轉換為電力開始到配送過程,乃至於最終供電至終端使用者設備的損耗情形。現代的功率半導體裝置所扮演的關鍵角色,便是協助推動電力電子邁向更優異的效能及更低的系統成本,藉此支援電力電子進一步擴展至電力轉換及控制的更多層面。

如果我們更深入探討各種電力應用的節能潛力,可以發現馬達控制應用消耗了高達 40%的電力,致為關鍵。該應用的主要議題是由單純的開/關控制轉換為變速馬達,除了能節省大量能源以外,也能減少產生的噪音,並創造更舒適的環境 (例如空調應用)。另一項重點領域為照明應用,大約佔了 15% 的電力消耗。就照明而言,主要議題在於將白熾燈泡及鐵磁式安定器 (目前已遭歐盟國家普遍禁用) 轉換為 LED 照明及更精密的電子式安定器,協助推動節省能源。電力電子提供合適的高壓 MOSFET、驅動器及控制器,支援上述各項應用的過渡轉換。

最後則是資料中心及 RF 電信基地台的電力供應。網際網路存取及高速資料交換廣泛存在於現代的生活型態中,具有不可或缺的地位。業界已於「電腦產業氣候行動計畫」(Computing Climate Initiative) 採取各項主要步驟,設定更具挑戰性的效率目標 (目前以鈦金級為最高標準),未來實施後將持續增加在新 IT 設備的應用比例。這裡的關鍵技術主要在於高壓及低壓 MOSFET,範圍從 AC 前端的 600V 裝置,乃至於負載點轉換器的 25V 裝置。

強勁成長的應用領域,例如:太陽光電 (預估於 2016 年可達到 60GW 的新安裝設備) 及電動車,將進一步帶動功率半導體產品的全球需求。

12吋晶圓功率技術

英飛凌因此成為全球第一家肩負以 12吋晶圓製造先進功率產品的功率半導體公司。英飛凌為此投入大量資本及工程資源,將鞏固公司在業界的領導地位,在持續成長的市場中提供穩定永續的產能。英飛凌結合三年以上的密集研究成果,以及德國維拉赫 (Villach) 和德勒斯登 (Dresden) 等工廠的製造專業,於 2013 年 2 月成功以12吋薄晶圓技術生產CoolMOS 功率半導體,完成首批客戶出貨。

英飛凌參與 EPT300 專案 –「實現在 12吋晶圓的功率技術(Enabling Power Technologies on 300mm wafers)」;這是歐洲奈米科技方案諮詢委員會 (ENIAC Joint Undertaking) 的專案。在 EPT300 的協助下,由歐洲半導體製造業及歐洲設備與材料業 23 家廠商所組成的聯盟,實現全球首創專用於功率產品生產的 12吋功率半導體製程生產線,讓歐洲擁有先進的製造能力。

明確區分電力電子製造與傳統 CMOS 製造技術之差異相當重要。電力電子的產品特性非常不同,因此必須採用不同的,且過去未曾使用於12吋晶圓的材料及製程。全球目前現有的先進功率半導體製造 (MOSFET、IGBT 及功率 IC 技術),仰賴 6吋及 8 吋晶圓技術。因此目前這類應用的製造設備都專為這這些晶圓尺寸所設計。 要發展12吋晶圓製造功率半導體的專用技術,需要克服過去無法解決的製造難題。

為了克服這項限制,EPT300 專案的目標就是針對下列目標提供解決方案:

‧ 在晶圓廠環境以 1:1 的轉換方式在 12吋晶圓製造首批 MOSFET 產品,充分證明新基板材料能夠符合應用需求。

‧ 提供更優異的設備及全新製程技術。

‧ 證明在生產線上量產的製造能力,並提出穩定及可接受的良率數據。

‧ 針對功率半導體技術的未來發展樹立技術基礎。

功率半導體的製造是高度複雜的作業,包括許多製程步驟,需要深入的材料知識與專業技術。第一項先決條件是取得適當原料和生產設備。因此最初的製造步驟需要處理一系列步驟,以便建立裝置的有效區域。後續步驟則專門處理半導體後端生產,其中包括薄層金屬化及一組晶圓背面製程步驟 (這是製造功率半導體的必要步驟)。其中一項關鍵製程就是晶圓薄化,因為功率裝置厚度對其效能有很大影響。英飛凌在薄晶圓製造領域扮演業界領航角色,主要用於生產 IGBT 產品系列,例如效能無可比擬的 TRENCHSTOP IGBT。不過晶圓薄化也將大幅提升低壓 MOSFET 的效能,亦應用於英飛凌的 CoolMOS 技術。

邁向 12吋製程中的挑戰

在 12吋晶圓實現功率技術的首要步驟,就是必須「移轉」現有的 8 吋技術。不過這絕不只是移轉而已,因為專案開始時並沒有適合 12吋使用的功率基本材料。此外部分功率技術設備也沒有適用於 12吋的設備。在現實情況下,這仍是充滿挑戰的研發專案,不能稱為「移轉」。

因此英飛凌必須證明已於 8 吋供應的產品,能以 1:1 效能轉換的方式進行移轉,並且要證明裝置能夠提供相同或更優異的效能。

除此之外,在 12吋晶圓開發及生產功率裝置,還有三項主要挑戰:

1. 以符合成本效益的方式取得 12吋的功率基板 (例如英飛凌修改 p 型標準基板,並由基板供應商開發 12吋的功率基板)

2. 調整 12吋 CMOS 設備進行功率製程 (例如晶圓正面及背面製程與製程、厚層製程、高溫製程,當然還包括薄晶圓製程及混合型機台製程)

3. 適合 12吋功率技術的薄晶圓技術 (調整英飛凌的 8 吋薄晶圓技術應用於 12吋 (最低至 40 微米),實現 20 微米的矽厚度)

12吋晶圓功率技術基板材料之挑戰

目前 CMOS 產品採 12吋基板生產製造,以更低的成本實現更優異的晶片效能。更小的尺寸 (<45 奈米)帶來效能,晶片及晶圓的大小亦決定了每個裝置的成本。不過在考慮需求量的前提下,可用基板材料已針對這些 CMOS 技術最佳化,並且不一定能夠滿足功率技術在基板材料的特定需求。

CMOS 技術使用 p 型基板 (大多為硼),而功率技術則需要 n 型 (一般為磷摻雜) 基板。此外所需的摻雜程度及裝置厚度,則主要取決於所需的崩潰電壓,在專案中產生另一個需要解決的技術差異。

在 CMOS 技術中,唯一有效的電力區域位於表面,但是在大部分的功率技術中,則是整個晶片體積,都讓電流從裝置頂端流動至底部。因此基板的污染和雜質,對裝置效能的影響遠超過 CMOS 結構。

即使是現在,8 吋功率技術的專用原料,仍比進階 CMOS 製程的標準材料昂貴許多。因此必須針對基板尋找符合成本效益的解決方案,維持 12吋直徑晶圓預期的成本優勢。

設備的挑戰

28奈米的12吋 CMOS 技術佔半導體市場的比例較高,應用於 DRAM、Flash 記憶體,以及個人電腦、筆記型電腦和智慧型手機的 CPU 等大眾產品。於此同時,功率技術迅速成長的發展潛力,也讓上述應用對於 12吋技術產生需求。不過即使目前市面上半導體生產的主流設備,都可供 12吋晶圓使用,但主流 CMOS 工具與功率技術所需要的特殊設備之間仍然存在重大差異。

相較於 CMOS 製程,製造節能功率半導體需要使用「三維製程」(在晶片上進行正面製程、背面製程及垂直製程 (溝槽))、厚層製程、高溫製程,當然還有薄晶圓技術。

英飛凌的高壓 MOSFET 是以超接面技術為基礎;這項技術可大幅減少每個晶片區域的導通電阻,並克服眾所周知的晶片限制。雖然導通電阻受益於持續提升的漂移區摻雜程度,但崩潰電壓則需要三維結構 p 及 n 摻雜區域的完美補償,涵蓋各個裝置、整個晶圓,乃至於每個晶圓甚至每批晶圓。英飛凌分別投入大量資源處理生產線內控制方法和精密的設備操作及維護,以便將 CoolMOS 技術成功轉移至 12吋。

其他功率技術挑戰則是高溫熔爐製程。12吋技術的標準設備能夠處理高達 ~1000°C 的溫度,功率技術則需要最高 ~1200°C 。因此英飛凌針對熔爐硬體進行大型研究,以滿足這些高難度需求。其中包括加熱系統及精密的溫度控制器,以及特殊調整的石英製品技術。

彈性使用能夠處理 8 吋及 12吋晶圓的設備 (混合型機台),是歐洲廠房製造具備高度彈性及成本競爭力的關鍵所在。這些混合型機台的另一項重要層面,就是能夠在相同設備提供相同的 8 吋參考。

| 圖四 : 彈性使用設備處理 8 吋及 12吋是關鍵所在 |

|

薄晶圓製造之挑戰

如前所述,功率產品會出現垂直電流,由前端載入電流通往裝置後端。為了實現最佳效能,功率裝置的最終厚度非常重要。英飛凌的 IGBT 技術仰賴非常淺的 p 摻雜後端植入,以正確控制其射極效率,並結合較深的 n 摻雜場終止層,以及頂端溝槽結構,精準打造電場分布 (因此具備阻斷能力) 及載波外型。任何多餘的裝置厚度,都可能增加順向飽和電壓及截流損耗,影響 IGBT 的兩項關鍵效能指標。下圖顯示個別 IGBT 電壓類別未來的晶圓厚度目標。

就功率技術的 6吋及 8 吋晶圓而言,目前最先進的晶圓厚度為 70 微米。這代表處理這類薄晶圓時因其易碎性而極具挑戰。使用 12吋晶圓使這項挑戰更為艱鉅,因為趨勢顯示晶圓厚度將再度降低,最終晶圓厚度甚至可達 20 微米。

薄晶圓處理技術亦嘉惠英飛凌其他如低壓 MOSFET 等產品,可以減少剩餘基板厚度的導通電阻及熱阻。

英飛凌已於 12吋晶圓製造成功實作功率 MOSFET 技術。原料供應及薄晶圓製造的相關挑戰已經解決。超接面裝置和低壓 MOSFET 的特定議題,也已成功獲得證明。

以上成果將使英飛凌繼續居於領先地位,為市場對功率半導體持續增加的需求提供永續產能。

(本文作者皆任職於英飛凌科技)