半導體設計的演進,由最早期的電晶體層次進化到ASIC階段的閘層次,已使得gate-array技術大幅提昇了設計生產力。在這之後,製程技術又歷經了數年的進步,又更加強化了另一個設計層面需求,以求取更大的生產力變化。這個需求,即是目前晶片業界所慣稱的虛擬元件(Virtual Component)系統單晶片(System-On a Chip;SOC)設計平台。這個平台是由智慧財(IP)觀念中的可重複使用虛擬元件(VC)所推動,並以深次微米(DSM)晶片實現的高階設計環境。

為了統一SOC的定義,於1996年成立的Virtual Socket Interface(VSI)聯盟,簡稱VSIA,孕育出了一套設計及整合可重複使用IP區塊的開發及辨識標準,將系統晶片定義為一個「高度整合的元件,又可視為System-on-silicon、System-LSI、System-ASIC及System-level integration等元件」。而晶片設計界則將整合數個功能元件的單一完整晶片或晶片組通稱為SOC元件。

(表一)所示為各種應電產品推動半導體製程技術及系統晶片的需求/時間表。典型的設計模式已由過去的Top-Down模式演變為數個獨立的設計團隊,個自開發不同的功能方塊(如Core-logic、Memory、Graphic、Network等),再透過系統組合的程序完成最後的產品。

在此前提之下,當VSIA正大力培植SOC產業的同時,大部份的半導體公司都同意重複使用的IP將是未來繼續生存的要素。此外,這些大公司也都相信它們目前所擁有的技術,已足夠進行公司間內部的IP重利用設計工作。不過實際的結果卻顯示,即使是一個IP分界及定義非常明確的單一公司,仍然無法精密地將IP重複使用於不同的工具、製程及測試環境之內。在正確地應用IP之前,建立完整的裝置系統以明確地表達IP開創 、取用、整合、保護、價值、辨識、目標及支援等特性,才能有效地提昇設計的生產力。

IP重複使用瓶頸與生產力評估

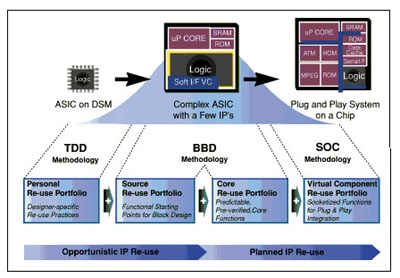

IP重複使用的瓶頸可由四個特徵進行分析、即取存、運用、設計流程及生產力評估。(圖一)將重複使用的模式對映至TDD(時序驅動設計)、BBD(區塊基礎設計)及SOC設計流程等三種演化過程。在此過程中,需逐步加入更多取存、預先審核及設計流程等工作量,但卻可換得躍進式的生產力及運用性提昇幅度。在早期IP成熟度不高的年代,重用的時機是在設計實作的階段;然而當重用成為設計的慣例後,便須在產品規劃階段即開始著手考量。

| 《圖一 IP重利用的技術演進<時機vs.計劃階段>》 |

|

個人的IP重利用模式

在傳統的ASIC及時序驅動設計(TDD)環境中,重複利用的取存都以經驗為準則,運用範圍也止於個人或小組的設計重行使用。其它人若需使用此一電路,只能求助於原始的設計人。與有組織的IP架構相比較,這種方法完全設有特定的規則可遵循。請參閱(表二)。

外部提供的IP重利用模式

以區塊為基礎的設計模式,促使由外部尋找IP重利用設計的機會大幅增加。外部供應IP重利用設計的模式,由於可馬上取得既有的RTL或電路描敘檔案,因此可快速地對其進行修改,以滿足自有系統的要求而加速設計時效。這種方法的效益評估非常難以量化方式來表達,最主要的關鍵在於取得之IP是否具有完整的說明文件,是否滿足主系統設定的限定條件,是否配有足夠的測試標竿,及主系統是否有足夠開放的架構,以採用現存的設計等主客觀環境的配合程度。對許多大型半導體公司而言,最大的障礙應是來自於資訊的取得與其完整程度(表三)。

核心功能(Core)重利用模式

當設計部門已成熟到採用以區塊為基礎的階層式設計流程後,IP重利用的模式即可進一步改良。改良的方式是透過採用矽晶片上實際的區塊(包括晶片尺寸、時序、接腳間距及功率等數據)資訊而達成。這種設計方法具有下列特點:

- 1.更多的實際的(硬式)區塊出現在系統內。

- 2.以特定技術元件庫表示的可重利用電路描述檔。

- 3.檢測進入重利用IP資料庫的限制條件。

- 4.記錄曾被使用或重利用的方塊資料。

- 5.整理一套曾被整合或應用於特定製程的外部供應IP區塊清單。

正確地說,上述的改進同時升級了IP重用內容的品質與取存的便利性。成熟的區塊架構設計流程,重利用及管理市場壓力等因素相互結合後,實際上打破了IP重利用的非技術性障礙。愈來愈多的大型複雜區塊以GDS Ⅱ硬式核心(Hard Core)的型態出現。設計部門也開始劃分為系統設計、晶片整合及區塊管理等細部團隊。測試指標也必須從最頂層(Top)執行,而非各自對不同區塊獨立開發(表四)。

一旦設計流程邁入成熟階段,生產力便自然地提高,而可預測度也隨之增加。此時,IP重利用市場的擴增主要是來自較佳的核心區塊特性、大眾化的取存管道、更好的品質及IP種類數目的增加。這也意味著整體設計中的重複利用IP百分比與日增加,因而簡化了設計程序。

虛擬元件(Virtual Component)重用模式

由IP轉換到虛擬元件的階段,將會由於個別的管理及整合分工而獲致最大的生產力效益。虛擬元件(VC)是一群針對特定應用系統環境而預先定義、預先驗証並塑作的區塊元件。虛擬系統設計可創造出一群適用於特殊市場的商用等能,功率、匯流排、可靠度、可生產率、成本及I/O等元件。實際而言,虛擬元件(VC)的重利用模式是針對一個整合及生產環境,作專門的最佳化處理,包含工具及製程兩方面。核心區塊的IP重利用模式可增加1.5至3倍生產力,但虛擬元件IP重利用模式卻能增加10倍的生產力,差別極大。除此之外,由於虛擬元件已針對技術及生產條件做過個別應用領域的最佳化整理,因此為了搶先推出市場而損失的晶片尺寸及性能效益也會減少許多(表五)。

由傳統晶片設計方式轉移至SOC環境的先決條件是:IP重利用時不會產品及時上市及晶片成本的優勢。現有的以電路合成為中心的設計流程只能處理軟式(Soft)的RTL層級IP區塊,還需附加足夠的支援、文件整理及取存機制,才有機會把設計生產力提高1.5至3倍,代價確實很大。但在今日,系統整合晶片至少需要10倍以上的生產力,才足夠滿足產品上市的時程壓力。因此以設計架構為中心的模式,不但能重複運用虛擬元件,又不會改變原有設計環境,應是一種最佳的升級考量。