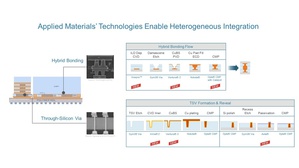

面對當前國際半導體市場競爭加劇,應用材料公司也趁勢推出新式材料、技術和系統,將協助晶片製造商運用混合鍵合(hybrid bonding)及矽穿孔(TSV)技術,將小晶片整合至先進2.5D和3D封裝中,既提高其效能和可靠性,也擴大了應材在異質整合(heterogeneous integration, HI)領域領先業界的技術範疇。

|

| 應用材料公司最新推出精進異質晶片整合方案,幫助晶片製造商運用混合鍵合及矽穿孔技術 |

應材表示,該公司目前身為異質整合(HI)技術最大供應商,提供經過優化的晶片製造系統,包括蝕刻(ETCH)、物理氣相沉積(PVD)、化學氣相沉積(CVD)、電鍍(ECD)、化學機械研磨(CMP)、退火與表面處理。

如今透過混合鍵合及矽穿孔等全新攻略的核心要件技術,可通過直接銅對銅鍵合來連接晶片對晶圓和晶圓對晶圓,在更小的空間內堆疊更多導線,縮短訊號傳輸的距離,進而提高生產率(throughput)和功率。使其組合後的整體成為單一產品的形式來運作,協助半導體業者將各種功能、技術節點和尺寸的小晶片結合到先進封裝中,解決產業正受到高效能運算(HPC)和人工智慧(AI)等應用對電晶體的需求以指數級速度成長,而傳統的2D微縮速度趨緩且變得更加昂貴等挑戰。

應用材料公司半導體產品事業群副總裁暨HI、ICAPS(物聯網、通訊、汽車、電源和感測器)和磊晶技術部門總經理桑德‧瑞馬摩西(Sundar Ramamurthy)博士表示:「如今異質整合技術正快速發展,起因於傳統2D微縮已不能同時改進效能、功率和成本,而異質整合則能協助晶片和系統公司突破此一限制,可以在2.5D和3D結構中配置封裝更多的電晶體和導線,讓晶片製造商得以全新方式改善晶片的功率、效能,降低功耗、單位面積成本與上市時間(PPACt)。」

因此提供的「Insepra SiCN」沉積系統,擴展了應材領先業界的混合鍵合產品組合,使用一種新的矽碳氮 (SiCN)材料,提供產業中最高的介電鍵合強度,並具有優異的銅擴散阻障性。更強的介電鍵合提供了設計人員所需的結構穩定性,能夠在給定區域內整合更多銅對銅互連,從而降低功耗並提高元件效能。

「Catalyst CMP」解決方案幫助客戶控制「表面凹陷」(dishing)量,亦即在後續高溫退火作業步驟中將鍵合的兩個表面上的銅材料預留凹陷。過多的CMP凹陷在銅墊片的頂部表面造成不必要的金屬損失,進而產生空氣間隙並降低銅對銅鍵合的真確度(fidelity)和強度。應材的Catalyst解決方案屬於動態溫度控制技術,可以控制表面凹陷、提高生產率。

至於已在大規模量產中使用超過十年的矽穿孔(TSV)技術,則是用於精確連接堆疊晶片的垂直導線,透過在矽晶片中蝕刻溝槽,然後填充絕緣襯墊和金屬導線來完成 TSV。隨著設計人員繼續將更多的邏輯、記憶體和特殊功能晶片整合到先進的2.5D和3D封裝中,每個封裝中的TSV互連導線數量已從幾百個擴展到數千個。

為整合更多的互連導線並容納更高的晶片堆疊,設計人員需將矽穿孔變得更窄、更高,造成沉積均勻性改變,因而降低了效能,也增加了電阻和功耗。應材推出的介電質和金屬沉積新技術,提供更高的矽穿孔深寬比,協助晶片製造商實現整合、效能和功率的目標;新的沉積系統也能提升運用矽穿孔技術所堆疊晶片的密度、效能、品質和成本

其中包括:「ProducerR InVia 2 CVD」系統是新的化學氣相沉積(CVD)製程,在不斷增加的各種TSV應用,為需要極端深寬比的邏輯和記憶體客戶,提供介電襯墊均勻性和電氣特性穩定性(robust)。該系統使用專有的原處(in-situ)沉積製程,為高深寬比的TSV提供了優異的一致性;其生產率也高於原子層沉積(ALD)技術,因此降低了TSV的每片晶圓的成本,並且進一步促進擴展其導入。

「Endura Ventura 2 PVD」物理氣相沉積系統提供高達20:1的深寬比,使其廣獲採用的前代方案能延伸到TSV應用中,提高對金屬TSV導線沉積的控制並確保能完全填充,以實現高電氣性能和可靠性。新的TSV PVD製程已經與Producer InVia 2 CVD製程完成協同最佳化,為客戶提供了解決最具挑戰性TSV設計的成熟解決方案,並獲得所有先進的晶圓代工/邏輯晶片製造商和所有主要DRAM生產商所採用。

應材最新一代的「Producer Avila PECVD」電漿輔助化學氣相沉積系統,是針對TSV的導孔「露出」(reveal)製程應用而設計的。在TSV的製程中,晶圓與暫時的玻璃或晶矽載體暫時性鍵合,然後透過CMP和蝕刻進行薄化,直至觸及TSV。完成TSV露出步驟之後,運用等離子增強的(plasma-enhanced)CVD技術沉積一個薄的介電層,藉此將TSV之間以電氣相互隔離。如果PECVD製程產生的熱量超過約200°C,脆弱的暫時性鍵合黏著層可能會受損,導致成本高昂的晶圓良率損失。應材的Producer Avila PECVD系統,能以超低溫、高速產生高品質的介電薄膜,滿足TSV品質和成本所要求的低熱量積存(thermal budgets)和高生產力要求。