英特尔是首家在类产品的测试晶片上实作背部供电的公司,达成推动世界进入下个运算时代所需的效能。英特尔领先业界的晶片背部供电解决方案━PowerVia,将於2024上半年在Intel 20A制程节点推出。藉由将电源??路移至晶圆的背面,解决因晶片面积微缩而日益严重的互连瓶颈问题。

|

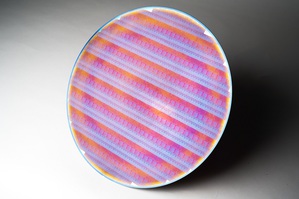

| 代号「Blue Sky Creek」测试晶片的完整晶圆。 |

英特尔技术开发??总裁Ben Sell指出,PowerVia是英特尔『4年5个节点』策略以及迈向2030年达成单一封装内含1兆个电晶体过程中的重要里程碑。使用试验性的制程节点及随後的测试晶片,让英特尔降低背部供电对於领先制程节点的风险,并让英特尔在晶片背部供电导入市场方面,领先竞争对手一个节点世代。

英特尔将PowerVia从电晶体的开发中分离出来,以确保实作於Intel 20A和Intel 18A制程节点晶片时已准备就绪。与Intel 20A的RibbonFET整合之前,PowerVia已在其内部测试节点进行测试和除错,确认该技术具备良好的功能性。制造该测试晶片并测试之後,PowerVia已被证实能够显着且有效地利用晶片资源,单元利用率超过90%,让晶片设计人员能够在产品中提升效能和效率。

PowerVia遥遥领先竞争对手的晶片背部供电解决方案,并为包含英特尔晶圆代工服务(IFS)客户在内的晶片设计人员,在提升宝贵的能源与效能方面,提供一条更快速的途径。英特尔在导入业界最关键创新技术有着悠远的历史,例如应变矽、Hi-K金属闸极和FinFET,藉以持续推动摩尔定律发展。随着PowerVia和RibbonFET环绕式闸极(gate-all-around)技术将於2024年问世,英特尔持续在晶片设计和制程创新引领业界。

PowerVia为晶片设计人员首次解决日益严重的互连瓶颈问题。随着人工智慧和电脑图形在内等领域的应用不断增加,需要更小、更密集和更强大的电晶体来满足不断成长中的运算要求。过去数十年来直至今日,连接电晶体的电源线和讯号线架构总是在争夺相同的资源。藉由分离这两者,能够提升晶片的效能和能源效率,为客户提供更好的结果。背部供电对於电晶体微缩十分重要,让晶片设计人员能够在毋须牺牲资源的情况下提升电晶体密度,提供相较过往更高的功率和效率。

Intel 20A和Intel 18A均会导入PowerVia背部供电技术和RibbonFET环绕式闸极技术。作为一款全新的电晶体电源传输方式,背部供电实作也向散热和除错设计提出新的挑战。

藉由将PowerVia的开发与RibbonFET脱钩,英特尔可以迅速地解决这些挑战,确保在Intel 20A和18A制程节点晶片实作时已做好万全的准备。英特尔工程师开发出避免散热问题的缓和技术,除错小组也发展出新技术,确保新款设计结构能够被正确除错。实作测试的结果显示出稳定的良率和可靠性指标,於整合RibbonFET架构之前就展现出该技术优秀的内在价值。

该测试还利用EUV(极紫外光)微影的设计规则,其结果包含在晶片大面积上达成超过90%的标准单元利用率,提升单元密度同时降低成本。本测试还显示出平台电压下降幅度改善超过30%以及6%的频率优势。英特尔也迎合逻辑单元微缩随之而来的高功率密度,在PowerVia测试晶片达成所需散热特性。

於VLSI举行期间公开的第三篇论文,英特尔技术专家Mauro Kobrinsky将解释英特尔对於部署更先进PowerVia方法的研究,例如在晶圆的正面或是背面同时实现讯号和电源传输。

领先业界提供客户PowerVia并在未来持续创新,反映出英特尔长期以来身为首位将半导体创新带往市场,并不断创新的传统。