厚翼科技(HOY Technologies,简称 HOY)日前发布最新「记忆体测试电路开发环境-BARINS 3.0」,开放使用者自定义Cell Library(元件库)里Cell的行为。让BRAINS学习如果遇到使用者定义的Cell行为,决定记忆体时钟(Memory Clock)由哪一个时钟路径提供,可大幅降低使用者比对记忆体落在时钟域(Clock Domain)的比对时间,并提供最隹化的记忆体测试电路、大幅缩短测试时间,降低测试费用。

|

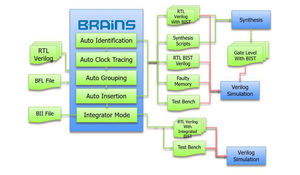

| BRAINS操作流程图 |

深度学习(deep learning)是在人工智慧(Artificial Intelligence, AI)领域中的一个新兴话题,也是成长快速的领域,而AI将引发记忆体测试需求,现已有许多晶片供应商对深度学习的兴趣不断增加,意味着系统单晶片(SoC)对於记忆体的需求量将会大增,进而带动记忆体测试需求。

厚翼科技最新「记忆体测试电路开发环境-BARINS 3.0」内建数个已知Gate Cell的行为,在Auto Identification後段,进入Auto Clock Tracing之前,BRAINS会开始建立所有Memory的Hierarchy并找出共同的Top Hierarchy。

对照其他记忆体测试开发工具而言找出共同的测试开发工具而言找出共同的Top Hierarchy在复杂的电路中会花费很长的执行时间,以BRAINS3.0而言,但若电路设计没有大幅更改,之後就可直接使用第一次搜寻的结果,可节省三倍的执行时间。