PCI Express (PCIe)已經從 1.0 版發展到 5.0 版,預計將在 2021 年發表 6.0 版,每個版本都維持向下相容性,能與過往產品共存。現有規格並未指定失效日期,設備設計人員需要晶片供應商支援每一代產品。

PCI Express 與頻寬需求

PCI Express(PCIe)

當成一種連接運算、嵌入式及自訂主機處理器,以及乙太網路連接埠、USB 連接埠、視訊卡及儲存裝置等「終端」周邊裝置的方式,已經成為高效能互連技術的參考基準。PCIe 利用高速串列通訊技術,提供高效率的點對點連接,還提高通道數量和訊號速率,提供具擴充能力的介面頻寬。

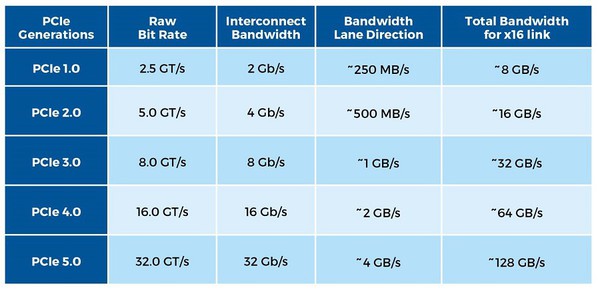

2002年發佈的 PCIe 1.0 規格,運作速度為每秒 2.5 GT/s,提供 8GByte/s 的總 x16 介面頻寬。2006年發布第二代 PCIe 2.0 規格後,頻寬成長一倍;2010 年推出的 PCIe 3.0 規格將頻寬提高到32GByte/s,以滿足現代各項重要產品應用項目不斷成長的需求,包括高階個人電腦、遊戲、企業運算及網路。

近期社群媒體及視訊串流等雲端服務迅速普及,對大規模資料中心內的高速連接技術提出更高的全新要求。

如今物聯網時代的到來,安裝在整個智慧城市及基礎設施、智慧工廠和其他工業資產、商業和住宅建築物,還有用於健身和醫療追蹤之穿戴式裝置上的連網感測器,將產生巨量資料,供超大規模的資料中心擷取、儲存、處理與分析。這些力量正在推動對新一代 PCIe 的需求,以高效率的方式將資料中心伺服器連接到高速乙太網路、網路附加儲存裝置和人工智慧加速器。

連網車將進一步提升資料負載量、增加即時處理的壓力,以提高自動駕駛能力水準,最終實現全自駕車的目標。在資料中心的背後,訓練神經網路進行人工智慧推理作業,要用到極為大量的運算作業,嚴重暴露出與周邊裝置進行通訊的瓶頸。

這些因素開始發揮作用,PCIe 該繼續向前發展。2017 年發布 PCIe 4.0,不久後在 2019 年發布了 PCIe 5.0。圖 一顯示 PCIe 各版本提供的聚合速度。

| 圖一 : PCIe 各版本提供的聚合速度 (資料來源:Diodes 公司) |

|

各大資料中心紛紛捨棄 100Gb 乙太網路,改用最新的 400Gb 規格,有望推動廣泛採用 PCIe 5.0。在實務上增加 PCIe 頻寬一事,或多或少有跟上乙太網路速度加快的腳步,最理想的情況是在兩種標準之間保持平衡,有助於避免效能方面的瓶頸。

如今仍在使用「老舊」的 PCI 標準

PCIe 5.0 產品開始進入市場,加上日前 PCI 特殊興趣小組(PCI-SIG)宣布已展開研發新一代 PCIe 6.0,將於 2021 年完成,在可預見的未來,PCIe 將會是要求高效能周邊裝置通訊協定的首選。

與此同時,向下相容性成為 PCIe 系列的一大優勢。PCIe 規格沒有失效日期,多代產品可以共存於市場,甚至共存於同一個產品應用項目中。這對系統設計人員來說是一項優點:新一代 PCIe 產品不斷出現,以滿足日益成長的頻寬需求,早期產品仍能在眾多情景中貢獻其價值,像是個人運算裝置、遊戲及部分企業運算和網路產品應用項目。

解決實行上的挑戰

每一代 PCIe 之間的向下相容性,使得系統能夠受益於新晶片推出時更高的傳送速率,又無需大幅變更設計。另一方面,提高訊號速度對訊號邊限帶來額外壓力,並可增加設計的複雜性。再者,顯然得解決跟 PCIe 橋接的問題,不僅是在老舊介面之間,還有在 USB 或圖形連接埠等其他介面之間。

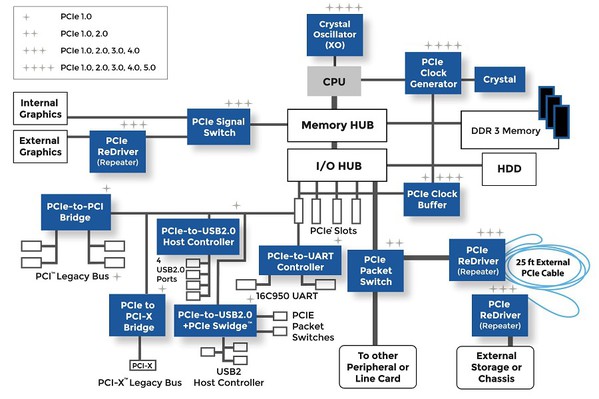

設計人員需要存取支援各代 PCIe 的裝置,如圖二所示的時鐘產生器、時鐘緩衝器、控制器、封包切換器/橋接器、ReDriver晶片及高速多工器,以因應這些挑戰。

| 圖二 : Diodes 推出之 PCIe 解決方案的範例。(source:Diodes 公司) |

|

ReDriver 晶片能夠為提高高速系統的訊號完整性,提供一種實惠又便利的解決方案。ReDriver 使用等化及預強化等技術,輸出驅動器有著最低延遲性,補償傳輸線的損失情況,以恢復訊號邊限並將抖動情況降至最低,確保接收器有著低位元錯誤率。與整合包括時脈及資料恢復等額外功能的重計時器相比,ReDriver 具備低延遲的特性,且成本較低、易於實行。

圖 二顯示如何在需要驅動訊號穿過較長 PCB 軌道處使用 PCIe ReDriver 的情況,例如到外部顯示卡或透過纜線到外部儲存裝置。這些 ReDriver 具有完全向下相容性,支援所有舊款 PCIe。

橋接器與切換器滿足各類主機和端點裝置之間的介面要求。封包橋接器通常會在 OSI 參考模型中的兩層之間,或是兩個通訊協定之間提供一個介面。圖二還顯示如何使用橋接器在 PCIe 與包括 PCI-X 在內的老舊 PCI 標準之間進行連接,或連接到 USB 連接埠或 UART 匯流排介面。封包切換器這項多連接埠/多通道裝置,通常用於將單一根複合體擴展到具有多通道的多個連接埠,以存取周邊裝置或線路卡等其他對等系統。

除了提供有著多種連接埠配置及轉換功能的封包橋接器和切換器,Diodes 公司還結合了 PCIe 封包切換器與 PCIe-to-USB2.0 橋接器的功能,打造出 PI7C9X442SL PCI Express-to-USB 2.0「切換橋接器」。這種多功能裝置可以從一個 PCIe x1 上游連接埠扇出到兩個 x1 下游和四個 USB 2.0 連接埠,使得系統主機處理器同時存取多個 PCIe 和 USB 裝置。

Diodes 公司等企業可以提供多款無源雙向 PCIe 1.0、PCIe 2.0 或 PCIe 3.0 訊號多工器/解多工器,將單一 PCIe 通道連接到多個通道,為圖形或運算作業擴大頻寬。也能將這些裝置用於從單一多通訊協定介面連接。

時鐘緩衝器通常可以將單一參考訊號當成輸入,並且產生多個輸出,以便更廣泛地分佈在 PCB 上。時鐘緩衝器 IC 有多種配置,Diodes 提供專有的 PLL 設計,確保抖動保持在 PCIe 要求的範圍內。時鐘產生器可以產生輸出抖動極低的特定頻率時鐘訊號,適用於 PCIe 及其他系統時脈。Diodes 的產品組合有 1.8V PI6CG18xxx 和 1.5V PI6CG15xxx PCIe 4.0 時鐘產生器及緩衝器,有 2、4 和 8 通道配置,符合各舊款 PCIe 的要求。整合晶片內的端點,這些裝置為每個輸出省下 4 個外部電阻器,在物料清單中減少多達 32 個元件。

結論

從嵌入式和桌面運算,再到高頻寬資料中心連線及神經網路訓練等應用項目,PCIe 都是首選的高效能互連技術。設計人員可以利用早期 PCIe 標準一直沿用至今的優點,加上向下相容新舊不同規格的特性,以具成本效益的方式滿足各種系統要求。設計人員使用有著橋接器、緩衝器、ReDriver、切換器及多工/解多工 IC 等功能的裝置組合,高效率地解決產品應用項目的嚴苛要求。

(本文作者Kay Annamalai為Diodes 公司資深行銷主管)