抗混疊設計是ADC類比前端設計裡非常重要的一部分,需要結合ADC類型、實際電路中的各種雜訊要素系統地去考量。有時我們會發現,透過ADC測出來的訊號,在實際PCB電路上找不到源頭,這有可能是在ADC抗混疊類比前段設計出了問題。

頻率混疊

我們舉一個實例來看什麼是頻率混疊:

如圖一,fs為取樣頻率,fin為訊號頻率。當fs<2fin,fs=1.3fin時,黑色虛線是實際的訊號波形,紅色實線為取樣得到的波形。我們可以看到取樣得到的波形已經脫離實際波形,這就發生了混疊現象。

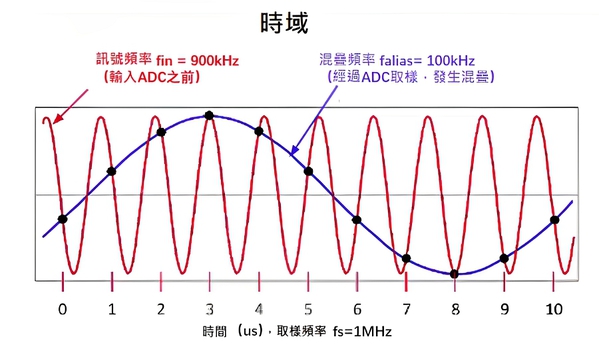

假定訊號頻率fin=900kHz,取樣頻率fs=1MHz。圖二的紅色正弦波是實際訊號,藍色正弦波是透過ADC取樣之後的訊號,我們實際看到的混疊頻率falias=100kHz。

| 圖二 : 時域中,訊號頻率與混疊頻率的關係(source:TI) |

|

根據奈奎斯特取樣定律,取樣頻率至少是訊號頻率的兩倍以上。如果取樣頻率小於訊號頻率的兩倍就會發生混疊現象。我們切換到頻域,更容易看清這個問題。

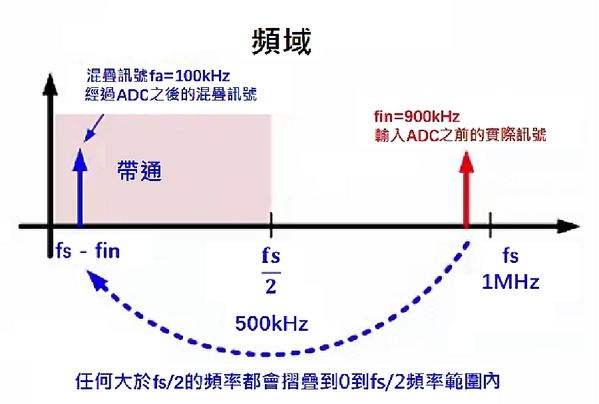

| 圖三 : 頻域中,訊號頻率與混疊頻率的關係(source:TI) |

|

在頻域圖裡,根據奈奎斯特取樣定律,任何大於fs/2的頻率訊號將會鏡像折疊到0到fs/2的頻率範圍內。當取樣頻率fs=1MHz時,所有大於500kHz(fs/2)的訊號,將會折疊到0到500kHz頻率範圍內。當訊號頻率fin=900kHz,這時讀取到的混疊訊號fa =fs-fin=1MHz-900kHz = 100kHz。

如何防止頻率混疊?

加一些週邊電路(濾波器),可以把產生頻率混疊的一些頻率濾除,進而防止頻率混疊。

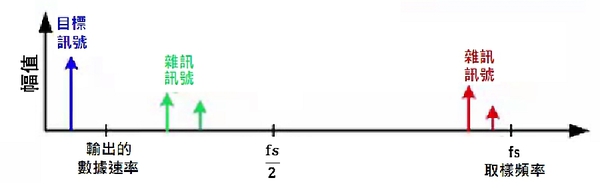

如圖四,在頻域範圍內,藍色是我們要採集的訊號頻率,綠色和紅色都是不希望出現的雜訊訊號頻率。

| 圖四 : 頻域中的目標訊號與雜訊訊號(source:TI) |

|

以Σ-Δ ADC舉例,這是一種目前使用最為普遍的高精準度的ADC結構。

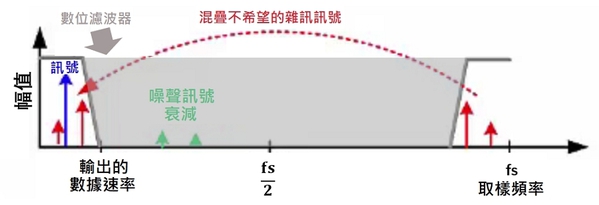

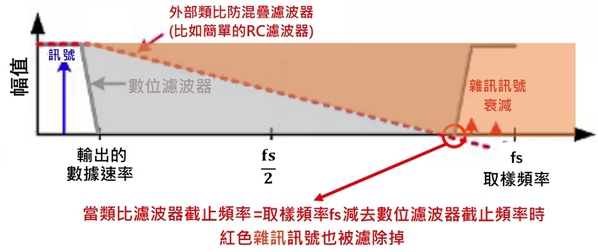

一般Σ-Δ ADC會自帶數位濾波。理論上講,數位濾波器可以濾除截止頻率到fs/2內的雜訊,如圖五灰色部分的頻率,將會被數位濾波器濾除,因此,圖中的綠色部分的雜訊訊號將被濾除。

根據奈奎斯特取樣定律,任何大於fs/2的頻率訊號將會鏡像折疊到0到fs/2的頻率範圍內。如下圖紅色部分的雜訊會避開數位濾波器,折疊到訊號頻率附近。

| 圖五 : 設計數位濾波,濾除不希望的雜訊訊號(source:TI) |

|

所以,在實際電路中,還需要一個外部類比防混疊濾波器(比如簡單的RC濾波器)。如圖六紅色部分的頻率,將會被外部類比濾波器濾除。當類比濾波器截止頻率=取樣頻率fs減去數位濾波器截止頻率時,那麼後面紅色部分的噪聲訊號也會被濾除。

| 圖六 : 設計外部類比防混疊濾波器,濾除不希望的雜訊訊號(source:TI) |

|

經過數位濾波和類比濾波雙重過濾,在檢測範圍內,只剩下所要的目標訊號。

對於Σ-Δ ADC,內部有數位濾波器,這個數位濾波器有助於降低外部類比濾波器的設計要求。

Σ-Δ ADC抗混疊類比前端設計

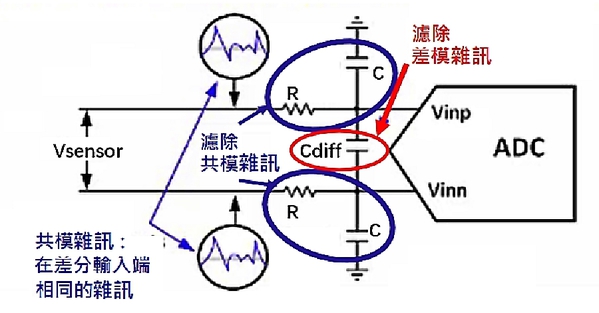

真正考慮Σ-Δ ADC抗混疊類比前端設計的時候,不僅要考慮濾波器頻寬的問題,還要考慮實際電路中的各種雜訊,以及噪聲來源的特性。比如共模雜訊,差模雜訊等。

濾除共模雜訊與差模雜訊

如圖七,每根差分線上都會有一個一模一樣的RC濾波器結構,用來濾除共模雜訊的干擾。

| 圖七 : 濾除共模雜訊與差模雜訊(source:TI) |

|

兩個差分線不可能完全一致,電容電阻會有微小的差異,進而導入差模雜訊。為了解決這個差模干擾,我們一般會在兩路差分訊號中跨接一個電容Cdiff。一般Cdiff的容值時Cdm的10倍以上,來降低差模雜訊。

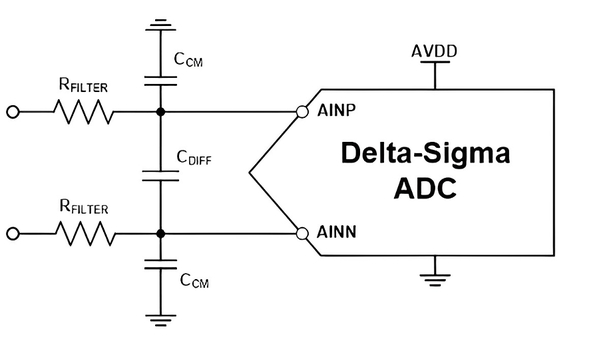

差分輸入Δ-Σ ADC,抗混疊濾波器如何設計?

低速Δ-Σ ADC通常需要一個簡單的單濾波器來減少混疊效應。對於差分訊號,濾波器結構通常由兩個濾波路徑組成:一個差分濾波器(源自兩個濾波器電阻RFILTER和差分電容器CDIFF的組合);一個共模濾波器(源自一個濾波器電阻RFILTER和共模電容器CCM的組合)。

| 圖八 : Delta-Sigma ADC的抗混疊濾波器結構 |

|

結語

抗混疊設計是ADC類比前端設計裡非常重要的一部分。抗混疊設計,並不能從單一去考慮,而是應該結合ADC類型、實際電路中的各種雜訊,系統化去設計。瞭解頻率混疊的發生機制,掌握防止頻率混疊方法,才能設計出良好的ADC抗混疊類比前端。

(本文作者Barley Li為Digi-Key Electronics亞太區技術內容部門應用工程經理)