I/O頻寬的需求每三年就會倍增,因此PCIe 5.0是一個早該推出的規範。而在PCI-SIG的努力下,PCIe 5.0規範終於在今年5月正式推出,並且已經有多個設計導入,終端產品預計在2020年就能夠陸續推出。

| 圖一 : 依據市場的發展,I/O頻寬的需求每三年就會倍增。(source/PCI-SIG) |

|

PCIe 3.0的時代,真的令人感覺漫長。甚至一度讓人以為那就是「固定」的規格了。然而,那其實是一個諸多糾結的總和。SSD市場仍不上不下,智慧手機突然搶了PC的風采,網路也還沒有很快,一切的種種,造成了PCIe 3.0可以存在的相安無事。

只不過產業變革有時就像海嘯,一道大浪打過來,原有陳舊的一切,就會被沖擊毀去。而那個大浪,就是目前仍在全速前進的數位轉型趨勢,它驅動了半導體技術持續突破、讓行動網路從4G轉進5G、讓大數據與人工智慧成為現實。

而這一切都需要更高的運算速度與傳輸性能才得以實現,因此作為I/O傳輸的樞紐,PCIe 3.0介面也不得不著手進行升級。

追趕延誤的進度 PCIe 5.0加速推出

只不過因為之前的升級作業擱置太久,整整停滯了將近十年,要再重啟就立即面臨人事全非的窘境,許多的文件與流程都需要重新擬定,因此這個新標準制定的進度就顯落後產業許多,同時也出現了需要連升兩級的怪現象。

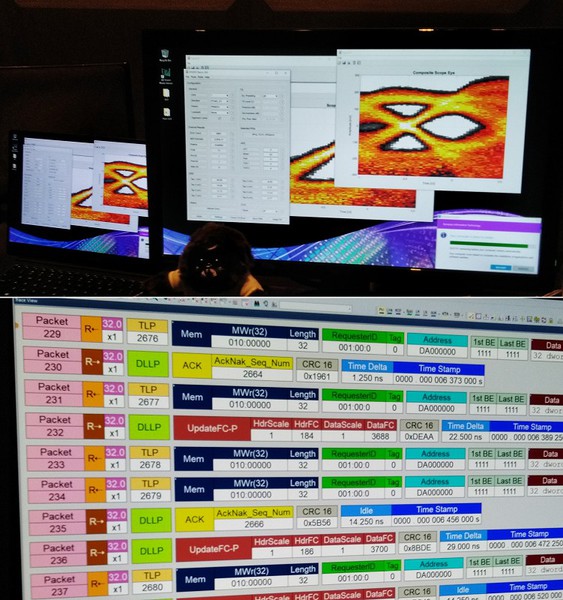

| 圖二 : PCIe 5.0的測試與驗證方案目前已問世,能支援最前端應用開發。(攝影/籃貫銘) |

|

也就是在PCIe 4.0推出後,不到2年的時間,PCIe 5.0規範馬上就出台。但是PCI-SIG副總裁暨開發者會議主席Richard Solomon卻說:「事實上,PCIe 5.0是來遲了。」

因為依據市場的發展,I/O頻寬的需求每三年就會倍增,因此PCIe 5.0是一個早該推出的規範,目前PCI-SIG的工作就是在補進度罷了。而在PCI-SIG的努力下,PCIe 5.0規範終於在今年5月正式推出,並且已經有多個設計導入(design-in),終端產品預計在2020年就能夠陸續推出。

相較於PCIe 4.0,PCIe 5.0在效能上又成長一倍,其信號速率達到32 GT/s,單道的頻寬提升至32 GB/2,而x16的頻寬則增加到了128GB/s,並維持向下相容(支援4.0~1.0)的功能。除了頻寬倍之外,PCIe 5.0也改善了電子的設計,以提高信號的完整性,並增加連接器的機械性能。此舉不僅能減少信號延遲,同時也改善了信號傳輸時的衰減。

| 圖三 : PCI-SIG副總裁暨開發者會議主席Richard Solomon。(攝影/籃貫銘) |

|

在今年11月舉行的PCI-SIG台北開發者大會的現場,就已有數家業者展示了PCIe 5.0的解決方案,包含PCIe 5.0 CXL和CCIX的IP方案、測試與驗證系統、與高速傳輸的重定時器(Retimer)等,為PCIe 5.0的產業應用之路,先行踏出了第一步。

「我們不希望再重蹈PCIe 3.0時代的失誤。」Richard Solomon強調。

他表示,有鑑於PCIe在3.0之後開發延宕的前車之鑑,PCI-SIG正持續推動新版標準的開發進度,這也是為什麼會在4.0發表之後一年,今年就宣布了5.0的規範。

頻寬供不應求 PCIe 6.0將改採PMA-4

他指出,由於人工智慧、汽車電子、雲端運算、資料中心、物聯網與數據儲存等先進應用,市場對於運算力與傳輸頻寬的需求仍是會持續增加,因此新的規範必須不斷的推進,才能夠因應未來的應用需求。

依據PCI-SIG的預估,至2022年,市場的頻寬需求就會達到128 GB/s,至2025年則會再倍增至256 GB/s。而身為標準制定組織,就必須要在實際需求發生之前,先行將標準底定。

「我們的期待就是領先3年左右,讓製造商與相關的供應鏈可以有時間把產品開發完成。」Richard Solomon說。

目前PCIe 4.0的終端產品正迅速地進入市場中,PCIe 5.0的產品,也已經有了先行者,預計採用該規範的終端產品在明年就會率續亮相,至2021年就會有更多的產品導入。

然而今年最重磅的消息,還是PCIe 6.0草案0.3版本的發布,該規範才在今年十月推出。Richard Solomon指出,新的標準將會把頻寬再往上升一級,信號速率會達到64GT/s。此外,另一個大特色,是從不歸零(NRZ)傳輸技術,演進為四階脈衝振幅調變(PAM-4)。

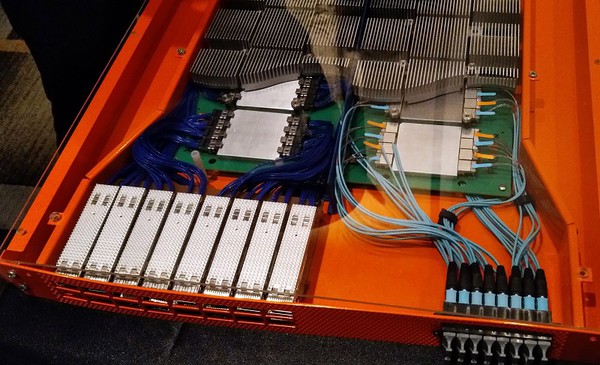

| 圖四 : PCB內的連結改採外接的光纖方案,以解決互連頻寬不夠的問題。(攝影/籃貫銘) |

|

這個變動的主要原因就是NRZ在高速傳輸時,訊號很容易衰減,而為了實現更高頻寬的傳輸,因此轉向PAM-4訊號。由於PAM-4能實現四種可能的電壓位準,讓每個符號代表2個位元,因此PAM-4技術理論上可以得到兩倍於NRZ的速率。

Richard Solomon解釋,使用PAM-4技術是一個新的進展,但目前仍在討論中,而透過0.3版本的發布,也將會從會員的開發實作裡取得更多的回饋,並據此再進行調整,若會員的回饋不理想,最後仍會有變動的可能性。

Richard Solomon也透露,PCIe 6.0的0.5版本很快就會推出,會更聚焦在具體的實作上,而最終的版本預計會在2021年訂定。

超高速帶來新的系統設計挑戰

不過持續倍增的速度並不全然沒有缺點,首當其衝的,就是對系統設計者帶來更大的壓力,不僅在整體的系統規劃上需投注更大的心力,以尋求在速度與穩定度上的平衡。而在開發後段的測試與驗證上,所需要的成本也將更龐大。

其中一個挑戰,就是內部各元件的同步與調適。由於更高速的數據傳輸,意味著訊號的錯誤率也會倍增,如何對PCB機板上的其他元件進行調適,就成為一大挑戰。也因此搭載重新計時器(Retimer)就會成為通用的設計。

再者,單一通道的頻寬的倍增,也讓目前的連接方案顯得難以因應,尤其是在伺服器與超級電腦這類高負載的運算應用上,也因此一些PCB內部設置的連結就改採外接的光纖方案,以解決內部互連頻寬不夠的問題。

整體而言,PCIe 5.0和6.0的相繼問世,將會對目前的元件與系統I/O設計帶來全方位的影響,並有望實現次世代的高超速傳輸與運算效能。然而,目前既有的相關周邊與PCB的設計,也需要隨之進化,才有望把這個新規範的潛力完全釋放。