高效能雲端計算系統對資料速率的要求不斷提高,這讓資料中心設備部署中的各類元件面臨訊號完整性的重要挑戰。資料速率增加導致訊號傳輸距離變短,並且限制系統的可擴展性。儘管Redriver或Retimer元件可幫助解決限制問題,但二者皆各有優缺點。本文介紹這些元件如何擴展週邊元件高速介面(PCIe)協定訊號範圍,以及如何選擇在目前甚至未來最適合計算系統和NVMe儲存應用的協定。

PCIe訊號完整性挑戰

PCIe介面標準是目前高效能計算系統和資料中心最常用的一種介面標準。PCIe的資料速率已從第一代(Gen1)的2.5GT/s發展到第五代(Gen5)的32GT/s。與上一版本的資料速率相比,第六代(Gen6)的資料速率將再次實現翻倍。頻率增加已然實現,可以支援更高的資料速率,因此面臨的挑戰是以合理的系統成本來保持足夠的訊號完整性。Redriver和Retimer元件均為可以彌補欠缺的解決方案。

FR4印刷電路板(PCB)是電子行業最常用並且最具成本效益的材料。FR4 PCB材料在相對較低的頻率下呈現出色的效能,可接受的衰減低於10 GHz。但是,隨著資料速率的提高,FR4材料的頻率回應能力也相應下降。Megtron 6等其他PCB材料雖然頻率回應能力強、訊號損耗少,但成本十分高昂。例如,Megtron 6的成本約為FR4的七倍。其他能夠在微波頻率範圍內運行的材料的成本更高。

圖一為FR4和Megtron 6 PCB材料的PCB衰減曲線。視PCB複雜性和尺寸而定,改用高品質材料PCB的成本可能令人難以承受。

一些應用可能需要使用連接器將訊號傳送到設計的其他部分,如背板和板外附加轉接卡。連接器也是造成訊號損耗的一個因素。PCIe CEM連接器在32 Gbps的速率下會增加約1.5 dB的損耗。PCIe Gen5標準規定,允許的通道損耗預算為36 dB(端到端)。

使用Redriver或Retimer可協助保持PCIe訊號的完整性。要做出正確選擇,需對兩者之間的差異有基本瞭解。

Redriver介紹

Redriver是一種帶接收(RX)端等化器(EQ)的高頻寬放大器,可補償因PCB走線或纜線而導致的頻率相關衰減。連續時間線性等化器(CTLE)的主要功能是使失真波形閉合的「眼睛」張開。發送(TX)端可包含預加重功能(發送等化器),用來預先形成發送波形。如果走線或纜線長度超出標準範圍,則可透過在DisplayPort、USB、Thunderbolt、HDMI和PCIe等序列介面的路徑中放置Redriver來加強其訊號完整性。類比放大器未經歷鏈路訓練過程,因此不會區分任何特定的協議標準。由於與協議無關,鏈路可能不符合任何介面標準。類比電路的特性使其不需要時鐘。

Redriver的主要缺點是它在放大資料訊號的同時,也會將訊號路徑中的任何雜訊放大。放大器本身具有本底雜訊,會在訊號的整體雜訊圖中加入自身的雜訊。典型的線性Redriver等化器可為訊號增加8 ps的固有抖動,並對符號間干擾(ISI)抖動進行校正。Redriver無法補償非ISI抖動。與Retimer相比,在某些情況下,Redriver的功耗和總成本更低。典型的Redriver延時約為100 ps。圖二概括了類比單通道Redriver的關鍵構件。

Redriver中的高頻寬放大器可以是線性放大器,也可以是限幅放大器(非線性)。視具體設計而定,線性放大器可提供一些針對PCIe協議的偽鏈路訓練功能。限幅放大器不支援針對任何協議的任何類型鏈路訓練序列。限幅放大器僅支持兩個閾值電平來確定所接收訊號的狀態。由於大多數鏈路訓練脈衝需要檢測中間閾值,因此對於Redriver而言,要支持訓練序列極其困難。這就是限幅放大器的「盲點」。

Redriver的自身限制

如果應用規模足夠小,並且提高訊號傳輸距離並不過於複雜,則Redriver可以支援PCIe Gen 1到Gen 3的資料速率。但隨著設計規模和複雜性的提升,如果仍然使用具有成本效益的材料,Redriver將再也無法補償訊號損耗。串聯(cascading )兩個Redriver來解決這一問題不切實際。任何雜訊或隨機抖動都將隨目標訊號一起放大。類比放大器無法重置任何雜訊或時序預算。因此,級聯兩個Redriver實際上會將資料的雜訊量加倍。

從訊號完整性角度而言,16 Gbps資料速率的PCIe Gen 4所帶來的挑戰更為艱巨。大多數PCIe Gen 4介面應用都處於雲端儲存、伺服器和高效能計算平台中,在這些應用中,需要透過長走線、連接器、纜線、插槽和轉接卡(AIC)來驅動16 Gbps鏈路。在資料中心基礎架構用例中,Redriver在這樣的資料速率下根本無法使用。

2019年,隨著PCIe 5.0的發佈,資料速率提高到32 Gbps。部署資料速率不斷提高的PCIe鏈路的主要推動因素是採用400 Gbps乙太網、多重200 Gbps無限頻寬以及加速器/GPU組件和技術的高階網路系統。促使資料速率提升的另一個因素是部署在企業伺服器和儲存系統中的NVMe SSD元件。其他串列協定(如USB4.0、DisplayPort 2.0和Thunderbolt 3.0)也逐漸實現了資料速率加倍。

Retimer前來救場

面對解決這些高速訊號完整性問題的要求,自PCIe Gen 4開始,PCIe標準對PCIe Retimer要求進行了定義。該標準將Retimer定義為一個元件,該元件能識別實體層協定,並且必須能透過Retimer每一端的任何相容通道與任意元件對進行交互操作。因此,Retimer的複雜程度高於Redriver。

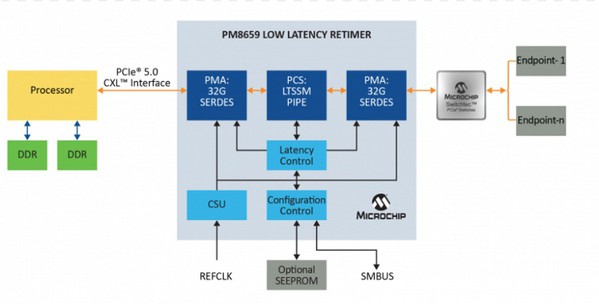

圖三顯示單通道雙向Retimer的高階架構。PCIe標準將其稱為PCIe x1配置。大多數PCIe Retimer為x4(共8個通道:4個RX,4個TX)、x8(16通道)或x16(32通道)。實體層是物理介質連接(PMA:物理子塊),收發資料的串列器/解串器(ERDES)位於其中。PMA是一個混合訊號構件。在接收端,它會對失真訊號進行均衡處理,並使用CTLE對雜訊進行濾波。Retimer的核心是一個時鐘和資料恢復(CDR)模組。CDR將嵌入式時鐘連同並行域中的資料一起恢復。PMA模組將並行資料序列化以便於傳輸,並將接收的資料解串為物理編碼子層(PCS)塊。眼圖監視塊生成一個接收眼圖的即時捕獲波形,以進行除錯。PCS負責處理鏈路訓練狀態狀態機(LTSSM)和PIPE(PCIe的PHY介面)功能。PCS是一個純數位部分。

表一概括了Redriver與Retimer之間的主要差異。

表一:Redriver和Retimer比較

|

|

Redriver

|

Retimer

|

|

協議

|

不可知

|

可知

|

|

外部時鐘

|

無

|

有

|

|

級聯

|

無

|

有

|

|

潛在

|

-100ps

|

64ns 基於 PCI 4 & 5 規範

|

|

協議鏈路培訓

|

無

|

有

|

|

功率和成本

|

低

|

較高

|

|

均衡器

|

CTLE

|

CLTE, DFE 和發送器 FIR

|

|

抖動

|

減少確定性抖動(Dj),位元也增加隨機抖動(Rj)

|

消除 Dj 並完全重置 Rj

|

|

調試模式

|

無

|

眼圖監控、鏈路狀態狀態、接收器裕度

|

PCIe應用中的Retimer示例

PCIe標準是部署在資料中心內用於記憶體、伺服器和網路架構的元件所使用的主要介面標準。CPU利用高速PCIe介面將I/O事務作為PCIe根聯合體傳送給所連接的SSD驅動器或其他端點元件。圖四舉例說明了從CPU到這些端點的拓撲結構。PCIe開關提供額外扇出,可支援更多的端點目標。目前,Retimer已成為支援透過CPU板、背板、電纜和轉接卡實現訊號擴展的必備元件。

| 圖四 : 採用PCIe Retimer的伺服器的示例 |

|

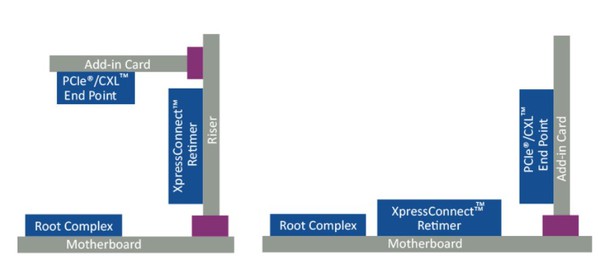

此外,當纜線和/或多個連接器在資料路徑中時,PCIe Retimer通常用於支援訊號調節。Retimer通常在下文列出的CPU與端點之間使用,如圖五所示:

‧ CPU --> Retimer --> 轉接卡(AIC)

‧ CPU --> Retimer --> Riser卡 -->AIC

‧ CPU --> Retimer --> 電纜 --> 開關 --> AIC

‧ CPU --> Retimer --> 電纜 --> AIC

| 圖五 : Riser卡上的Retimer到AIC以及主機板上的Retimer到AIC |

|

在很多資料中心系統應用中,Redriver和Retimer都可以協助保持訊號完整性。視設備設計的複雜性和資料速率而定,Redriver可用於以較低資料速率運行的小型系統。當資料速率高於16 Gbps時,Redriver不足以補償明顯的訊號降級。PCIe 4.0和5.0需使用Retimer來達到合規目的。USB 4.0和Thunderbolt 3.0等其他串列協定也在其透視圖規範中規定了Retimer要求。

由於Retimer會重置訊號抖動預算,並重新生成用於重新傳輸的乾淨訊號,因此不存在插入損耗,並且設計人員能夠以合理的系統成本實現其電腦系統和NVMe儲存應用的全面效能優勢。

(本文作者Tam Do為Microchip資料中心解決方案產品部市場行銷工程師主管)

參考資料

[1] https://www.intel.com/content/dam/www/public/us/en/documents/white-papers/serial-bus-white-paper.pdf

[2] https://pcisig.com/sites/default/files/files/PCI-SIG_Webinar_Retimers_final.pdf

[3] https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an766.pdf

[4] PCI Express Base Specification Revision 5.0 Version 1.0, 2019: https://pcisig.com/