有鉴于近期异质整合晶片上板后的翘曲状况频率提升,导致后续可靠度因空冷焊而造成早夭现象,为协助客户克服此一品质问题,宜特今宣布,导入低温焊接LTS制程(Low Temperature Soldering,简称LTS),藉由使用小尺寸WLCSP封装零件,执行异质合金焊接,并进行后续可靠度验证,从温度循环试验(Temperature Cycle Test)结果显示,LTS制程在可靠度TCT实验中的表现,和一般无铅制程相比,并不逊色,有助于降低翘曲变形量。

|

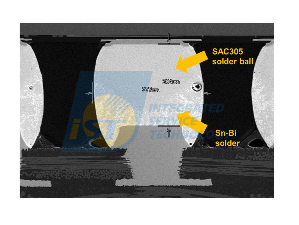

| 透过精确控制焊接温度与锡膏体积,锡铋合金(Sn-Bi)锡膏与SAC305锡球的焊接点,可看出锡球具备良好的扩散性,且无热滴泪状况发生。 |

宜特观察发现,系统单封装( System in a Package)已成为现今趋势,各种不同材质、不同功能的晶片整合进同一封装,这样的封装元件使用的材料相当复杂且多元,堆叠在一起时,因材质本身热膨胀系数不同(CTE)就会产生翘曲(Warpage),成为表面黏着制程(Surface Mount Technology,简称SMT)良率最大挑战。

针对预防翘曲造成空焊现象,一般传统做法是,模拟确认翘曲(Warpage)数据,调整锡膏印刷钢板设计及回流焊温度,借此减少因翘曲( Warpage )造成空焊及短路问题的机率。依据此方式,宜特已成功替多家厂商克服PCB或IC翘曲( Warpage )的焊接问题。

然而上述传统方式,可以藉由修正锡膏来避免空焊或短路问题,但如果翘曲(Warpage)程度太高,就无法藉由控制锡膏量来解决了。为解决此议题,宜特科技板阶可靠度(BLR)实验室导入新的做法-低温焊接制程( Low Temperature Soldering ,简称LTS),藉由减少热应力,以降低翘曲( Warpage )变形量。

宜特指出,产生 Warpage 主要原因,来自于使用不同材料的IC堆叠后,由于不同材料的热膨胀系数(CTE)不同,经过高温焊间产生形变。温度越高,因热应力造成封装后的IC ( Package ) 变形程度越大。因此,藉由降低 SMT 焊接温度,将可大幅减少热应力,借此不仅可改善PCB与零件的 Warpage 程度外,也可减少能耗。而一般无铅焊接所使用锡、银、铜合金的熔点温度约在220℃,峰值温度达到230℃~250℃,而低温焊接所使用锡、铋合金熔点温度为140℃,峰值温度则可降低到170℃~200℃。

宜特进一步指出,低温焊接LTS制程因为不同合金所要求熔融温度不同,而容易产生热滴泪(Hot Tearing)效应,宜特也克服此项挑战,借着精确控制温度与锡膏体积,即可避免LTS制程中出现热滴泪( Hot Tearing )的现象(见图)。

宜特表示,在封装材料无法解决CTE 问题之前,LTS制程不失为一个降低Warpage程度的方式。而在实际应用上还包含了主被动零件,如晶片电阻、电容、记忆体、晶体管等等,越早准备就越早能切入市场。