随着首批商用5G无线网路陆续启用,爱美科为5G及未来世代通讯应用准备了下世代的行动手持装置。更确切的说,该团队正在研究如何运用与CMOS制程相容的三五族材料技术来改良前端模组。这些前端模组将以毫米波运作,尺寸精巧、性能强大且具备成本及能耗方面的效率。爱美科的计画主持人Nadine Collaert将于本文说明爱美科目前正在研发的相关技术,并展示第一批功能元件。

5G带给行动手持装置新的挑战

第五代行动通讯网路应该会将物联网推升至更高境界。 5G将实现超级行动大宽频、低延迟,以及超过100Gbps的资料传输率。借着上述特性,5G将巩固下一代科技的基础,从自驾车、机联网(machine-to-machine communication;M2M)到智慧城市和人工智慧。

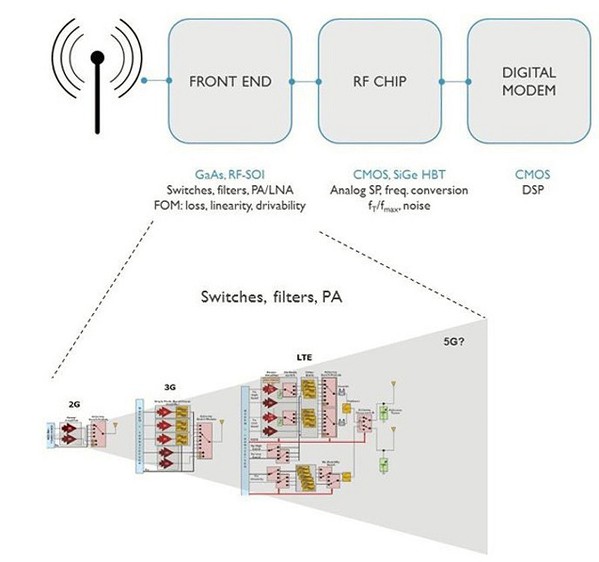

2019年,我们看到首批商用5G无线网路陆续启用。在5G部署的第一阶段,无线通讯主要由sub-6 GHz射频频段支援。然而,这些频段中的频谱供不应求,这就驱动操作频率逐渐朝向毫米波运作,28-39GHz的频段则是下一步。采用这些毫米波频段将对5G的整体网路基础设施产生重大影响,包括基地台、小型基地站和用户设备。对行动手持装置(例如智慧型手机)来说,这个重大影响就变成日趋复杂的前端模组。前端模组运用功率放大器、射频开关和滤波器作为主要构件,接收来自天线的讯号或发送讯号至天线。

| 图一 : 各代行动通讯射频前端模组设计趋向复杂化的示意图 |

|

为了让射频前端模组能以毫米波运作,就必须结合高速及高输出功率。此外,将这些模组用在以电池供电的手持装置上,对其规格尺寸、成本和功耗效率带来高要求。这些需求特别会影响到未来射频前端模组的发射端。

目前这类模组由各种技术构成,包括基于砷化镓(GaAs)且高速的异质接面双极电晶体(heterojunction bipolar transistor;HBT)—通常在小型且高价的GaAs基板上制造,用来制造功率放大器;以及射频绝缘体上矽(RF-silicon-on-insulator;RF-SOI),用来制造射频开关。这些元件各自分别制造及封装,随后在同一片载波基板上组装。创新的解决方案必须要微缩晶片尺寸和降低成本,并提高传输速度和功率输出。

关键解方:共整合(co-integration)

实现微缩尺寸和降低成本的一种诱人办法,就是将射频前端的辅助元件以一种相容于Si-CMOS制程的技术共整合。这些元件最终会和无线电通讯晶片的其他元件(像是控制电路、ADC或DAC)共整合。除了成本和尺寸优化外,共整合应该还会提升整体电路的能源效率。

2018年初,爱美科成立了「产业联盟计画(Industrial Affiliation Program;IAP)」,以实现上述目标。在计画第一阶段,一项与CMOS制程相容的III-V-on-Si技术正在开发中,用以制造具备高输出功率的高速元件。

在计画第二阶段,爱美科的团队会探究将这些高速元件共整合至其他基于CMOS制程元件的可能性,看是运用单片或2D整合(将矽元件和三五族元件放在同一片基板上),或是利用2.5D或3D整合技术。

确认理想元件

爱美科团队正在研究哪一种(和CMOS制程相容的)元件和结构能够实现预期的性能特性。两种途径正在开发中,各自允许不同的操作频段运行。

第一种途径是测试基于氮化镓(GaN)的元件,提供较低频的毫米波运作。基于三五族宽能隙材料的元件具备处理高功率的能力,因此很有希望被用来制造具高输出功率的功率放大器。这些元件目前用于电力电子应用,也用在基地台—通常以超过28V的工作电压运作。为了应用在行动手持装置上,工作电压必须大幅降低(至5V以下),且缓冲层必须与射频相容,将射频讯号损失最小化。

其他设计挑战包含将元件整合至矽,以及找出能够传输高速射频工作速度的合适架构。为了协助达成这个目标,爱美科的研究团队可以凭靠本身在GaN-on-Si技术上长久累积的专业—该技术原本用于发展电力电子应用。

第二种途径聚焦在将基于磷化铟(InP)的元件整合至矽,因而得以借助爱美科在III-V-on-300mm Si技术上的专业—该技术发展背景是为了实现CMOS制程中的尺寸微缩。

首先,该团队正在研究HBT元件,这是一种射极区与基极区采用不同材料的双极性电晶体(bipolar junction transistor;BJT),因而形成异质接面。射极包含磷化铟镓(InGaP)且基于GaAs的HBT元件已显现出高速能力。而高电子迁移率可望出现在基于砷化镓铟(InGaAs)或基于InP的元件上,为使用远超过28-39GHz的毫米波操作频段铺路,并解决6G所会面临的挑战。

比较GaN-on-Si元件结构 以实现高频操作

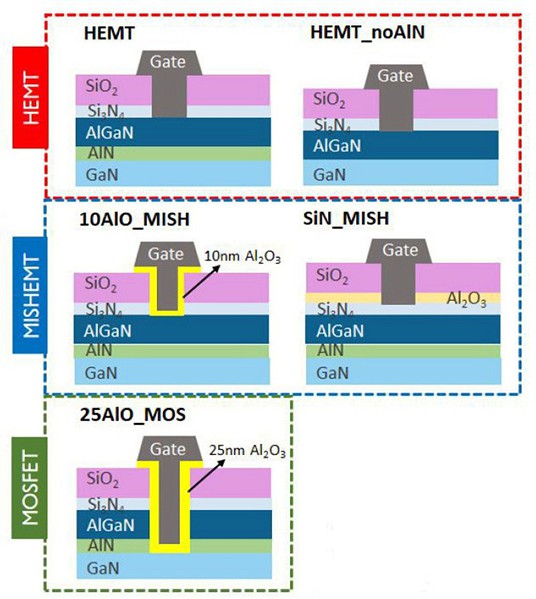

作为第一种途径,爱美科研究员使用标准矽CMOS工具中的无金加工,将基于GaN的元件和氮化铝镓(AlGaN)阻障层整合在200mm的矽晶圆上。为了确认出高频操作应用中最具前景的可微缩结构,该研究团队比较了三种不同的元件结构。他们在寻找同时具有正临界电压(threshold voltage;VT)及负临界电压的元件,以确保设计电路的弹性。

性能表现优异的元件都是基于GaN的高电子迁移率电晶体(high electron mobility transistor;HEMT)元件。这些元件是采用萧基金属闸极(不含高介电氧化物)且具备负临界电压的空乏模式(depletion mode;d-mode)元件,或称常开型元件。

在这个性能测试「频谱」的彼端,是基于GaN的MOSFET常闭型元件,具备正临界电压。该正临界电压操作模式的代价是性能,因为AlGaN阻障层在闸极堆叠沉积前就在通道区被蚀刻移除,导致高迁移率的二维电子气(two-dimensional electron gas;2DEG)被移除。

而性能表现介于HEMT和MOSFET元件的是金属绝缘半导体HEMT(metal insulator semiconductor HEMT;MISHEMT)元件或金属氧化物半导体HEMT(metal oxide semiconductor HEMT;MOSHEMT)元件,这些元件结合HEMT和MOSFET各自的优点。可以想见透过优化AlGaN阻障层的厚度,这些元件的临界电压能在正负值之间调适至最佳状态。

| 图二 : 基于GaN的元件架构类型:HEMT、MISHEMT和MOSFET。 |

|

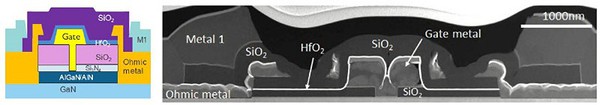

| 图三 : 加工完成后的元件横剖面示意图与穿透式电子显微镜影像。 |

|

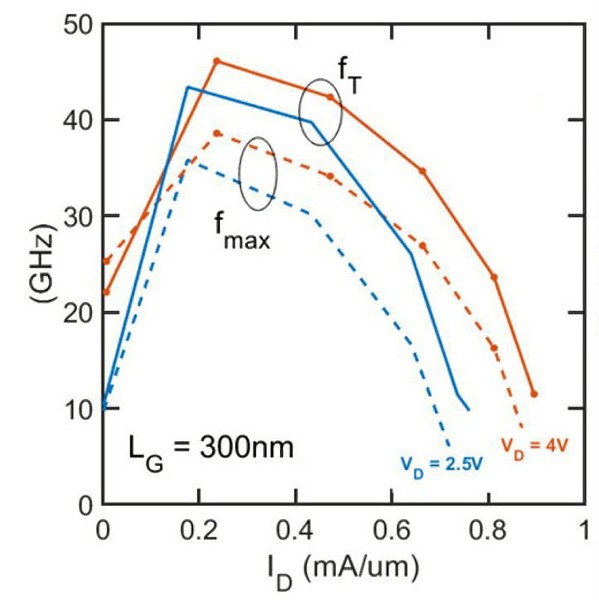

爱美科的研究团队表示,就高频操作而言,MISHEMT元件在尺寸扩充性和杂讯性能方面胜过其他元件类型。这些MISHEMT元件也展现了最高的迁移率,亦即场效载子迁移率大于2000cm2/V.s。闸极长度为300nm且汲极偏压只有4V的情况下,可获得fT/fmax的尖峰截止频率。 fT/fmax用以测量元件的固有速度,而MISHEMT测得的上述数值能确保以sub-6 GHz频段运作。

| 图四 : 堆叠于 200mm 矽晶圆上的GaN/AlGaN元件:在VDS=2.5V及4V的情况下,电流增益(currant gain;fT)和单向功率增益(unilateral power gain;fmax)所测得的截止频率。 |

|

为了实现更高的操作频率而优化元件,就必须进一步微缩元件的闸极长度,因为这将有助于获得更高的fT/fmax将氮化铝铟(AlInN)作为阻障层材料的第一批测试结果显示,透过增强2DEG特性,元件性能可能得以进一步提升,因而提高基于GaN的MISHEMT元件的操作频率。

矽上首款基于GaAs的HBT功能元件:新的成长方法

应用日益增长的三五族材料(例如GaAs on Si)通常伴随着缺点—主要是螺纹状差排(threading dislocation),原因是不同材料间的晶格严重不匹配。这些缺点导致漏电流,会明显拉低元件性能。

降低缺陷密度的一个办法是透过制造深厚(1-10μm)且应力松弛的缓冲层,举例而言,矽锗(SiGe)或复合三五族变晶堆叠。如此,缓冲层上就会生成三五族的主动层。

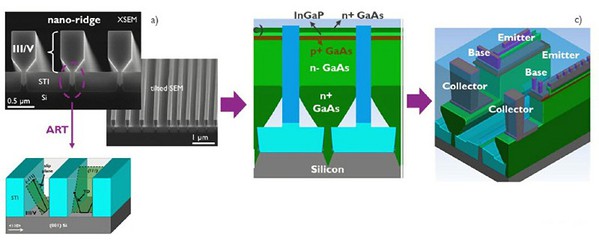

爱美科提出一个不需额外加厚缓冲层的方法。新制程结合了深宽比捕捉(aspect ratio trapping;ART)和材料成长(material overgrowth)技术,这也被称作爱美科独特的奈米折状结构工程(nano-ridge engineering;NRE)处理。

利用ART技术,一道沟槽会生成在矽基板上,随后被三五族材料填满。因晶格不匹配所产生的大多数缺陷,就会被局限在这个高深宽比的沟槽底部。这确保了窄沟槽外的材料生成的螺纹状差排密度低。同时,这样的材料成长让奈米折状结构得以加宽,因而生成大型盒型的形状。这种材料具备低度缺陷,就可以用来制造元件堆叠。

| 图五 : 利用NRE方法进行300mm矽晶圆上混合三五族CMOS整合:(a)奈米沟槽生成;缺陷被捕获在窄沟槽区;(b)利用NRE技术生成HBT堆叠;(c)HBT元件整合的布局类型。 |

|

藉由这个方法,爱美科近期已展示出首款基于GaAs的HBT功能元件,该元件在300mm矽晶圆上制造,并在迈向实现基于InGaAs的元件发展路上,作为第一块跳板。

基于GaAs的奈米折状结构表面的线差排密度显示为低于3x106cm-2。至于生成于GaAs基板上的各个阶层,其层介面(layer interface)的品质相似。基于GaAs/InGaP的HBT元件随后制造。这些元件的性能表现优于参考元件,后者在矽基板上加上一层深厚且应力松弛的缓冲层。

这项展示显现出将混合三五族CMOS技术应用在5G和毫米波应用的潜能。为了达到更高的工作速度,爱美科认为下一步是朝向高迁移率且基于InP的HBT元件发展。

![图六 : 比较本文制造的元件与具有应力松弛缓冲层的叁考元件[1],图为两者的电气特性差异(gummel plot特性曲线图)。](/art/2020/02/101324429830/p6S.JPG)

| 图六 : 比较本文制造的元件与具有应力松弛缓冲层的叁考元件[1],图为两者的电气特性差异(gummel plot特性曲线图)。 |

|

总结

下一代5G行动手持装置需要尺寸小、成本及能耗有效率的前端模组,这些模组相较于第一代前端,要能以更高速运作,并传递更高输出功率。爱美科认为,异质三五族Si-CMOS技术是进步的方法,最终将使得无线电晶片上的其他元件得以共整合。

两种途径正在开发中:(一)提供低频毫米波频段之用的GaN-on-Si,与(二)用于操作频率超过100GHz且基于InP的HBTs-on-Si。爱美科已展示了这两项技术的首款功能元件,以及进一步增强操作频率的确定方法。这为5G行动手持装置应用及往后的发展,提供了下一代射频前端的发展条件。目前开发出的技术将有助于其他也需要高资料传输率的应用,像是虚拟实境(VR)或扩增实境(AR)。

(本文由爱美科授权刊登;作者Nadine Collaert为爱美科高速类比/射频计画的计画主持人;编译/吴雅婷)

**刊头图(source:dficlub.org)

参考资料

[1] C. Heidelberger et al., Journal of Applied Physics 123, 161532 (2018).