AIoT、嵌入式視覺、硬體安全、5G通訊、工業和汽車自動化等新興應用正在重新定義開發人員設計網路邊緣產品的硬體要求。為了支援這些應用,網路邊緣設備的硬體方案需要具備下列特徵:低功耗、高效能、高穩定性、小尺寸。

萊迪思的研發工程師幾年前就開始著手FPGA開發製程的創新,旨在為客戶提供具備上述特性的硬體平台。萊迪思為支援28 nm FD-SOI製程技術的低功耗FPGA供應商。該製程由三星研發,與如今大多數半導體晶片採用的bulk CMOS製程技術有些類似,但優勢更為顯著,能在顯著降低元件尺寸和功耗的同時,大幅提升效能和穩定性。

除了支援全新的製造平台,萊迪思還依託其低功耗、小尺寸FPGA領先開發商的產業經驗,在系統設計的各個層面(從完善的系統解決方案到FPGA架構,再到電路)取得創新,進一步降低功耗,減小FPGA尺寸,同時提升系統效能。全新的製造製程與多個層面的創新催生了萊迪思Nexus FPGA開發平台。

Nexus重新定義低功耗FPGA

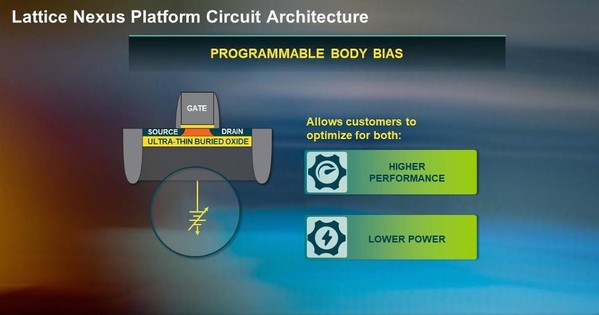

FD-SOI製程讓萊迪思的工程師能夠開發全新電路設計,充分發揮該製程的固有優勢。其優勢之一就是FD-SOI支援可程式化設計基體偏壓(body bias),這是一種位於電晶體基體上的塊電阻,能讓開發人員在電晶體運行期間進行動態調節。

萊迪思的研發團隊發明的可程式化設計基體偏壓,能夠根據設計的功耗和散熱管理需要,讓元件以高效能模式或低功耗模式運行。只需通過軟體開關即可控制運行模式。開發人員通過對基體偏壓進行程式設計實現高效能或低功耗之間的切換,可以優化 FPGA 的功耗/效能,更好地滿足應用的功耗和散熱管理需求。這不僅有助於降低電池供電的網路邊緣設備的功耗,還能降低工業和資料中心等應用的電力成本。根據萊迪思估算,基於Nexus平台的FPGA的功耗將比同類競品減少高達75%。

| 圖一 : 可程式化設計基體偏壓讓使用萊迪思Nexus FPGA的開發人員能夠密切控制電路的電流洩漏,同時對元件進行微調,實現低功耗或高效能模式。 |

|

加速AI處理效能

為了支援AI等網路邊緣新興技術,設備的開發人員需要讓系統更加智慧。他們的做法是為系統整合更多智慧功能,從而讓設備在網路終端執行即時資料處理和分析。然而AI的設計人員面臨諸多挑戰,AI推理演算法需要大量運算,還要求具備大型記憶體模組在本機存放數值以進行運算。以前AI解決方案的開發人員需要高水準的DSP來實現演算法時,他們往往選擇外部資源,如系統中另一個處理器或者雲端。然而如此執行AI計算會導致資料延遲,此外將客戶資料發送到雲端還會引發資料隱私問題和安全隱患。

有了Nexus FPGA技術平台,萊迪思可以通過整合更大的RAM和優化的DSP模組在本機存放資料和執行運算以解決延遲問題。Nexus FPGA比之前的萊迪思FPGA效能提升了一倍(同時功耗降低一半),因此開發人員可以在網路邊緣實現AI推理演算法。網路邊緣AI推理的潛在應用包括自動工業機器人、ADAS系統、安全監視器和智慧門鈴等。

FPGA提供高穩定性

一般半導體元件由於高能粒子(如宇宙射線和α粒子)撞擊電晶體,效能會受到損害;這一現象被稱為軟錯誤。從軟錯誤中恢復需要重置FPGA,這對於那些不允許系統中斷哪怕幾毫秒的關鍵應用而言,顯然不適用。為了解決這一難題,採用bulk CMOS製程開發的元件通常會使用一些功能來校正軟錯誤,例如晶片上軟錯誤校正(SEC)和錯誤代碼校正(ECC)模組。

萊迪思基於Nexus平台的FPGA不僅支援以上功能,還擁有一層極薄的氧化物(得益於FD-SOI製程技術)保護FPGA中的電晶體,防止高能粒子對基底產生影響。因此基於萊迪思Nexus技術平台開發的FPGA與同類FPGA產品相比,軟錯誤率可降低100多倍。由此帶來穩定性的大幅提升,對於任何應用而言都不失為理想之選,尤其是汽車和工業領域的一些關鍵應用,其元件故障可能導致重大傷害和財產損失。

實現小尺寸FPGA

萊迪思Nexus技術平台還能滿足網路邊緣設備不斷精簡尺寸的需求。許多FPGA廠商都在設計產品用於資料中心(雲端)的資料分析應用,它們的架構很大,不適用於邏輯單元數量較少的小型FPGA。萊迪思則專注開發小尺寸、低功耗的FPGA,創造了緊湊的FPGA架構,其元件的物理尺寸比相似邏輯密度的FPGA競品小十倍之多。

技術平台提供完善的系統解決方案

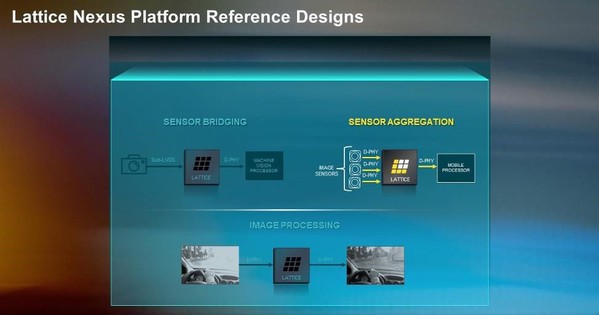

除了Nexus技術平台上電晶體結構的創新之外,萊迪思還研究了設計過程中更高層次的抽象設計,以瞭解如何協助客戶在其應用設計中快速輕鬆地應用Nexus FPGA。萊迪思已經創建或購買並驗證了易於使用、直觀的設計軟體、預先設計的軟IP模組、評估板、套件以及完整的參考設計等資源,從而實現萊迪思目標市場(通訊、運算、工業、汽車和消費電子)的各類常見應用,包括感測器聚合、感測器橋接和影像處理。

讓我們進一步瞭解圖二中的感測器聚合演示,看看這類演示如何協助客戶快速將產品推向市場。該演示主要用於嵌入式視覺系統,可以從多達四個來源獲取影片資料串流,將它們合併為一個資料串流,然後通過高速 MIPI D-PHY將其發送到顯示器或處理器以進行後續處理。

| 圖二 : 萊迪思為嵌入式視覺市場提供完整的參考設計,讓開發人員快速輕鬆地讓新產品或現有產品設計支援流行的應用。 |

|

該演示的潛在應用包括高級駕駛輔助系統(ADAS)。在此應用中開發人員需要從多個攝影機和/或雷達感測器收集、匯總資料,然後將其發送給處理器即時做出決策,保障安全。由於無須將多個感測器連接到汽車應用處理器(AP),開發人員可以簡化系統PCB上的走線,節省寶貴的AP I/O埠,從而降低系統成本,減小總體尺寸。

在軟體方面,萊迪思Nexus平台上的FPGA可搭配設計軟體和萊迪思精選的預驗證IP庫來實現該平台擬支持的各類應用。

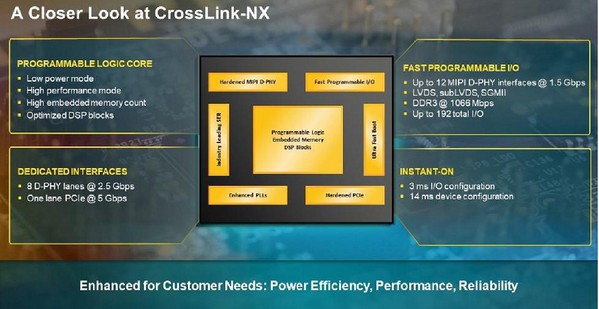

Nexus技術平台的FPGA:CrossLink-NX

CrossLink-NX作為採用萊迪思 Nexus 技術平台開發的首個新產品系列,將迎來巨大機遇。 全新的 CrossLink-NX FPGA繼承了CrossLink系列FPGA在視訊訊號橋接、拆分和聚合等應用中的優勢,同樣支援所有視訊訊號應用。得益於萊迪思Nexus開發平台,CrossLink-NX FPGA系列具有更高的儲存邏輯比、優化的DSP、更多的邏輯單元和更快的I/O,能夠使用AI演算法處理影像資料,運行速度是之前FPGA的兩倍。

此外,在工業和汽車應用中,CrossLink-NX的尺寸比上一代產品小了10倍,軟錯誤率最高降低100倍,大幅提升了可靠性。最後,為進一步加快產品上市時間,萊迪思提供Diamond 2.0 FPGA開發工具、經過驗證的IP模組以及基於CrossLink-NX FPGA的應用參考設計。

| 圖三 : CrossLink-NX系列FPGA是首款基於萊迪思Nexus技術平台開發的產品,用於AI和嵌入式視覺應用。 |

|

結論

如今,快速發展的網路邊緣設備市場在要求更高效能和可靠性的同時,希望設備具有低功耗和小尺寸的特性。萊迪思向來注重幫助開發人員將智慧、低功耗網路邊緣設備推向市場,服務各類應用。隨著 Nexus平台的推出,萊迪思半導體可以快速開發新的FPGA,開發人員也可以加速產品開發,滿足新的市場需求。萊迪思Nexus平台的推出,重新定義了開發人員對小尺寸、低功耗FPGA的期望。