今日的嵌入式產品與幾年前的產品相比較,要來得更複雜和精密。這類設計可能會包括現場可程式化閘陣列(FPGA)晶片及一個分開的圖形處理器(GPU),再加上多種連接埠,如視頻端子、USB、Wi-Fi、高速有線乙太網路,或甚至工業用ModBus或FieldBus。這些每一個處理器和子系統都需要不同的時脈頻率和類型,彼此之間卻不相關連,因此各有其不同的時脈訊號需求。設計這樣的系統─產生精密效能的不同時脈,並給予這些時脈個別的負載─是產品工程師所需面對的新增的挑戰。

用直接明顯的方式提供這些時脈,看起來似乎很簡單:使用所需的時脈產生器,無論多少個,並將每一個時脈置放於印刷電路板(PCB)目標負載的旁邊,或使用以主時脈驅動的時脈樹即可。這樣做可解決多時脈的問題,至少理論上是如此,因為這可滿足每一個負載設備的需求,其方法為使用訂製的時脈訊號以符合特殊的需求。每一個時脈來源被安置在它負載的附近,因此時脈群體中的以及時脈之間的串擾和訊號就會降低,因而將增加的時脈抖動和畸變降至最低。

針對每一個目標負載使用一個時脈IC的解決方案似乎很吸引人,但它也有很多負面影響:

1. 多個且個別分開的時脈產生器IC會有直接的材料成本問題,且管理和取得這些不同IC的後勤作業也會是個問題。

2. 這需要有相當大量的印刷電路板空間,而這條件幾乎是所有設計上的顧慮。

3. 若使用個別的單一輸出的時脈產生器,而不是使用分散式的時脈樹,那麼每一個時脈需要有自己的晶體,這會造成更多的成本和電路板空間需求。

4. 使用一個「時脈樹」來產生所有最後的時脈會增加成本、炭足跡、以及時脈抖動和誤差累積。

5. 使用多重IC會增加總功耗。

6. 使用多重時脈產生器IC會讓供應商在橫跨不同產品的生產線上系統設計的再使用變得較困難,因為每一個新的設計可能會有不同的佈局和時脈組件。

這些每一個因素在設定的情況下其重要性是由設計、其優先考量、和其利弊得失的權衡所決定。使用一個時脈產生器加上對每一個獨特時脈所需的晶體,做這樣的決定,在多處理器系統中會有許多意想不到的後果。

提供優勢的替代方案

幸好有另一個方法能有效克服在多處理器設計中使用獨立分開時脈產生器IC所帶來的缺點。用一個多路輸出、可編程時脈產生器可從單一晶體中提供獨立的輸出,因此可替代兩個、四個,或更多個時脈。這些IC有許多不同的輸出選項、組態、頻率區間,可使用於不同的應用目標。

就一個多路輸出時脈產生器而言,其功能要能夠符合各種時脈負載的需求,是一件很重要的事。在許多的設計中,各種的負載不僅理所當然地有不同的頻率,而且亦有不同的電壓、格式、上升/下降最大時間和抖動等規格。高端FPGA或SoC對所使用的時脈,相較於相同設計中低速路通訊連結的產品,其規格需求會更嚴謹得多,而設計者會選擇可符合所有需求的單一時脈產生器IC。

最新世代的可編程時脈產生器能夠做到這點,特別是能夠符合困難的需求。例如:Xilinx的Virtex-6和Virtex-7 FPGAs就包括了數據傳輸數率介於480Mbps~6.6Gbps和2.488Gbps~11.18Gpbs之間的無線收發器、每通道原始數據速率可達5.0Gbps的PCI Express Base、以及可支援10/100/1000 Mbps連結的乙太網路MAC區塊。

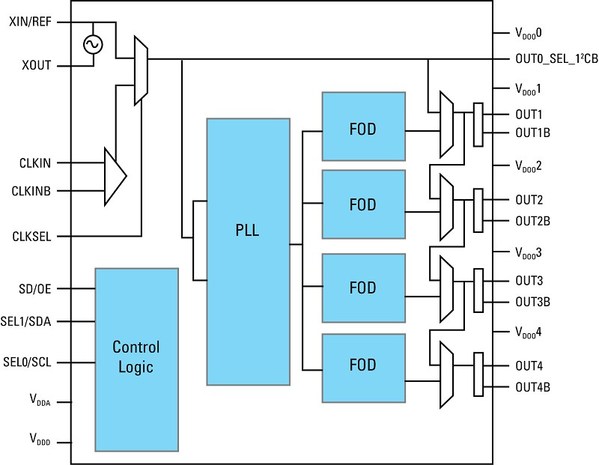

為了符合設計者以這些FPGA為基礎的線路設計需求,IDT提供了VersaClock 6 系列的可編程時脈產生器,如圖1所示。此款VersaClock 6 時脈產生器可提供二到八個可設定組態的輸出(可選擇LVDS或LVPECL),以及依據所選擇的特定設備,可提供二個、三個或四個一次性可編程(OTP)組態。所有這些時脈產生器皆具有分數輸出分頻器架構以達到最大彈性,且可產生介於1和350MHz之間的任何頻率。此產品系列最值得一提的特性是其對RMS相位抖動低於500 fsec(0.5 psec)規格的保證。

| 圖1 : IDT的VersaClock 6 系列時脈產生器,特性為二到八個可組態設定的LVDS或LVPECL 輸出,每一輸出具有1~350MHz的使用者可編寫頻率。 |

|

應用實例說明

必須支援SMPTE 424標準的設計是最佳的例子,說明使用可編程多路輸出設備所帶來的這些好處。此一標準,亦稱為3G-SDI,針對高效能3Gbps的SerDes(串行器/解串器)功能,有非常嚴格的眼抖動規格,以符合所需的誤碼率(BER)目標。

SMPTE(the Society of Motion Picture & Television Engineering)是國際認可的標準組織,其管轄之規格,包括數據電視傳輸(通常稱為SDI或Serial Data Interface)的高速串行物理介面。該組織主要的任務包括:

‧ 針對從10Hz到100kHz,峰值到峰值2.0 UI最大值的時序抖動規範。

‧ 針對從100kHz到297MHz,峰值到峰0.3 UI 最大值的校準抖動規範;並建議使用0.2 UI。

(單元區間(Unit Interval - UI)是兩個相鄰的訊號轉換之間的時間,以及時脈頻率的倒數。)

在更多技術性挑戰的情況下,許多廣播視頻設計需要支援NTSC和PAL的HDTV標準,也就是說必須同時具有148.5MHz和148.5/(1.001)MHz的參考時脈。此外,支援IP視頻(Voice-Over-IP;VoIP)的廣播視頻產品趨勢意謂著這些設計可能也需要支援10GE PHYs (10 gigabit Ethernet Physical Layer),因此一個額外的156.25MHz參考時脈通常是必需的。

因為整合了高效能的GTX/GTH/GTP無線收發器,Xilinx 7系列的FPGA經常被選擇用於這些符合SMPTE規格的設計。為了要符合SMPTE 424的眼抖動規格,Xilinx對使用於驅動這些SerDes功能的參考時脈指定了非常嚴謹的dBc/Hz相位噪音要求。

如果相同的Xilinx 7系列的GTX/GTH/GTP 無線收發器亦用於10 Gbps的SerDes,那麼這非常嚴謹的dBc/Hz 相位噪音需求就會再次顯得非常關鍵。這些非整數相關時脈頻率(148.5 MHz、148.351648 MHz、156.25MHz),當與每個時脈非常嚴謹的相位噪音需求結合時,針對提供一個整合性的時脈解決方案,就會構成一個工作要項。

幸運的是,有個單一裝置能夠將這些高效能時脈合成在單一設備之中:IDT的Universal Frequency Translator(UFT)系列高端PLL產品。此系列產品可用來做為高效能合成器,只需要一個簡單、基本模型的並行諧振晶體作為它的輸入參考即可。

UFT系列產品針對每個PLL支援一個或兩個不同的可選擇引腳組態,且可預先載入內部一次性可編程(OTP)的非揮發性記憶體,用於電源啟動的自動運轉,且其I2C 串行介面可用於設定所需的頻率轉譯組態。

針對SMPTE 424規格的設計,IDT的8T49N241可用來作為高效能,四路輸出的合成器,可明顯減省電路板空間和降低設計複雜度。此系列產品的時脈裝置在此高難度的應用中具有 Xilinx 7系列參考時脈所需的效能。

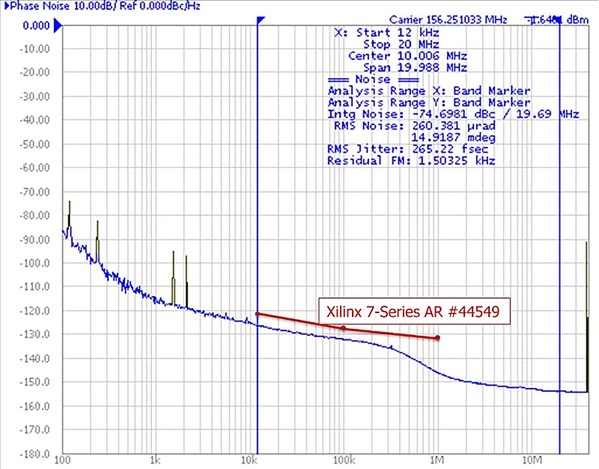

圖 2顯示一個典型的相位噪音圖像,取自IDT UFT時脈裝置所產生的156.25MHz輸出時脈。此相位噪音圖像遠低於定義在Xilinx Action Note AR# 44549中的相位噪音遮罩。

| 圖2 : IDT UFT時脈IC所產生的156.25MHz輸出時脈的典型相位噪音圖像,其超過Xilinx Action Note對遮罩的規格需求。 |

|

若設計者選擇具多路輸出的單一時脈產生器IC,那麼使用獨立分開的時脈IC所產生的許多問題就會消失或變得單純得多了。此外,因為增加了時脈IC的可編程性,相同的組件和配置可用於橫跨多種類或升級的產品上。

當設計者使用單一時脈IC時,必須記住一件事情。這IC的實體位置和印刷電路板針對各種輸出的個別負載的電路佈線必須事先建模並進行模擬測試。這樣做是必須的,以維持時脈訊號的完整性,並將串擾和噪音對抖動的影響降至夠低的水平。所幸這些高速率訊號和設計佈建的模擬工具是可取得的,使得這樣的模擬測試可行,且亦有助確保非時脈訊號的整體設計效能。

工具、易使用性也是設計的考量

很明顯地,一個使用者可編程的,可完全作組態設定的IC ,譬如時脈產生器,如果它無法提供容易的編程或組態設定,這對使用者來說是令人沮喪的。IDT的Timing Commander 軟體讓客戶可以直覺和彈性的使用者圖形介面(GUI)對裝置做組態設定和編程。

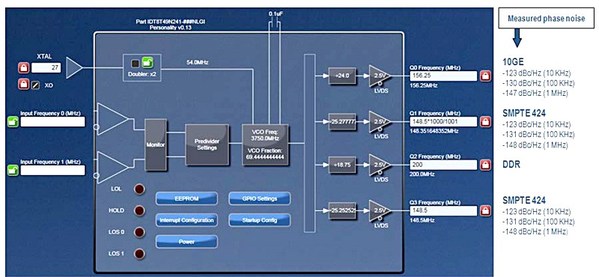

圖3顯示一個螢幕捕獲的圖形,舉例說明此平台的GUI在SMPTE 424應用中,作為高效能四路輸出合成器,用於8T49N241的組態設定。此分數回饋PLL與整數和分數輸出分頻器混合的組合使得8T49N241可產生所有這些0 ppb (十億分之幾)添加合成錯誤的輸出頻率,且所測得的10GE和SMPTE 424時脈的相位噪音效能符合Xilinx 7 系列的規格需求。

| 圖3 : 在對SMPTE設計作組態設定時,IDT Timing Commander GUI使用分數回饋PLL與整數和分數輸出分頻器混合的組合以產生所需的輸出頻率。 |

|

此外,系統內的I2C可編程模式可在電源啟動時用於編寫一些多路輸出裝置,以覆蓋一次性的可編程(OTP)記憶體組態,因此在需要時可重新設定設備的組態。最後,使用者可在每一個輸出配對另外編寫獨立的擴頻功能,以減弱系統層次的EMI/RFI水平和相關的顧慮,當然這也是依據所選擇的設備而定。

使用者可編程性以多種方法便利多處理器系統設計者的工作,並克服許多因使用個別獨立時脈產生器所遭遇到的缺點,且不會犧牲效能。此一可編程性以單一設備支援不同的負載類型和需求,因此「哪種時脈適合甚麼類型?」這樣的問題就可獲得解決了。它們當然可對頻率作客製化,也可針對關鍵性的設計規格,如成本效益、執行效能和能源效率予以客製化,而無需像其他產品需要太多的效益妥協。

(作者Baljit Chandhoke 為IDT公司時脈產品產品線經理)

參考文獻

1. AN-815, "Understanding Jitter Units," http://www.idt.com/document/apn/815-understanding-jitter-units

2. AN-827, "Application Relevance of Clock Jitter," http://www.idt.com/document/apn/827-application-relevance-clock-jitter

3. AN-839, "RMS Phase Jitter," http://www.idt.com/document/apn/839-rms-phase-jitter

4. AN-840, "Jitter Specifications for Timing Signals," http://www.idt.com/document/apn/840-jitter-specifications-timing-signals

5. "IDT Clocks for SMPTE and XilinxR 7 Series FPGAS," http://www.idt.com/document/idt-clocks-smpte-and-xilinx-7-series-fpgas

6. "Xilinx Action Note AR# 44549," http://www.xilinx.com/support/answers/44549.html