瀏覽人次:【10105】

為什麼要轉換?

最主要理由就是市場與消費者對嵌入式產品複雜度的要求升高。隨著嵌入式產品連網需求增加,並提供更多功能,目前的8位元與16位元微處理器已不敷處理需求。就算8位元或16位元微處理器可勉強滿足目前的要求,但很有可能限制未來的產品升級機會,並限制開發程式碼的再利用。

第二個常見的理由就是嵌入式系統開發商發現轉換至32位元微控制器的好處。32位元微控制器不僅可提供10倍以上的效能,並能降低功耗、縮小程式體積、加快軟體開發時程且提升軟體之再使用率。另外則是內建ARM裝置提供的多選擇性、範圍與可取得性。現在越來越多微控制器供應商開始供應採用ARM架構的微控制器。這些產品在週邊設備、效能、記憶體大小、封裝與成本方面,皆提供更多選擇。

此外,採用ARM Cortex-M系列處理器有一些功能是專門針對微控制器應用所設計。這些功能使採用ARM微控制器的應用範圍更廣且為數更多。同時,過去五年來採用ARM微控制器的價格已大幅下降,且有越來越多低成本甚至免費的開發工具可供開發人員使用。

指令長度

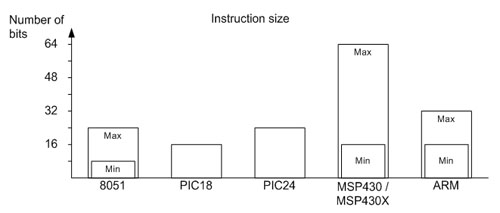

許多人認為8位元微控制器使用8位元指令,而32位元微控制器則使用32位元指令。事實上,許多8位元微控制器使用指令為16位元、24位元或其他大於8位元的長度,舉例來說,PIC18的指令長度為16位元。即便是已過時的8051基礎架構,有些指令為1位元組,但其他許多指令則是2或3位元組。這道理也適用於16位元架構,舉例來說,有些MSP430指令需要6位元組(SP430X甚至需要8位元組)。

ARM Cortex-M3與Cortex-M0處理器採用Thumb-2技術,提供絕佳的程式碼密度。處理器運用Thumb-2技術可支援Thumb指令集,包括16位元指令以及32位元指令,當中32位元指令的功能為16位元版本的超集(uperset)。多數情況下,除非只能執行32位元,C編譯器(C compiler)都會使用16位元版本的指令。

《圖一 各處理器中單一指令的長度》

|

在Cortex-M處理器的編譯程式中,32位元指令的數量僅佔總指令的一小部分。例如,針對Cortex-M3編譯的Dhrystone編譯程式中,32位元指令僅佔總指令的15.8% (平均指令長度為18.53位元)。就Cortex-M0而言,32位元指令所佔比例更低,僅5.4%(平均指令長度為16.9位元)。

指令集效率

ARM Cortex-M微控制器所使用之Thumb指令集效率相當高。例如,ARM微控制器的多重載入指令(multiple load instructions)、多重儲存指令(multiple store instructions)、stack push與stack pop指令都允許單一指令執行傳輸多個資料。

強大的記憶體定址模式(memory addressing modes)亦允許ARM微處理器簡化記憶體存取序列(memory access sequences)。舉例來說,記憶體可在單一指令下以暫存器偏移(register offset)、立即值偏移(immediate offset)、PC相關或堆疊指標(stack pointer)相關(可用於區域變數)之定址模式來存取。額外功能還包括記憶體指標(memory pointers)之自動調整。所有的ARM處理器皆能以高效率處理8位元與16位元資料。

也有針對帶正負號(signed)與未帶正負號(unsigned)的8位元、16位元與32位元資料之緊湊記憶存取指令。還有加入一些專門針對資料類型轉換的指令。整體來說,ARM處理器中,8位元和16位元資料的處理,與32位元資料的處理一樣容易有效。

ARM Cortex-M微控制器亦提供強大之條件執行(conditional execution)功能。除了針對帶正負號(signed)與未帶正負號(unsigned)資料提供完整的ARM微控制器之分支條件(branch conditions)選擇,ARM Cortex-M3微控制器亦提供條件執行、結合比較及分支指令。

Cortex-M0與Cortex-M3皆支援32位元單一循環乘法運算(singe cycle multiple operation)。此外,Cortex-M3微控制器亦支援帶正負號與未帶正負號整數除法(signed and unsigned integer divide)、飽和(saturation)、32與64位元乘法累加(multiply-accumulate, MAC)運算,以及許多位元欄位(bit field)運算指令。

8位元應用迷思

許多嵌入式開發人員誤以為他們的應用程式只執行8位元資料處理,因此毋須改為32位元處理器。但深入了解C編譯器手冊後便會發現,humble integer其實是8位元微控制器上之16位元,所以每次執行整數運算或存取需要整數運算的C Library功能時,您其實是在處理16位元資料。8位元處理器核心必須使用序列的指令以及更多時脈週期,以執行同等需求之處理量。

指標(pointers)亦是如此。在多數的8位元或16位元微控制器中,一個定址指標至少需要16位元。若使用的是8051裡的一般記憶體指標,或用memory bank switching,或以類似的技術來克服64k位元組的記憶體屏障(memory barrier),就還會需要更多位元。因此,8位元系統的記憶體指標處理效率相當低。

由於暫存器庫(register bank)裡的每個整數變數都需要多重暫存,在 8位元微控制器裡使用整數亦會導致更多記憶體存取、更多記憶體讀/寫指令與更多堆疊運算(stack operations)所需之指令。這些都會大幅增加8位元微控制器上的程式碼長度。

該如何用特定指標範例來作統整比較呢?舉例來說,針對各個基礎架構編譯之Dhrystone程式,經過長度最佳化後會導致以下結果:

(表一) 各個基礎架構編譯之Dhrystone程式

微控制器 |

SiliconLabs C8051F320 |

Cortex-M0 |

Cortex-M3 |

工具 |

Keil µVision 3.8 PK51 8.18 |

RVDS 4.0-SP2 |

RVDS 4.0-SP2 |

二元輸出大小(位元組) |

3186 |

912 |

900 |

多數嵌入式應用都因改採ARM Cortex-M微控制器而獲益,主要因為程式碼長度縮短,因此只需要較少記憶體的低價裝置。由於指令集效率提高、指令長度縮短,以及在多數嵌入式應用中處理16位元或更大資料的需求,程式碼長度因而得以縮減。

效能與功耗

促使許多嵌入式系統開發商放棄8位元與16位元微控制器而改用32位元微控制器的原因之一,為需要提升其產品的效能。以下將探討ARM微控制器與其他微控制器在效能方面的比較,以及ARM微控制器如何協助降低功耗。

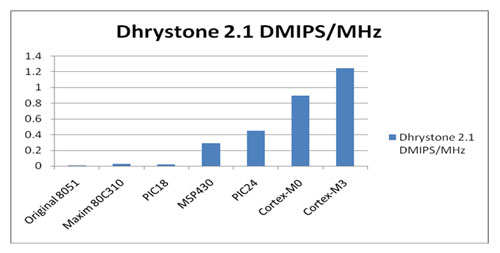

效能

一種常見的方式是利用Dhrystone指標來比較微控制器的效能。Dhrystone指標為免費工具,易於使用且體積小,置入微控制器後所佔記憶體空間極少。原始的8051效能僅有0.0094 DMIPS/MHz。較新之8051s效能則略為提升,舉例來說,Maxim 80C310裝置之DMIPS為0.027,速度最快的8051微處理器宣稱其Dhrystone效能為0.1 DMIPS/MHz。此速度還是比ARM Cortex-M微控制器慢的多,ARM Cortex-M的Cortex-M3處理器最大效能為1.25 DMIPS/MHz,而Cortex-M0處理器則可達0.9 DMIPS/MHz。

《圖二 使用Dhrystone之基本效能比較》

|

8位元與16位元微控制器的限制

一般來說,8位元微控制器處理16位元與32位元資料的效率很低。每次處理整數變數或指標時,便需要一序列的指令,導致效能降低及程式碼加大。

另一個造成許多8位元與16位元微控制器低效率的原因,在於指令集與程式設計師使用模型之限制。例如,8051大幅仰賴累積器(ACC)與資料指標暫存器(DPTR)進行資料轉移與處理。因此需要指令將資料移入/出ACC與DPTR,便成為程式碼大小與執行週期的經常負載。

記憶體介面本身也會限制8位元與16位元處理器的效能。例如,許多8051指令需要多個位元組。因為程式記憶體介面為8位元,儘管指令本身是很簡單的運算,記憶體仍需多次讀取,進而需要多次時脈週期來取得指令。

若需存取64K位元組以上之記憶體,8位元與16位元微控制器之效能將更為降低。這些基礎架構是設計來配合16位元定址。若需要64k位元組以上之記憶體,便需額外的硬體與指令負載以產生額外的定址位元。針對需要存取64k位元組以上記憶體的典型8051,記憶體會分成不同的記憶庫,所有的記憶庫的開關碼(bank switching code)執行都需透過記憶庫#0(bank #0)。這將導致程式碼長度增加與時脈週期負載變大,進而降低記憶體使用效率。有些16位元微控制器的變通辦法,是使用更大的程式計數器或用記憶體分段(memory segmentation),但操作大型定址數值仍需額外的處理,因此降低效能並導致程式碼增加。

低功耗

ARM處理器針對低功耗設計,採用許多低耗電技術。舉例來說,Cortex-M0與Cortex-M3處理器支援休眠模式,及重返休眠模式(sleep-on-exit)。

為了解Cortex-M微控制器如何降低嵌入式系統的功耗,最好先從典型的微控制器產品內部結構開始研究。新型的微控制器中,處理器核心已不佔據最大的面積。

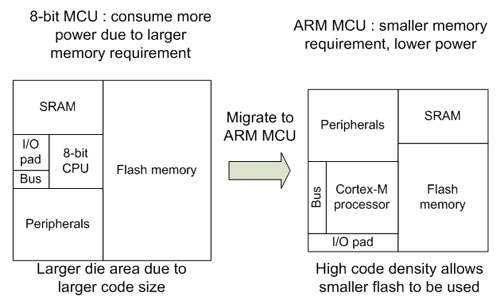

《圖三 使用ARM Cortex-M處理器可減少矽面積》

|

由於8位元微控制器的程式碼密度不高,因此便需要更大的快閃記憶體,進而增加整體功耗。ARM微控制器的程式碼密度高,可使微控制器利用較小之快閃記憶體,並同時降低功耗與成本。

記憶體存取效率

藉由減少記憶體存取次數並利用32位元匯流排以降低功耗。若要在記憶體裡拷貝等量的資料,8位元微控制器需要四倍的記憶體存取,且拷貝運算需要更多指令提取(instruction fetches)。因此,即使記憶體大小相同,8位元微控制器需消耗更多電力才能達到同樣的結果。

Cortex-M微控制器裡的指令提取效率也遠比8位元與16位元微控制器更高,由於每一次指令提取是32位元,每次循環允許提取最多兩個16位元Thumb指令,並讓資料存取有更高的匯流排頻寬。針對同樣長度的指令序列,8位元微控制器需要使用四倍的記憶體存取次數,16位元微控制器需兩倍指令提取次數。因此,8位元與16位元微控制器所需之功耗遠比ARM微控制器高。

降低操作頻率以降低功耗

32位元微控制器的高效能允許在低時脈頻率下執行應用程式以降低功耗。舉例來說,某應用程式在8051上以30MHz執行,但在ARM Cortex-M3微控制器上只需3MHz時脈頻率,且效能仍可達到同樣水準。

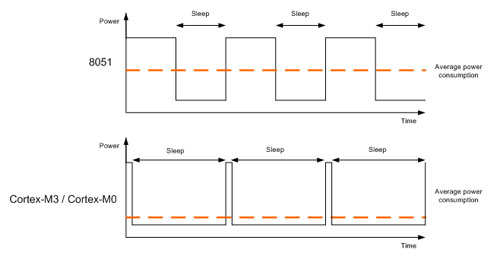

減少動態循環以降低功耗

此外,工作處理完成後,可利用ARM微控制器的休眠模式進一步降低耗電量。與8位元及16位元微控制器相比,Cortex-M微控制器的效能更高,因此完成工作後可更快進入休眠模式,進而降低整體系統動態循環數量。

《圖四 Cortex微控制器可藉由減少動態循環來降低系統功耗 》

|

軟體開發與總結

ARM Cortex M0微控制器的軟體開發,較8位元微控制器產品容易。Cortex-M處理器不僅可做完全的C程式語言設計,亦有各種進階除錯功能,協助搜尋軟體中產生的問題。網路上亦有許多範例與教學,包括ARM微控制器供應商的網站,以及微控制器開發工具組等額外資源。

將軟體從8位元或16位元微控制器移至ARM

與簡單的8位元微控制器相較,ARM Cortex-M微控制器在週邊設備擁有較多暫存器。ARM微控制器的週邊設備通常具備較多功能,因此有更多可排程暫存器。但是ARM微控制器供應商可提供裝置驅動程式資料庫,利用幾個函式呼叫(function calls)就能協助設定週邊設備。

與大部分的8位元與16位元基礎架構相比,ARM微控制器程式設計更具彈性。舉例來說, 它沒有硬體堆疊限制,函式可以遞迴方式存取,除此之外,軟體部分不用特別去對針對暫存器中的資料做儲存的動作,因為在進入中斷時,CPU會以硬體的方式儲存這些暫存器值。舉例來說,若是MSP430,可能需在乘法運算過程中關閉中斷;若是PIC,軟體人員則需在中斷處理前儲存table pointers及乘數暫存器中的資料。

針對基礎架構正確使用資料種類,將對程式碼長度與效能帶來重大影響。某些資料種類的大小在ARM微控制器與8位元/16位元微控制器分別是不同的。

(表二)

資料種類 |

8位元/16位元微控制器 |

ARM微控制器 |

整數 |

16位元 |

32位元(16位元則使用短整數short int) |

列舉型別 |

8位元/16位元 |

8位元/16位元/32位元 |

指標 |

16位元或更多 |

32位元 |

雙精度浮點數 |

32位元(使用單精準度) |

64位元(32位元則使用浮點) |

舉例來說,若某應用程式在8位元/16位元微控制器的整數溢位(overflow)在16位元範圍內,那麼該程式碼變數宣告型態需經調整才能在ARM微控制器上達到最佳化執行。

另一個資料大小差異帶來的影響在於資料陣列(data array)大小。舉例來說,在8位元微控制器應用程式之ROM整數陣列定義如下:

const int mydata = { 1234, 5678, …};

但若是在ARM微控制器上執行,為了避免不必要的ROM大小增加,該定義則應修改如下:

const short int mydata = { 1234, 5678, …};

浮點指令的差異也會導致計算結果產生些微差距。由於8位元與16位元微控制器的效能差異限制,若使用雙精度(double),它會以單精度(32位元)處理。在ARM微控制器裡,雙精準度(double)資料類型為64位元,因此對於32位元浮點應改用單精準度類型(float)。這個差異也會影響數學函式。舉例來說,以下來自Whetstone之程式碼會在ARM微控制器上產生雙精度數學函式:

X=T*atan(T2*sin(X)*cos(X)/(cos(X+Y)+cos(X-Y)-1.0));

若為單精度,該程式碼應改為

X=T*atanf(T2*sinf(X)*cosf(X)/(cosf(X+Y)+cosf(X-Y)-1.0F));

除錯

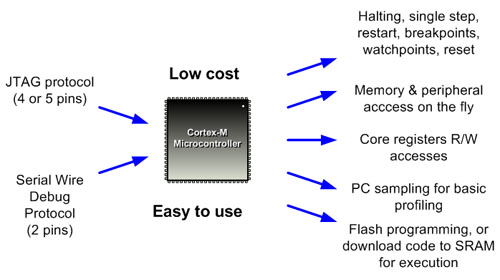

對某些使用者來說,選擇微控制器的關鍵考量之一為除錯支援。ARM Cortex-M微控制器支援全面的除錯功能,包括硬體中斷點、觀察點、暫存器存取與即時記憶體存取。除錯方式採用JTAG或Serial Wire協定,以及標準化的Cortex除錯阜安排,使得目標板易於與除錯軟體(debug hosts)連結。

《圖五 Cortex-M微控制器的除錯功能》

|

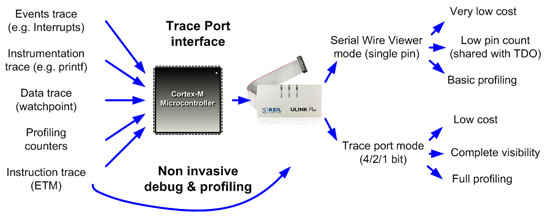

追蹤支援為Cortex-M3使用者提供額外的除錯功能。基本的Cortex-M3處理器支援可選擇之資料追蹤、事件追蹤、例外追蹤以及純文字輸出追蹤。追蹤資料可由單一pin腳直接收集,此種方式稱為Serial Wire Output (SWO),SWO和JTAG/SWD接頭共用pin腳。如此一來,程式執行資訊可被低成本之除錯硬體紀錄,而不需額外之追蹤硬體。

許多Cortex-M3微控制器亦支援Embedded Trace Macrocell(ETM),擴大追蹤支援至完整之指令追蹤。此功能可詳細分析應用程式碼執行,並允許執行程式碼剖析(code profiling)。因為Cortex-M0與Cortex-M3的相似性,可在Cortex-M3上用指令追蹤來開發應用程式並加以除錯,稍作修改後便可將該應用程式匯入Cortex-M0。

《圖六 追蹤功能提供高能見度》

|

選擇

採用ARM微控制器最大的優勢之一為多樣選擇性。可提供Cortex-M微控制器的廠商越來越多,搭配各種週邊設備、介面、記憶體大小、封裝以及頻率範圍。可提供之編譯器套件包括從免費或低成本套件,到多項進階功能之專業編譯器套件。嵌入式作業系統、編碼器與中介軟體廠商也提供更多的支援服務。

軟體可攜性

ARM Cortex-M微控制器亦提供高度軟體可攜性。雖然微控制器廠商為數眾多,但都有各自的裝置驅動程式資料庫,也有許多C編譯器廠商提供的各種編譯器套件,但仍可透過Cortex微控制器軟體介面標準(Software Interface Standard, CMSIS)輕鬆匯出/匯入軟體。

許多微控制器廠商提供之微控制器裝置驅動程式資料庫皆有CMSIS。它為核心函式與核心暫存器提供軟體介面,並為標準化系統提供例外處理器名稱。用CMSIS開發的軟體可輕易在不同Cortex-M微控制器之間轉移,並允許嵌入式作業系統或中介軟體產品同時支援多家廠商與多個編譯器套件。它亦提供更高的軟體再使用率,以確保軟體開發投資。

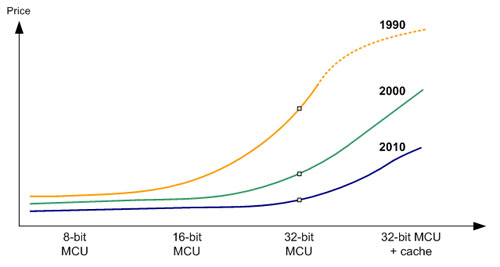

轉移成本

近年來,技術的進步使ARM Cortex微控制器所需成本與8位元及16位元微控制器相當。這也是因為越來越多使用者對於高效能、多功能微控制器需求增加,導致產量大幅上升,進而降低單位成本。

《圖七 32位元微控制器價格大幅降低》

|

目前已針對ARM Cortex-M微控制器提供許多低成本開發系列及免費開發套件。同時,由於Cortex-M微控制器易於使用且效能良好,也縮短了產品開發時間,因此可降低整體產品開發成本。

總結

從8位元微控制器轉換至ARM Cortex-M微控制器,可提供更高的效能,並能以低成本開發進階軟體,亦可降低功耗及縮短程式碼長度。轉換至16位元基礎架構或32位元基礎架構則無法提供同等效益。

(表三) ARM架構為控制器比較表

|

8051 |

其他8位元 基礎架構 |

16位元基礎架構 |

其他32位元 基礎架構 |

ARM Cortex

微控制器 |

效能 |

○ |

○ |

⊙ |

● |

● |

低功耗 |

● |

● |

● |

○ |

● |

程式碼密度 |

○ |

○ |

⊙ |

○ |

● |

>64k位元組記憶體

(原始、效率) |

○ |

○ |

○ |

● |

● |

向量中斷 |

● |

● |

● |

⊙ |

● |

低中斷延遲 |

● |

● |

● |

○ |

● |

低成本 |

● |

● |

● |

○ |

● |

多來源

(非專有基礎架構) |

● |

○ |

○ |

○ |

● |

編譯器選項 |

● |

⊙ |

⊙ |

⊙ |

● |

軟體可攜性 |

● |

⊙ |

⊙ |

⊙ |

● |

從8位元轉至16位元基礎架構僅能解決部分8位元微控制器帶來的限制。16位元基礎架構在處理大記憶體(> 64k位元組)時同樣會產生效率不足的問題,且通常為專有基礎架構,限制了裝置選擇性及軟體可攜性。其它32位元微控制器基礎架構的中斷功能、能源效率、系統功能與軟體支援等亦十分落後。

展望未來,市場上將有更多Cortex-M微控制器產品,並且會有更多嵌入式系統專案改採ARM架構。

---本文作者為ARM工程師---

|