隨著越來越多的系統整合多個IC,系統功耗也不斷增加,這是目前全球關注的問題。除了帶來環保影響外,功耗增加也會增加系統構建及運營成本。想要散去多餘熱量,就必須使用複雜的散熱片、風扇甚至更多的穩壓器,而這些都會增加資本支出、運營支出。包括設備運行以及降溫所需的電力,也會隨著總功耗的增加而增加。此外,系統過熱會降低可靠性,及增加系統停機風險,並提高運營成本。

28nm破除FPGA靜態功耗罩門

另一方面,摩爾定律的不斷延續,新一代半導體製程技術都會提高整合度,以降低成本。不過,上述優勢往往會被增加的靜態功耗抵消。每次縮減外形尺寸,似乎不可避免地都會提升靜態功耗,這種現象在FPGA產業中尤為明顯。一直以來,FPGA產業在採用最先進製程技術為客戶提供更高效能及容量方面一直處於半導體產業的領先地位。後來,系統設計人員發現,由於功耗原因,他們很難充分運用更高的密度和電路速度。支援新一代系統的關鍵在於為設計人員提供更高的「可用效能」,也就是說,要在可用功耗預算範圍內提供盡可能高的資料處理能力。降低靜態功耗可為動態功耗留下更多功耗預算,從而提高可用效能,進而也能提高介面頻寬,並為同一FPGA中的邏輯、記憶體、DSP及其他功能提供更多資源。

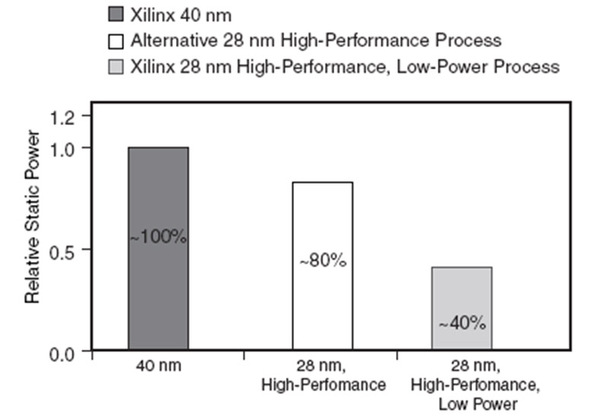

FPGA設計的關鍵挑戰在於管理動態功耗的同時,控制靜態功耗的提升,靜態功耗完全是開銷,對效能毫無助益。不幸的是,製程提升反而會增加靜態功耗。事實上,在某些情況下,靜態功耗的提升幅度還會超過動態功耗,參見圖一。

在28nm節點出現之前,FPGA產業嘗試透過降低電源電壓和多重電晶體臨界電壓來解決功耗提升問題,並成功達成目的。不過,隨著28nm製程出現,就必須採用新的方法。

為了解決28nm製程技術的可用效能問題,開發了針對FPGA的HKMG高效能低功耗28nm製程技術。此最新28nm製程技術建立在40nm FPGA製程開發的成功基礎上,並推出最新 HKMG技術,透過降低功耗能最大限度地提高可用的系統效能。該技術相對於其他製程技術而言,能大幅降低靜態功耗。就28nm節點而言,靜態功耗往往占元件總功耗的絕大比例。因此,要想最大化功率效率,製程技術的選擇至關重要。

28nm FPGA製程技術:HKMG

傳統的FPGA製程技術在28nm製程上已經達到功率極限,也達到效能極限。問題根源在於幾十年來用於構建IC電晶體的多晶矽閘極和氧氮化矽閘極電介質(Poly/SiON)。

為了提高電晶體速度,半導體工程師一直在隨著製程技術的提高努力減小閘極介電層的厚度。不過,由於介電層通道效應和閘極本身的漏電流,電介質厚度減少會導致漏電流增加,這就會造成製程技術每次節點進步都會大幅提升靜態功耗。

新一代FPGA以三重閘極氧化層電路技術成功控制隧道電流效果,從90nm製程到 40nm 製程節點一直都比較成功。不過,就28nm製程而言,閘極氧化層太薄,必須用最新閘極材料和架構來處理隧道效果。為了控制閘極下的漏電流(低於閾值的漏電流)。

為了解決28nm製程問題,採用了二氧化鉿這種新型閘極介電材料,該材料的介電常數(κ)較高,可增減閘極厚度,這就使電晶體不太容易受到隧道電流效應的影響。舉例來說,40nm 製程使用的二氧化矽κ值為3.9,而28nm 金屬閘技術所用的二氧化鉿κ值則為25,這就成為高效能低功耗28nm製程技術的最佳選擇,如圖二所示。

仔細評估多種28nm製程技術,其中包括標準的低功耗(LP)和高效能(HP)製程,最後決定採用28nm HKMG高效能低功耗製程技術。28nm LP製程是Poly/SiON 40nm技術的簡單升級,風險較低,但該技術不適用於FPGA,因為其電晶體切換速度太慢,效能不夠高;28nm HP技術專為實現高效能而最佳化,但又會造成功耗過高,也限制了可用效能,如圖三所示。

| 《圖三 40nm和28nm製程技術實現同樣效能的靜態功耗比較》 |

|

28nm HP製程技術還需要將HKMG與SiGe應變技術整合。兩種高級技術在製造製程中整合,相對於採用HKMG和應力襯墊應變技術的高效能低功耗28nm製程技術而言,會存在更多風險。

解決兩難困境:以更低功耗實現更高效能

FPGA設計旨在滿足汽車、廣播、消費、工業、醫療、測試與測量、視訊、有線通訊和無線通訊等不同市場的多種不同應用需求。28nm FPGA產品是透過上述市場領域中眾多客戶的協助所定義而來,其目標就是降低一半功耗,而系統效能則提升一半甚至更高。為了滿足28nm FPGA的介面效能要求,除大幅提升時脈技術,並決定加強關鍵資料路徑元件,從而大幅改善外部記憶體介面,可將整體系統效能提升一半以上。

就許多高效能微處理器而言,最重要的設計特性就是原始的核心速度。與此形成對比的是,FPGA可以適當地翻轉率執行高效能資料處理任務;設計人員可充分發揮FPGA架構內在的並行處理優勢來建立較寬的資料路徑,而時脈運行速度則遠遠低於輸入輸出線速。由於元件容量提升2倍,因此28nm技術能支援更高的流水線和並行處理能力,進一步提升核心效能。這類似於微處理器領域採用多核心設計的發展趨勢,雖然每個核心的工作頻率降低,但整體效能卻超過單一一個高強度運行的核心。

除了高效能低功耗製程技術外,28nm FPGA還受益於時脈閘技術以及最新的佈線演算法,可進一步降低功耗。精細時脈閘控技術(Fine-grain clock gating technology)是一種專利演算法,可分析邏輯方程式並禁用無益於最終結果的多餘邏輯轉換。由於刪除不必要的邏輯工作,從而能將功耗平均降低 20%,如下圖四所示。

通過驗證的方法:加速 28nm FPGA 上市時程

對晶片測試工具的智慧使用,可確保在FPGA產品推出之前很早就做好技術準備,並對包括元件效能、設計/製程範圍、晶片內建變化、製造設計(DFM)、關鍵模組驗證、製程和產量穩定性、裸片-封裝相互影響、以及最終產品可靠性等在內的所有領域進行全面檢查。測試工具的效率要提升,必須確保重要的測試結構和設計/IP模組與元件和製程開發的重要時間節點相協調,而不能單純關注開發製程中部署測試工具的絕對數量。

此一通過驗證的技術開發方法包括四個階段,如表一所示。

測試工具開發的四個階段

第一階段 |

製程開發/聯合技術定義 |

第二階段 |

分立電晶體、射頻以及單元/陣列 |

第三階段 |

電路層級/硬式 IP |

第四階段 |

類產品結構 |

第一階段開始時,製造合作夥伴將提供針對特定技術的測試結構,以執行新的製程模組,支援新設備推出,並評估新材料組合。舉例來說,40nm製程使用浸潤式微影技術和SiGe技術,而28nm製程則使用HKMG技術。

在第二階段中,用更多測試工具,以驗證如電感器和電容器(對高速收發器極為重要)以及以單元/陣列為基礎的 FPGA 元件結構等射頻元件。

在第三階段,電路級FPGA模組(如模組RAM和配置)和硬式IP結構添加到測試工具中。這種測試可評估巨集級功能和特定FPGA模組效能,包括對電路效能的寄生效應。其他結構能在產品開發早期階段就明確得知ESD效果特性。在一段時間內持續收集並檢驗工具的實踐資料,將元件型號與實際的晶片技術互相關聯,從而得到有助於提升效能、降低功耗的FPGA 解決方案。

第四階段,包含之前各階段測試工具的重要元件,並增加對代表性產品類結構的測試。舉例來說,調試專門關聯於FPGA產品佈局效果隨機問題的RAM,也對功能和效能進行描述,並能進行早期產品可靠性評估。

專利基準測試結構配合統計分析,有助於識別出突顯關鍵製程中邊緣性的薄弱點。其他結構均採用整體設計,可識別出製程和設計之間的相互影響,並對不同製程、電壓和溫度(PVT)條件下的前端(電晶體級)和後端(互聯/電介質)效能及功耗進行早期分析。這種代表性的架構亦添加到FPGA元件中,對實際FPGA元件測試工具結構提供的結果進行進一步的調試和關聯,如圖五所示。

除了電容器和電感器等基本構建元件外,測試工具中還包括多PLL振盪器及其它電路,從而強調對收發器的關鍵元件。振盪器是收發器核心,需要早期全面的描述塑造,以確保頻率穩定性,避免相位雜訊。邊緣速率和回損等更多參數特徵化也透過收發器相關結構完成。測試工具將多個結構彼此靠近放置,再結合全後端金屬層,可識別潛在的耦合效果以及相鄰振盪器間的相互影響。這種貼近性非常重要,因為FPGA中,帶全後端金屬層的多個結構與只有一個後端金屬層的單振盪器特性不同。有關資料能在技術開發早期階段就解決問題,並快速讓28nm FPGA 準備就緒。

結語

功耗是現在半導體產業的首要關注點,在FPGA產業中功耗問題尤為突出,相對於前代FPGA而言,高效能低功耗28nm製程技術與架構創新,以及設計開發工具的結合,提供一種統一的的新方法。而28nm FPGA產品將能實現系統架構師和邏輯設計人員所需要的革命性突破。該技術使設計人員能開發出更廣泛的FPGA應用,從低功耗應用(如HDTV、工業控制和車載資訊娛樂)到高頻寬以及超高階應用(如通訊設備、高效能計算、軟體無線電和視訊處理)等,無所不包。