近年來半導體與量測業者無不致力於開發工具的性能與易用性的提升,希望能協助產業界能在最短時間內滿足客戶需求外,亦能協助客戶創造更多的差異化,以期透過元件與開發工具之間的相輔相成,來因應未來市場的諸多挑戰。

有鑑於此,CTIMES特地集結業界知名的晶片與量測業者們,透過他們的介紹,加速認識各類開發工具的特色與使用方法,讓與會者對於系統開發能更加得心應手,順利達成客戶目標。

Xilinx:FPGA內建處理器 加速軟硬協同設計速度

在所謂的嵌入式設計領域,FPGA(可編程邏輯閘陣列)亦可屬於該領域的 陣營之一,但隨著ARM的開疆闢土,ARM在嵌入式領域也有相當優異的成績表現。賽靈思(Xilinx)FAE經理羅誌愷直言,在產業界裡,同時具備 ARM處理器、PLD與DSP架構的晶片業者,應只有賽靈思一家業者。

過往FPGA在產業界總有一種讓人曲高和寡的感覺,不過羅誌愷也表示,在募資網站Kickstarter已有不少案例是採用賽靈思的Zynq進行設計開發。 他以無人的飛行直升機為例,開發者就是透過OPEN CV的函式庫與Zynq加以結合而開發而成。他更談到,OPEN CV其實是C語言與C++的延伸版本,但賽靈思的作法是採用HLS(High-Level Synthesis;高階合成語言)進行移植,以達到軟硬體協同設計的目標。而賽靈思每一季都會針對OPEN CV比較關鍵的程式碼進行移植的工作,進一步的說,就是將C語言轉成RTL的流程,由賽靈思處理並加以最佳化,工程師便無需在這個流程上耗費心力。

羅誌愷進一步解析Zynq的晶片架構,傳統上,系統設計用兩顆SoC(系統單晶片)的作法,在連線的速度上相當有限,但若是加以整合後,透過晶片內部的連 結,在處理速度上更能有效提升,而Zynq本身是用雙核的Cortex-A9處理器與FPGA整合而成,中間是採用AMBA4.0的傳輸介面,速度可高達 100Gbps,再加上FPGA也有平行運算特性的乘加器來達到DSP(數位訊號處理器)的功能,所以要加速軟體處理的性能,進而作到軟硬協同設計便相當 容易。

另一方面,羅誌愷也指出,過往要作軟硬體協同設計 有著相當高的難度,工具彼此之間有著的鴻溝需要跨過,不過隨著賽靈思在各類開發工具的努力,開發工具之間的溝通已經不是問題。此外,由於Zynq本身就內 建了處理器,因此要搭載作業系統也不是問題,目前針對Linux部份,已經有Petalinux這類免費的套件可以針對Linux系統進行在Zynq上的移植,當然,工程師若要選用開放原始碼的Linux版本,Zynq也能夠支援。(姚嘉洋)

解決四大難題 Mouser成為需求最高物流服務商

目前的工程師,普遍會遭遇到的問題在於找不到料、找錯料、跟趨勢脫節,以至於發生產品上市太慢等情況,已經十分普遍。他們需要的是能夠幫助他們快速解決上面這四大難題的好伙伴,而Mouser(貿澤電子)正是為了解決工程師所遭遇到的這些問題而生。

| 圖二 : Mouser亞洲區行銷暨企業發展協理田吉平指出,Mouser希望能提供工程師一個創新應用快速實現的機會。 |

|

Mouser亞洲區行銷暨企業發展協理田吉平指出,Mouser是目前全球知名的零組件代理商,2013年的網站流量在中國區已經位居第一名,北美區則位居第二,這也可以看出Mouser對於工程師來說,已經是十分重要的代理商。

Mouser的優勢,就在於代理超過500家原廠的400萬種產品,連單一個晶片也能出貨,而便利的網站一鍵搜尋與搜尋加速器功能,以及智慧BOM表工具,更能方便工程師在最短的時間找到所要的商品。

除了產品之外,Mouser網站也與全球熱門趨勢接軌,包括技術應用文庫、電子報、研討會資訊、社交媒體等,更與許多知名產業媒體例如CTIMES等合作,讓工程師能夠快速掌握半導體產業的最新趨勢,讓他們在產品設計與找料的過程中,能將錯誤的狀況減至最低。

事實上,選擇對的電子設計工具,將能讓工程師更事半功倍。特別是由於現在產品設計的複雜度提高,使得產品上市時間受到壓縮,且設計工具的價格門檻也高,而這 些工具也需要有大型元件庫的支援。目前Mouser提供了免費的線上設計工具,不僅可加快設計週期,其所代理的400萬種展品也可訂購庫存支援,讓工程師 更無後顧之憂。

Mouser不斷進化的背後,無疑是希望能提供工程師一個創新應用快速實現的機會。藉由差異化的優勢,不僅保持Mouser繼續前進的動力,而全球化佈局與化簡為繁的運籌服務,也讓Mouser持續成為工程界需求度最高的物流服務廠商。(王岫晨)

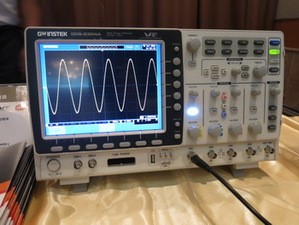

固緯:搞定頻寬、取樣率與記憶體 才是好示波器

自然界的運行,皆是以正弦波的形式移動,可能是海浪、地震、音爆、爆炸等,透過空氣傳遞的聲音或物體運動的自然頻率方式呈現。透過不同類型的感應器,可以將這些能量轉換成為電器訊號,這就是示波器的原理。透過示波器,就可以觀察、量化及研究這些訊號。

| 圖三 : 固緯GDS-2000A系列數位示波器,各種效能參數均有不錯的表現。 |

|

固緯電子實業產品行銷專案經理潘光平指出,決定示波器性能的參數種類也十分多樣,一般來說,工程師會依據包括頻寬、取樣率、記憶體深度等細節來評斷一部示波器性能的優劣。例如頻寬就決定了示波 器量測訊號的基礎能力,當訊號頻率增加時,示波器精確顯示訊號的能力將會下降。一般來說,針對一個方波而言,示波器至少要具備三到五倍的訊號頻寬才夠。

而取樣率則是顯示數位示波器每秒鐘ADC能夠做多少次取樣的能力。示波器的取樣率越快,波形在螢幕上還原的能力就越強。理想狀態下,示波器的取樣率必須大於 示波器頻寬的2.5倍。至於記憶體深度,則決定了示波器採集波形的能力。較先進的示波器,可以允許自由選擇記憶體長度,使得示波器的量測條件能夠達到最佳 化。

此外,探棒也是影響示波器性能的關鍵要素之一。探棒是介於示波器以及待測電路之間的媒介,理想的探棒 必須容易連接且方便使用、擁有絕對的訊號精確度、完全沒有雜訊耦合進入,並且不能有負載效應。嚴格說起來,探棒就是待測電路的一部份,探棒的探針會因為負 載效應而改變待測電路的響應,因此整體的電路量測結果,應該要將探棒和示波器的響應考慮進去。

目前許多儀器廠商都推出了示波器解決方案,而性能的差異,就決定於前述所提到的各種參數。目前固緯GDS-2000A系列數位示波器,提供了兩通道與四通 道, 頻寬範圍包括300MHz, 200MHz, 100MHz及70MHz等。各型號皆提供了2GSa/s交錯式即時取樣率及100GSa/s高速的等效取樣率。搭配8吋800*600 TFT LCD的螢幕顯示,垂直檔位1mV/div,與時間範圍1ns/div至100s/div,使GDS-2000A 能對複雜及微弱的信號波形進行精確的量測。

至於記憶深度的部分,GDS-2000A提供了2M的長記憶體,並且提供波形搜尋及分段記憶體的功能。記憶體分段功能可用來擷取及顯示欲觀測之波形,無關之信號則不被處理,記憶體最多分為2048組,如此可大幅增 加記憶體的使用效率。波形搜尋功能可搜尋符合觸發條件的波形並將之標示出來,再加上播放/暫停及移動Zoom視窗功能,可以快速瀏覽波形中的細節。(王岫晨)

ADI:SDR設計仍需業界通力合作

隨著無線通訊技術不斷演進,其系統設計的難度也與日俱增,這也造成了單一晶片供應商可能無法獨力提供完整的解決方案給客戶,所以就必須採取合作策略,與其他晶片業者合作,進一步供應完整的解決方案。

| 圖四 : ADI資深應用工程師簡百鍾指出,現在的客戶希望完整的解決方案。 |

|

ADI(亞德諾半導體)資深應用工程師簡百鍾表示,ADI在全球訊號轉換器的市佔率約有五成,可以說是主要的龍頭廠商。他進一步談到,從採樣率與分辨率來看,採樣率愈高的訊號轉換器,在分辨率方面的提升就會有所極限,反之,採樣率較低,分辨率就有辦法提升。換言之,不同等級的採樣率與分辨率的訊號轉換器各自在不同的應用市場有其定位。

過去的訊號轉換器只是單純地進行訊號轉換工作,但隨著技術漸趨複雜,有些半導體業者也開始嘗試加入一些混合訊號以及輔助型的數位處理功能,後來甚至還會加入濾波器甚至是基頻處理器預先要處理的工作,都可以先透過ADC(類比數位訊號轉換器)來預先處理。

而在速度方面的進展,也已經進步到PLL的SerDes等級,可達到6.25Gbps以上,但如此一此,後面配合的FPGA元件的等級勢必就不能太低。所以整體來說,ADC整體的設計也變得更加複雜,但這類ADC還是偏重相當高端的應用。

簡百鍾更指出,傳統上的作法,晶片供應商只是僅僅提供單一的元件,而現在的客戶則是希望完整的解決方案。所謂的SDR(Software Define Radio),透過軟體的控制,來控制RF的頻率或是決定無線發射的頻寬,以因應多元的無線通訊協定。要作到所謂的SDR,需要RF人員,要了解RF,還要懂數位硬體甚至是軟體程式碼的編寫,以及DSP的運作方式,ADI非常了解這方面的難度之高。

也因此,ADI透過與Xilinx之間的合作,才可以真正達到所謂的SDR設計,雙方就各自所長,ADI提供一系列的類比與混合訊號元件(也包含ADC)等,透過FMC連接器可以與不同的Xilinx旗下的FPGA開發板進行連結,以進行協同開發。

NI:LabVIEW非常適合用於設定FPGA功能

現場可程式化閘陣列(FPGA)是一種可重新設計的晶片。不同於電 腦的處理器,設定FPGA時必須重新接線晶片,以便實作自己的功能,而非執行軟體應用程式。Xilinx的共同創辦人Ross Freeman在1985年發明了FPGA,從簡單的膠合邏輯(Glue logic)晶片,演變為可取代客制的特定應用積體電路(ASIC)與處理器,適用於訊號處理與控制應用。目前NI也與Xilinx建立起合夥關係,針對 各種硬體平台提供最先進的FPGA技術。

| 圖五 : 星協科技專案經理吳志二認為,LabVIEW FPGA可讓各種測試設備機台更快上市。 |

|

最籠統來說,FPGAs 即為可再程式化的晶片。透過預先建立的邏輯區塊與可程式化路由資源,不需更改麵包板或焊錫部分,即可設定這些晶片以建置客制硬體功能。使用者可於軟體中開 發數位運算系統 (Computing task) 並將之編譯為組態檔案或位元流 (Bitstream),可包含元件接線的相關資訊。

此外,FPGA 完全為可重設性質,當使用者重新編譯不同的電路設定時,可立刻擁有不同的特性。在過去,工程師必須深入了解數位硬體設計,才能夠使用FPGA技術。然而,高階設計工具的新技術可針對圖形化程式區或C程式碼,轉換為數位硬體電路,即變更了 FPGA 程式設計的規則。

FPGA 整合了 ASIC 與處理器架構系統的最佳部分,使 FPGA 晶片可應用於所有產業。FPGA 具有硬體時脈的速度與可靠性,且其僅需少量即可進行作業;可降低客制化 ASIC 設計的費用。可重新程式設計的晶片,具有與軟體相同的彈性,卻不受限於處理核心的數量。與處理器不同的是,FPGA 為實際的平行架構,因此不同的處理作業並不需要佔用相同資源。每個獨立的處理作業均將指派至專屬的晶片區塊,不需影響其他邏輯區塊即可自動產生功能。因 此,當新增其他處理作業時,應用某部分的效能亦不會受到影響。

FPGA技術的5大優點包括效能、上市時 間、成本、可靠性與長期維護。在過去,工程師必須深入了解數位硬體設計,才有辦法運用 FPGA 技術。但隨著 NI LabVIEW 軟體等高階系統設計工具的興起,FPGA 程式設計的規則也有所變化,所提供的創新技術可把圖形化程式圖轉換成數位硬體電路。 所有的 NI FPGA 硬體產品皆搭載可重設 I/O (RIO) 架構,其中配備強大的浮點處理器、可重設 FPGA 與模組化 I/O。NI RIO硬體搭配LabVIEW系統設計軟體,即可在設計進階的控制/監測/測試應用時,簡化開發作業,同時縮短上市時間。

NI LabVIEW FPGA Module可擴充LabVIEW圖形化開發平台,並用於NI可重設I/O(RIO)硬體的FPGA。LabVIEW 非常適合用來設定 FPGA 功能,因為能清楚呈現平行機制與資料流;無論使用者是否熟悉傳統的 FPGA 設計,都可以有效運用可重設硬體的強大效能。

選用 LabVIEW FPGA Module的主要理由有三大項:

於FPGA硬體上使用強大的圖形化程式設計

一般來說,FPGA 必須透過 VHDL 或 Verilog 進行設計。工程師可能不熟悉這些複雜的程式語言,或需要更高設計效率的工具,以便大幅簡化 FPGA 程式碼的生產過程。LabVIEW FPGA 比其他類似工具更好入手,也更便於執行。

直接於硬體中建置LabVIEW程式碼

FPGA 本身即具備硬體電路,沒有任何的作業系統或執行緒。透過 LabVIEW 設計 FPGA 時,往往需要更高的處理速度、精確度、穩定性與平行機制,才能建構絕佳的 FPGA 系統。

運用初階功能完成高階設計

LabVIEW為FPGA 適用的高生產力程式語言,除了可精簡複雜的細節以加快設計速度之外,必要時還可設計所有的時脈週期。

星協科技(WPC System)專案經理吳志二認為,目前採用了LabVIEW FPGA,讓該公司在進行各種測試設備機台的時候,能更縮短時間,加速產品上市。(王岫晨)