不可或缺的PLD

PLD可編程邏輯元件內含一系列可編程功能元件,利用這些元件的配置和互連可實現基板上特定的硬體管理功能。一般而言,軟體設計工具可將某個邏輯功能如基板硬體管理,轉換為特定PLD的配置位元流(bit stream),可用於互連和配置可編程功能元件。配置位元流位於可編程邏輯元件內的配置快閃記憶體中。

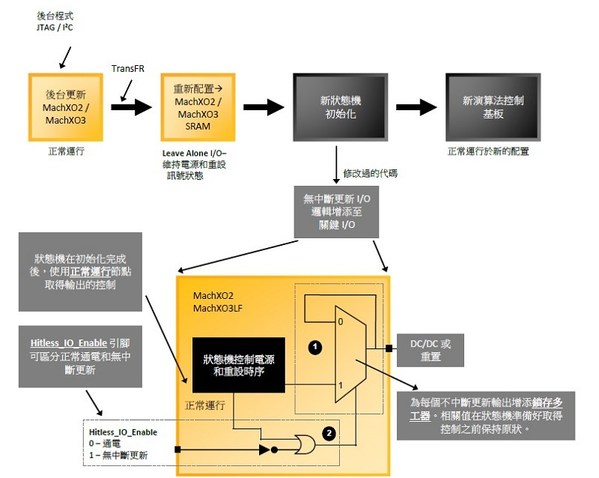

當基板通電後,配置快閃記憶體中的內容將自動傳輸到晶片內的配置SRAM,使配置可編程功能單元執行所需的硬體管理任務。PLD更新硬體管理功能時,可透過不同的位元流從後台隨時載入到配置快閃記憶體,無需中斷可編程邏輯元件執行中的硬體管理功能。將新儲存至快閃記憶體的配置傳到晶片內的SRAM會造成電源重啟,中斷系統的正常運行(如圖1)。

在配置過程中保持穩定的輸出

高常用性系統無法接受因電源重啟導致的作業中斷。由於可編程邏輯元件的I/O可使基板上主要的ASIC和CPU實現DC-DC轉換器和控制重設訊號,但在重組時可編程邏輯元件的輸出需保持不變。保持PLD在重組時的輸出穩定,為其應用設計帶來多項挑戰。

萊迪思MachXO2或MachXO3 PLD系列支援多項功能實現系統更新零停機(如圖2)。首先,PLD進行「後台更新」透過JTAG、SPI或I2C載入新的配置資料至其配置快閃記憶體,待載入完畢,「TransFR (Transparent Field Reconfiguration, 透明現場重組)」 指令將新的PLD配置從快閃記憶體傳輸到PLD的配置SRAM,執行「TransFR」指令的同時啟動「保持當前狀態(Leave Alone)」功能,確保所有的I/O值在傳輸過程中保持不變,最後,在「邏輯初始化」步驟,狀態機將開始重新啟動電源管理並重設分配。導致電源中斷,強迫基板進行電源重啟的過程。

| 圖2 : 採用MachXO2/ MachXO3無中斷更新I/O 的PLD重組步驟 |

|

使用無中斷更新I/O解決問題

為了支援系統更新零停機,PLD元件必須能使新影像所創建的狀態機在初始化階段時,能確保控制電源以及其他邏輯訊號的輸出保持不變。新演算法經過初始化之後,即能管控電源和其他邏輯訊號。

為了使得關鍵I/O在初始化過程中保持原狀,使用者設計中需增添「無中斷更新I/O」,如圖3所示,這需要為每項關鍵輸出增添一個鎖存多工器(latch-mux),在狀態機初始化的過程中保持輸出的最終已知狀態,並在初始化過程完成後將輸出控制交還至狀態機。該電路能運用「Hitless_IO_Enable」輸入區分正常(通電)啟動和重組狀態,可避免在正常的通電過程中發生關鍵輸出I/O值被鎖的情況發生。

深入探討

PLD提供設計便利性和絕佳效能,可管理基板上DC-DC轉換器、監測和控制關鍵訊號、整合串行通訊並執行其他內務管理功能,為高常用性系統理想的硬體管理元件。

圖3說明新配置載入至MachXO2/ MachXO3元件配置SRAM時,無中斷更新I/O在狀態機初始化過程中所發揮的作用。

| 圖3 : 無中斷更新I/O在初始化期間使關鍵I/O保持最終已知狀態 |

|

為每項輸出增添一個鎖存多工器,只要多工器的控制輸入為「0」,輸出就能保持現值不變。這意味著無論狀態機的輸出狀態如何,DC-DC轉換器可保持「on」(如果先前處於「on」的狀態)。當控制訊號為邏輯值「1」時,DC-DC轉換器的狀態則由狀態機控制。狀態機透過「正常運行」節點控制多工器輸出。晶片最新添加的「Hitless_IO_Enable」輸入可區分正常的「通電」配置(狀態機初始化過程中DC-DC轉換器輸出受到控制)和無中斷重組流程 (狀態機初始化過程中DC-DC轉換器保持不變)。

假設控制無中斷更新流程的「Hitless_IO_Enable」訊號設為「1」。

在初始化前,狀態機將「正常運行」訊號重設為「0」。鎖存多工器將忽略來自狀態機的輸出,並且DC-DC轉換器的「Enable」訊號保持不變。

當PLD的邏輯準備好恢復正常運行時,將「正常運行」訊號設為邏輯值「1」(高電頻),允許其取得DC-DC轉換器的控制。此時基板的DC-DC轉換器和重啟將由復原的電源和重設控制狀態機控制。

實際案例

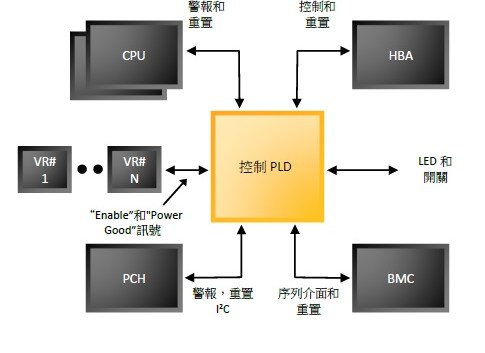

圖4說明PLD在供電、監控和管理CPU叢集 (cluster) 以及平台控制中心 (Platform Controller Hub, PCH)、基板管理控制器 (Baseboard Management Controller, BMC) 和主機匯流排轉換器 (Host Bus Adapter, HBA) 等基板級子系統的使用情景。

在此例中,PLD主要負責基板負載點電壓調節器(Voltage Regulator, VR) 的上電和斷電時序,並在電源重啟時將重設和控制訊號保持最佳的狀態。在正常運行時,PLD監控子系統的溫度、電壓、記憶體和I/O故障等警報參數或狀態變化,同時將控制訊號穩定保持在合適的狀態。

| 圖4 : 將機架式服器的控制/內務處理功能整合至PLD |

|

BMC在後台更新伺服器的控制PLD並啟動「TransFR」指令以便用更新的配置運行PLD。若沒有無中斷更新I/O的情況下,控制和重設訊號或是 VR訊號將不能在初始化過程中保持不變。例如,若CPU或其外設上的重設訊號在重組過程中發生變化,無論當下CPU執行何種功能都將進行重新初始化並開始重啟流程。

同樣的,如果「Power Enable」訊號發生變化,VR或負載點的電源供應將中斷,導致由該VR供電的元件進入未知狀態,造成基板運行中止、遺失或擾亂資料,甚至對基板的電子元件造成物理損害。

為關鍵訊號增添無中斷更新I/O機制可使PLD在重組的過程中暫停外部感測和控制訊號。因此,伺服器的關鍵功能在PLD的常態性維護和升級過程中不受中斷。此功能也有益於產品開發,能夠縮短除錯時間或是在安裝機架時建構專用產品的變數。

總結

PLD為靈活、高成本效益的解決方案,可控制DC轉換器、橋接I/O通道以及執行複雜電子系統中的其他基板級硬體管理功能。元件支援現場升級,可為製造商提供運行中變更配置所需的靈活性,實現設計錯誤更正或是為產品添加新功能。

隨著無中斷更新I/O架構的面世,PLD現可以無差錯、有保證的方式進行重組。其設計中的閘道數量的增加通常少於1%,並且無需外部元件即可執行。無需電源重啟即可實現穩定可靠的配置變更,無中斷更新邏輯使CPLD成為網路、資料中心儲存設備以及其他任務導向應用中硬體管理解決方案的理想選擇。

(本文作者為萊迪思半導體資深產品行銷經理)