多年来,软体于嵌入系统设计中扮演越来越重要的角色。而从定义及描述基础硬体平台的程序,以至于使用者介面及应用层级中,程式码已经成为工程学加值及任何产品进行差异化的要项。

这个趋势形成了硬体及软体 (经常是硬体设计者及软体程式设计者之间健康的紧张关系)角色间的复杂交互作用。昔日每块晶片都是全客制元件以建置所有功能于硬体中,而于制造(fab-binding)时便拥有其功能组合的日子已不复见了。另一方面,具备以高阶语言撰写之传统程式来定义行为的元件之「处理器」架构,同样也以可编程核心加入SoC元件中,周边则是具备特定功能的硬体。

软体较容易修改、更新及维护

跨越「可编程」及「硬线」之鸿沟的方法,为可配置式解决方案(如FPGA)。其部署一套通用硬体资源而可进行功能化配置,因此本质上并未改变。硬体描述语言可用来描述所需的行为, 而功能则是于通电(field-binding)时设定。无论用什么方法,目前几乎所有硬体都拥有某些软体元件。设计者们均认同软体较容易修改、更新及维护,这是关键要求,尤其是于具成本压力及拥挤的市场环境中。

这种双重特性致使在设计流程中越来越难达到一贯性及整合性。尽管如SystemC之开发便是企图跨过硬体及软体主导的领域, 但每一类型的设计仍然大量保留了自身独特的设计工具及方法学。对于此问题的解决方法,是展开对软体化的晶片(SDS)矽晶架构方法之进程,其能提供大量软体驱动设计流程,并使用相似的软体开发范例。

SDS的实体建置,系根据多核心阵列处理器架构。概念性而言,此组成可视为建置大量独立操作连续程序。此阵列透过讯息传递沟通,可加以配置来高效率地执行相关功能,包括作为较初始程序的平行结构,或连续操作的连续组成。

SDS软体架构

SDS 架构需要用来做为程序排程、同步化、通讯及输入/输出任务的硬体资源。虽然各个核心的指令集必须为相同的协同处理、通讯及I/O功能提供便利性,此以传讯为基础的通讯仍保留了各个初始程序的独立性,并使其能建立高效率、可扩展至百个程序的多核心晶片。其协同成本可有效率的降低,以支援负载、储存、分立及算术运作。

SDS方法的优势之一,是其支持各种编程技术,范围从静态配置网路至动态再配置等。协同程式可直接编写入处理器指令集,其不须OS内核,并且于处理器建置时无微码。

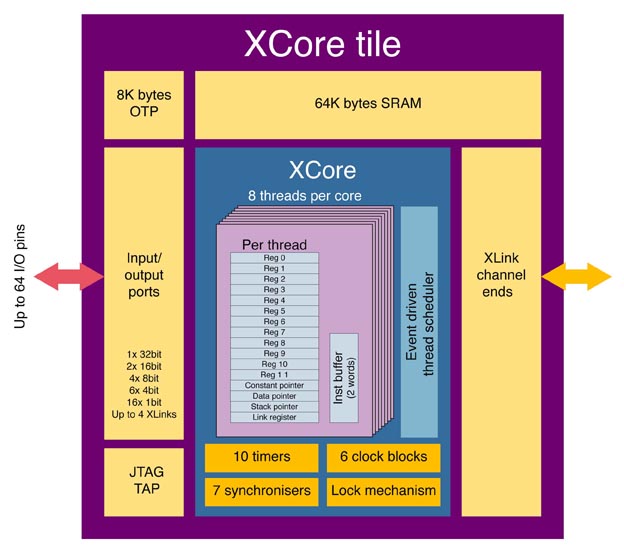

每个XMOS处理单元(或tile)包括处理器、本地指令及数据记忆体、处理实体介接之I/O架构,及一个处理执行绪交互及核心交互通讯的基础设施,如图一。造就了透过动态讯息定线网路通讯的处理器阵列:将此方法与常用于FPGA的方法比较是值得的,其包括藉由静态配置互连而通讯的look-up表列。

| 《图一 XMOS XCore tile以四个主要的元素来建置软件化的硅晶。XCore 32位8路多线程处理器,其为一个紧密整合的I/O埠架构;XLink线程交互通讯协议及基础设施,以及64KB单一周期本地内存。》 - BigPic:623x552 |

|

I/O处理功能在SDS结构中尤为重要。其允许整个系统被转译成执行于vanilla矽晶的软体图像,而这就是用于SDS 的处理单元与传统嵌入式处理器不同之处。欲建置I/O介面,此处理器必须对晶片外部针脚所产生的即时事件明确回应,无论所执行的是何种软体。

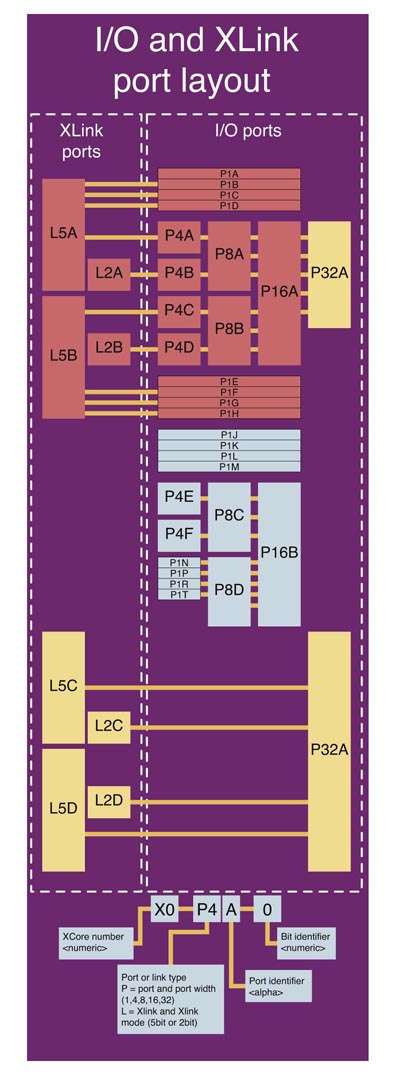

相对的,I/O应拥有足够的智能以将针脚及处理器间的延迟降至最低,如图二。于软体中建置多重介面同样会提高平行程式设计的挑战,此软体必须能快速切换内容,以使多重任务能有效率地同步执行。

EDA工具及硬体描述语言(HDL)须兼顾

虽然SDS方法适用于嵌入式软体设计流程, 需留意的是, 这不代表须放弃已经建立在EDA 工具及硬体描述语言(HDL)的可观知识与技术。特别是标准编程语言,如C语言,并不以其既有的平行性,在积体电路内容中以一有意义的方式处理事件或计时。

另一方面,无容置疑地,理想中硬体设计应该更像软体编辑,这有许多理由可以解释。首先, 针对具备数百个op-code的目标处理器,编写一个具备数百个可变数的C程式是一个本来就完全可预期的过程,因此其只具备有限的「正确」答案。相反的,即使是一个小型50k系统闸极FPGA,都拥有50万(大部份为独立)个配置位元,所提供的可能组合范围相当大,完全客制化的ASIC甚至有更多选择。

| 《图二 建置XCore的主要元素,是增加智能至I/O。为达到建置硬件接口所需的I/O延迟及带宽, 此XCore上的埠紧密的耦合至核心,并支持广泛的特性以降低软件负荷。》 |

|

硬体设计者的这些窘境,使其需要在设计意向的描述中加入对目标元件的了解,以此可限制工具的使用,使其只考虑已知的最佳选择,而避免已知的不良建置也同样重要。软体编辑是比HDL方法更短的程序。以HDL工作需要在直通(first-pass)目标矽晶定义前便完成综合、配适、布局与绕线 (P&R)。每一个步骤跟整个软体编辑程序本身一样复杂,而最后会产生许多等效结果。

如同前述提示,当相关设计需增加或需在最后一秒进行更改时,软体化的流程一定有其优势。在HDL方法中,既使模组从综合至netlist之角度而言已充分地被隔绝,设计上的变更仍可在P&R过程中引发妥协,而重建时间(及增加中的功耗)方面,广为人知的挑战只有在设计变动后才会结束。

相反的,可编程元件以处理器引擎及程式计数器的暂时时间调扩效应,取代了P&R流程。于此情况下,自足式程式模组对于设计的其他部分冲击有限,因此不需要任何本质上的妥协。

结论

自从硬体工程师接受逻辑综合,并了解设计工具可被用来将高阶定义的功能转译成低阶制造细节,至今已超过20年。今日,嵌入式设计者正准备采取相似的信念。 SDS 架构使他们能更趋近软体工程的工作模式,将设计意向以更直接、编译器型式转译成元件指令。

但仅采用软体化的流程是不够的。关键将是部署一个包含正确矽晶架构、谨慎设计指令集与弹性工具组之组合。而唯有能提供此三项优势之供应商,才能在硬体及软体的统合中获致成功

<作者为XMOS Semiconductor行销执行副总裁>