Xilinx FPGA被業界廣泛地應用在無線通訊基地台設計,包括基頻協同處理與其它先進的基頻功能。除了頻道卡應用外,Xilinx FPGA也提供具成本效益的多種無線通訊界面卡功能,像是數位上行轉換(Digital-Up-Conversion, DUC)以及數位下行轉換(Digital-Down-Conversion, DDC),其中包括各種先進技術,如波峰因數消減(CFR)與數位預失真(Digital pre-distortion, DPD)。除了針對WCDMA與WiMAX的無線通訊界面卡解決方案外,Xilinx也推出TD-SCDMA數位前端解決方案,支援多重載波與多重天線等組態。

波峰因數與RFPA效率

RFPA的功耗效率是設計無限通訊基地台最重要的要素,因為它對OPEX與CAPEX有顯著的影響。高效率的RFPA解決方案帶來更低的CAPEX,因為系統可使用較小的功率放大器,就能達成相同的輸出功率,或較少的冷卻設備需求。另一方面,由於功耗較少,OPEX也會降低。

針對效率較高的RFPA需求,促使基地台架構從被動式單載波功率放大器(SCPA)輸出轉移至數位式的載波,運用多重載波功率放大器(MCPA)產生的中頻來傳送訊號。後者亦讓系統採用CFR技術的應用與數位線性化技術,如DPD。

然而,載波訊號的線性組合,衍生出高波峰對平均功率比(PAPR)。這不僅出現在3G CDMA載波,多重載波EDGE與GSM訊號也是如此。甚至單載波CDMA或OFDM訊號也出現極高的波峰因數(CF),這是來自於CDMA與OFDM載波時產生的許多獨立波形的線性組合。

用來量測PAPR的波峰因數可定義如下,由公式(一)推算

《公式一》  |

其中的x 是上行轉換窄波訊號的實際值

在高波峰因數環境中,常用的Class AB RFPA必須在特定的輸出回退(Output Back Off Level)時運作,如此方能避免高峰值訊號導致RFPA轉變成非線性。首先探討波峰因數與RFPA效率之間的關係。

RFPA效率的定義是在特定運作點時,DC電源的平均輸出功率。如公式(二)所示

《公式二》  |

這意謂著若要達到較高的效率,RFPA輸出應接近飽和點(此時非線性效應不會產生影響)。然而,在實際的運作中,輸出功率偏低,不僅和輸入訊號的波峰因數及RFPA有關,其它較微弱的RFPA非線性關係也有影響。

圖一顯示,輸入功率回退(Input Power Back Off)與輸出功率回退(Output Power Back Off, OPBO)之間的關聯性1。為達到理想的OPBO水準,必須提高IPBO。由於運作點維持不變,公式中的分母固定,但隨之OPBO提高而分子減少,進而導致效率降低。

《圖一 RFPA的功耗效率曲線》  |

圖二顯示針對不同等級的放大器在轉移電導(trans-conductance)時產生極高的非線性時,所顯現的典型RFPA效率,其OPBO則以dB為單位。當回退越高,Class AB RFPA 在12dB的OPBO時,效率從70%下滑到約10%。

《圖二 RFPA 效率效能》  |

面對高波峰因數訊號因而增加OPBO,進而衍生效率降低的問題時,有兩種解決方法。其中之一是使用高效率的波峰因數消減機制來降低多重載波輸出訊號的PAPR,或(與)使用數位預失真(DPD)技術來拉大RFPA線性運作的範圍。藉由降低輸出至RFPA訊號的PAPR,可降低IPBO,同時OPBO也進而壓低,如此就能增進效率。

在CFR方面,一般效率約在16%左右,若沒有使用CRF則約為8%。在以下的章節,我們將介紹各種常見技巧,並深入探討在各種TD-SCDMA多重載波應用中,Xilinx的脈衝消減CFR (Pulse Cancellation CFR, PC-CFR)機制在效能與資源使用效率的表現。

CFR技術

業界至今推出許多CFR機制,運用編碼選擇、 I & Q或基頻極性剪裁、波峰修整 (PW-CFR)、雜訊調整(NS-CFR)、以及脈衝注入(PI-CFR)。Xilinx推出一種名為波峰消減(PC-CFR)的技術,它具備減少運算的負荷以及其它方面的優點,使得此技術在使用更少資源的同時,效能也更優異。

在詳細探討PC-CFR之前,先概略上述3種常見的技術。

波峰修整CFR (PW-CFR)

PW-CFR是傳統剪裁技術的延伸,利用時域調整的方法來剪裁訊號以降低PAPR的功效。

傳統剪裁的公式如下所示

《公式三》  |

其中c(n) 定義來自於以下公式,當中的A是波峰剪裁訊號的最大允許值。其想法是用函式b(n)來取代c(n),利用適合的窗口範圍來限制波峰剪裁訊號的展頻。

《公式四》  |

PW-CFR 模塊圖表,如圖三所示

《圖三 PW-CFR 模塊圖表》  |

PW-CFR處理訊號的ACLR 與EVM 效能, y(n) 值取決於窗口種類以及窗口長度。窗口的長度可在ACLR與EVM效能之間做取捨,較長的窗口獲得較佳的ALCR數據,但須捨棄EVM的效能。

雜訊調整CFR (NS-CFR)

這個機制最先運用在Xilinx針對WCDMA數位前端元件以及後續推出的WiMAX參考解決方案。NS-CFR藉由將超過特定消減門檻的樣本全數剪裁,以達到減少波峰因數的效果。

《圖四 NS-CFR 機制概念圖》  |

圖四顯示NS-CFR (亦稱為錯誤分派CFR)系統的模塊圖表。傳統的極性剪裁技術用來裁去超過特定門檻的波峰訊號。經過剪裁的訊號必需再處理雜訊調整,確保因剪裁動作而落在訊號頻帶內的雜訊。

雜訊調整的剪裁訊號將從原始訊號傳送到頻道,以降低PAPR。上述機制中,在處理過程產生的波峰,可於後續的階段再加以利用。NS-CFR 機制提供超越PW-CFR 的效能。

脈衝注入CFR(PI-CFR)

圖五表示簡化版的PI-CFR機制。這項技術通常運用於數位剪裁程序的最終階段。

《圖五 PI-CFR 機制》  |

基本來說,PI-CFR機制會在低於採樣率的比例下偵測輸出端的高PAPR訊號,鎖定超過剪裁門檻的波峰,對應到相同振幅的「完整」訊號,但其位相是相反的。產生的訊號用來抵消偵測到的波峰訊號,如圖五模塊圖表所示。

封包的PI-CFR系統含有一系列偵測與消減(PDC)階段,以及數量有限的脈衝產生器。因多個PDC的同時運作,引發在階段過程中波峰的重新產生。

波峰消減CFR (PC-CFR)

PC-CFR 技術提供類似NS-CFR的波峰因數降低效果。

但有別於稍早介紹的NS-CFR,在PC-CFR機制後,產生的頻譜型訊號是參考波峰採樣,在經過適當的延遲處理後,用採樣訊號來剪裁原始波峰訊號中超過剪裁門檻的部份。在NS-CFR中,所有剪裁過的雜訊採樣都經過濾波處理,且使用於幅度剪裁對應的原始延遲波峰訊號。

簡化方法的結果,僅使用波型樣本來剪裁,會產生較少的失真,也會降低運算的負荷。

在各個PC-CFR 階段,可能含有4個 CPGs (消減脈衝產生器),波峰調整涉及複雜的重整處理。PC-CFR機制的另一個優點,是它帶來的彈性,相同系統能支援多個無線傳輸界面標準,能適當地變更產生脈衝的濾波器。

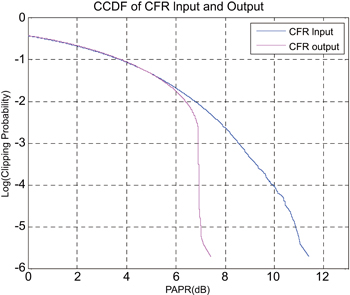

圖六顯示CFR輸入的CCDF圖,以及在7% EVM運作點的CFR輸出,加上超過15MHz頻寬的6個非鄰近TD-SCDMA載波,在1E-4的增益是3dB。模擬作業在76.8 MSPS的輸出採樣率下完成2。在圖七中,描繪類似組態下,頻譜輻射掩模(SEM)的PSD效能。

《圖六 CCDF圖: 6個超過15MHz非鄰近TD-SCDMA 載波》  |

《圖七 CFR 輸入的PSD以及二次交迭運算PC-CFR的輸出》  |

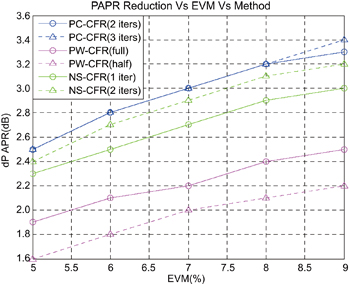

圖八顯示PC-CFR、NS-CFR、以及PW-CFR的效能比較。PC-CFR 在不同EVM值下提供最好的效能,而PC-CFR在二次交迭運算後增加的效能幅度有限。

《圖八 各種TD-SCDMA @ 76.8 MSPS機制的效能比較》  |

表一列出二次交迭運算PC-CFR所需使用的FPGA資源

表二列出一個10MHz、6載波、3天線(6C3A)TD-SCDMA 76.8 msps數位前端元件的資源使用狀況,每個天線需要一個二次交迭運算PC-CFR模組。這種組態可應用到基地台以及遠端無線電。

根據表二的資料,使用兩個 V4SX35 FPGA讓研發業者能建構一個6C6A數位前端解決方案,內含CFR,能提供較高效率的RFPA。這點相當重要,尤其是在需要傳導冷卻的RRU環境。

誠如本文所討論,PC-CFR很顯然的勝出其它同類型產品,因為它提供超越其他機制的效能,且使用較少的FPGA資源。再加上許多TD-SCDMA DFE參考設計方案,讓基礎建設設備研發業者能縮短產品上市時程,並得到較高的成功機率。

<附註: [1] OPBO被定義為最大輸出飽和功率與實際輸出功率比

[2] PC-CFR參考設計方案亦可適用於61.44MSPS DFE解決方案>