文/愛美科;編譯/丘燕

源/汲極接觸電阻:先進矽CMOS的技術瓶頸

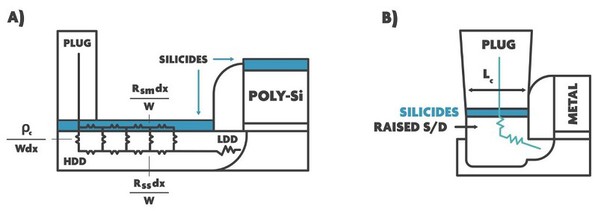

源極/汲極是電晶體的接觸電極,用來引入與移除載子(carriers)於電晶體的傳導通道。傳統的CMOS技術,利用金屬導體(MS)接觸特性,在金屬側具有過渡金屬矽化物(例如鎳矽化物),得以形成源極/汲極的接觸電子。另一種普遍方式,是利用自對準矽化物製程,稱為SALICIDE,讓矽化物覆蓋在整個源/汲極表面。

| 圖一 : 隨著新型鈦矽化技術的發展,來自愛美科(imec)的博士生Hao Yu,介紹了改進源/汲極接觸方案,這將能解決先進CMOS技術接觸電阻帶來的挑戰。 |

|

但隨著電晶體尺寸的縮小,與接觸面積成反比的源極/汲極處的接觸電阻,則會相應地增加。

Hao Yu說:「接觸電子上升的問題,從14nm後就漸趨嚴重。使得源極/汲極接觸電阻成為主要的寄生電阻,大量削弱先進矽CMOS的效能,這促使我們著手研發改善源極/汲極處接觸電阻方案。」

接觸電阻像是「自然」界面電阻,當兩種不同材料接觸時就會產生。「一般而言,有兩個法則可用來改善金屬半導體接觸時產生的電阻。」Hao Yu說。「一個是是增加半導體側的摻雜程度,另一個是優化金屬和半導體之間的介面品質。」

超低接觸電阻率:矽化物候選人的新規範

進一步研究顯示,金屬半導體接觸電組率(ρc),被視為源極/汲極接觸電阻在小面積接觸面的主要成因。因此,未來的製程技術便需要具有超低接觸電阻率(即低於2×10-9Ωcm2)的源極/漏極接觸電阻,用來抑制寄生電阻,並確保電晶體的高性能。

Yu解釋說:「由於金屬與半導體間能源帶的不連續,促使接觸電阻率上升。所以具有超低接觸電阻率的觸點,可允許高通量載子以高速率通過金屬/半導體界面傳輸。」

雖然傳統的鎳矽化物提供低接觸電阻率,但是鎳在矽(鍺)中的快速擴散效果,限制了其在先進奈米級電晶體的應用。Yu說:「因此半導體公司希望愛美科研發新的接觸方案和新的矽化物材料,達到具備超低的接觸電阻率,同時兼容於CMOS製程。」

| 圖二 : 橫截面示意圖(a)利用SALICIDE技術的傳統電晶體、(b)現代電晶體。 (註:矽化物在現代電晶體的橫向電流分佈中不起作用。) |

|

適當的測試載具

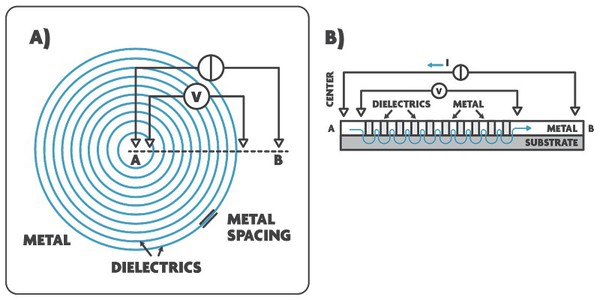

現在市面上,缺少的是一種能夠精確測量,和評估接觸電阻率低至10-9Ωcm2結構的測試工具。

Yu說:「在我的博士研究框架中,透過愛美科接觸模組團隊的協助,利用多環形傳輸線模型(MR-CTLM),我設計了一個獨特的平面測試結構。新的測試載具,結構簡單(具有最小誤差)、高採樣能力、高重製性,可精確展現超低接觸電阻率特徵。

| 圖三 : MR-CTLM測試載具結構的示意圖:(a)俯視圖和(b)橫截面圖。 |

|

已同時有幾家主要晶圓代工廠同意並實施了MR-CTLM測試結構,該結構也已被數所大學所複製。MR-CTLM能夠準確揭露超低接觸電阻率,相當接近產業目標所需。MR-CTLM結構製造簡單,也有效促進和加速於評估各種產業相關的源極/汲極接觸方案。

金屬絕緣體半導體觸點是否會導致低接觸電阻率?

幾年前,金屬絕緣體半導體(MIS)的源極/汲極觸點開始引起注意。Yu說:「結果顯示,在金屬和半導體之間插入一個超薄絕緣體,可以幫助實現非常低的蕭基能位障高(Schottky barrier height),應該可達到低接觸電阻率。我博士研究中的一部分,即看好這接觸方案,並評估了接觸電阻率和CMOS(適用於7nm以下)的兼容性。我篩選了幾種絕緣材料,包括鈦二氧化物,但發現MIS源/汲接觸方法的兩項主要缺點,停止了應用MIS觸點於先進的CMOS技術的想法,而這些問題與絕緣體無關。」

首先是涉及MIS觸點的熱穩定性,特別是在n型半導體上;第二,在與CMOS電晶體源極/汲極相關的高摻雜半導體上,MIS觸點的蕭特基位障高降低了MIS觸點的優點,無法補償掉穿隧能障引起的載子阻塞。

新型鈦矽化技術

在他的博士論文的第二部分,Hao Yu轉為探究金屬半導體源/汲接觸方案,金屬側有鈦矽化物,半導體側有高摻雜矽(n +)和矽鍺(p +)。

經過內部討論並與愛美科的CMOS項目合作夥伴密切協商後,他們開發了三種新的鈦矽化技術,改進了金屬半導體界面。這三種技術可達到大約10-9Ωcm2的超低接觸電阻率,如MR-CTLM測試載體所展現的結果。

這些技術之間的主要區別,在於與最先進的CMOS可製造性的兼容性。Yu說:「我們從第一種技術中得出的結論,讓我探究了第二種技術,可擁有更好的CMOS兼容性。繼續從第二種技術的結果,我們得到的第三種技術,而它與CMOS製造最相容。我們的合作夥伴也對這三種技術進行了評估。」

第一種技術中,稱為接觸前非晶化注入,是一種在鈦沉積和接觸形成之前,進行鍺離子注入的步驟。該步驟被認為可改善鈦矽化物的成核和結晶度。然而,使用不是完全結晶的矽化物,但具有嵌入式小鈦矽化物微晶的無定形狀態下,可達到最低的接觸電阻率值。

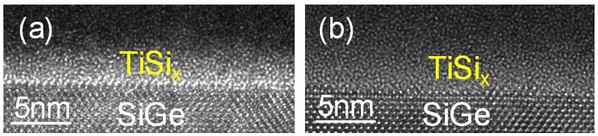

Yu說:「低ρc鈦矽化物的特殊階段,促使我開發第二種技術,也就是基於矽化鈦(TiSi)共沉積作用,形成鈦矽化物。利用這項技術,可以增強鈦矽化物微晶的形成。這項技術還能提高源極/汲極觸點的品質、可靠性和可重複性。」

| 圖四 : 在SiGe上的超薄共沉積矽化鈦(TiSi)的橫截面TEM((a)在450℃下N 2的1分鐘之前和(b)之後)。 |

|

最後,第三種技術被開發用來解決矽化鈦沉積技術與CMOS製程兼容性的限制。

Yu補充說:「透過共形化學氣相沉積(CVD)/原子層沉積(ALD),矽化鈦將成為產業的最佳接觸解決方案,但該技術仍在開發中。在現階段,我們與工業供應商一起探索了使用保形沉積技術,如ALD沉積鈦。」

「這項技術使我們能夠創造鈦基底的ALD,擁有超低ρc(2x10-9Ωcm2)的源極/汲極觸點。」

在不遠的將來,Hao Yu將利用在博士研究工作中所獲得的知識,在愛美科針對5G手機的高速類比/射頻程序框架內,開發基於三五族為基礎元件的接觸方案,如砷化鎵銦(InGaAs)或氮化鎵(GaN)。

(本文由愛美科授權刊登)