宜特宣布,近日引进真空压力烤箱,可依据不同胶材黏度调整真空及压力叁数,做到0 % Void,彻底将Underfill制程品质做到最好,避免因Void原因,影响可靠度测试结果。

|

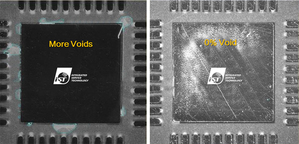

| 图为一般烤箱,有较多的Voids残留;右图为使用真空压力烤箱,没有任何void残留 |

宜特指出,现阶段,晶片采取细小间距的球闸阵列封装(Ball grid array,简称BGA)、晶片尺寸封装(Chip scale package,简称CSP)封装形式的比例越来越高,因此锡球间距(Ball pitch)小於0.25公??(mm)以下的焊点可靠度受到关注。主要来自於,热应力、机械应力(弯曲、扭曲)或冲击应力作用下,细小间距的焊点可能出现断裂失效问题。

因此,在表面黏着制程(Surface-mount technology,简称SMT)後,进行底部填充胶(Underfill)制程,能有效阻止焊点本身(即结构内的最薄弱点)因为应力发生应力失效,将有效增加晶片的可靠度。

宜特进一步说明,Underfill制程多被运用在手持装置,如手机或平板的电路板设计,来自於这些装置必须通过严苛的冲击试验(Mechanical shock test)与震动试验(Vibration test),若未进行Underfill制程,手持式装置中晶片的焊点,将无法承受如此严苛测试条件。

然而,在进行Underfill制程操作中,容易受到各种因素影响,或多或少会产生气泡(Void)。这些因素包括胶管本身含有气泡、点胶温度及路径、温度固化的叁数,晶片设计锡球矩阵、锡膏助焊剂成份..等,皆可能导致Underfill无法完全包覆晶片底部的锡球,大幅降低焊点保护效果。

在宜特可靠度验证实验室中,就发现Flux的残留将阻碍Underfill流动路径,导致填充胶无法填满晶片底部,这样的情况下执行Underfill制程也会造成许多的气泡。

宜特可靠度验证实验室建议,先采取清除助焊剂(Flux clean)湿式制程,将阻碍流动的异物排除。清除後,务必将PCBA烤乾後,才可接着执行Underfill制程。

此外,随着先进制程将晶片极小化下,锡球间距也随之缩小,基板(Substrate)与裸晶(Die)的间隙缩小至10-30微米(um);间隙越小,流动的速度就缓慢,进而产生空隙,Underfill就更难渗透,且无法平均包覆每一个焊点,因此产生气泡。

宜特表示,若晶片底部有气泡,样品在有温湿度及通电的环境下,沿着Underfill Void处将会生成Dendrite,容易导致锡球间短路,造成可靠度测试的电阻值异常。换句话说,若无气泡,将能延长晶片寿命。因此,宜特近日引进真空压力烤箱,将可??协助客户在进行underfill制程时,消除void(周围气泡),正确获得可靠度测试数值。