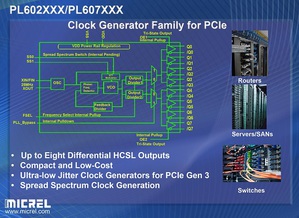

麥瑞半導體公司(Micrel Inc.)今天推出PL6020xxx和PL6070xxx時鐘發生器及SY7557xL時鐘分配產品。新產品可為PCI-Express(PCIe)基準時鐘信號提供極低的相位雜訊和業界領先的輸出管腳間偏差。新產品組合超越了目前第一代、第二代和第三代PCIe標準的要求,還支援降低電磁干擾的擴頻技術(SST)。該PCIe產品系列是對麥瑞半導體不斷擴大的高性能時鐘發生器和時鐘分配產品的補充。用戶可以聯繫當地麥瑞半導體代表或分銷商訂購樣品。

|

| 麥瑞半導體推出PL6020xxx和PL6070xxx時鐘發生器及SY7557xL時鐘分配產品。 |

麥瑞半導體的PCIe時鐘發生器提供1路、2路、4路或8路輸出,具有業內領先的低於200飛秒的相位抖動和50皮秒的輸出管腳間偏差。PL6070xxx還支援有利於降低電磁干擾的擴頻技術。該時鐘合成器接受25MHz的基頻晶體或基準輸入,並產生25MHz至200MHz的輸出頻率,在100MHz頻率下偏移10kHz的相位雜訊為-135 dBc。此外,該PCIe時鐘合成器還支援2.5V和3.3V的供電電壓,提高了設計靈活性,降低了功率耗散。

麥瑞半導體的新款SY75576L和SY75578L時鐘緩衝器分別支援4路和8路輸出,為現有和最新PCIe系統設計提供高性能解決方案。SY75576L和SY75578L為要求嚴格的基於PCI Express的伺服器、存儲和網路應用提供低於150飛秒的超低附加抖動和低於50皮秒的輸出管腳間偏差。該產品的卓越性能有助簡化系統級設計和印刷電路板設計,加快產品上市速度。

麥瑞半導體時鐘管理及通信業務部副總裁Rami Kanama表示:“最新推出的PCIe解決方案不僅拓展了我們的時鐘和時鐘管理產品組合,而且再次成為輕鬆超越第三代架構要求的性能最佳的時鐘發生和緩衝解決方案。新產品組合的推出,表明我們致力於通過提供最全面的產品線,成為時鐘管理市場的行業領導者。”

所有器件均適用於-40°C至85°C的工業溫度範圍。器件的封裝符合綠色環保、RoHS和PFOS的要求。器件採用6引腳SOT(1路輸出)、16引腳3mm x 3mm QFN(2路輸出)、24引腳4mm x 4mm QFN(4路輸出)或44引腳7mm x 7mm QFN(8路輸出)封裝。