电子装置系统中,除了逻辑运算元件与感测元件(包括各类电源控制与I/O收发控制)外,记忆体元件也是其中不可或缺的关键零组件。根据不同的应用需求,所需要的记忆体型式类别也会有所差别,所以记忆体的发展也是五花八门,各种读取技术、材料规格、挥发性、非挥发性,乃至於同质、异质的嵌入整合或系统封装都不断地推陈出新。

然而记忆体发展轨迹也可以说只是随着越来越庞大的运算与感测功能而亦步亦趋,所以其应用发展的关键指标就会以容量、速度为重点来观察。由於配合系统发展,当容量与速度越来越大、越来越快,此时各种数据交错复杂、讯号强弱不一,且环境干扰频繁,因此记忆体的可靠度也是未来发展的关键指标。

无止尽的容量扩充需求

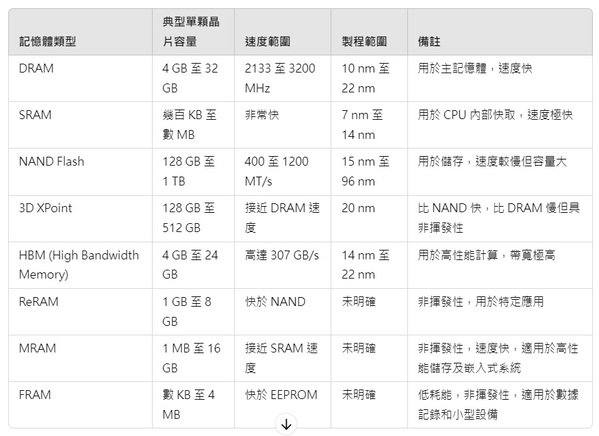

记忆体晶片的容量随着制造技术的进步而持续增加,其中以DRAM的单颗晶片容量发展速度最快,近年来平均每年翻倍。NAND Flash的单颗晶片容量发展速度也很快,但略低於DRAM。SRAM和HBM的单颗晶片容量发展速度相对较慢。

DRAM的单颗晶片容量不断提升,主要得益於制程技术的进步。制程技术的进步使得晶片上的晶体管尺寸更小,从而可以容纳更多的晶体管。

NAND Flash的单颗晶片容量不断提升,主要得益於3D NAND技术的应用。3D NAND技术将NAND Flash的储存单元堆叠在多层中,从而提高了空间利用率。

SRAM和HBM的单颗晶片容量发展速度相对较慢,主要原因是其对性能和功耗的要求更高。SRAM需要保证高速的存取速度,HBM需要保证高频宽和低功耗。因此,SRAM和HBM的制程技术需要更加成熟,成本也更高。

在未来,随着制程技术的不断进步,各类记忆体的单颗晶片容量将继续提升。预计到2030年,DRAM的单颗晶片容量将达到128GB,NAND Flash的单颗晶片容量将达到32Tb,SRAM的单颗晶片容量将达到1Gb,HBM的单颗晶片容量将达到128GB。

记忆体单颗晶片容量的提升,将带来以下好处:

1.降低记忆体成本:单颗晶片容量越大,生产记忆体的成本就越低,从而降低记忆体的价格。

2.提高电子设备的性能:更大的记忆体容量可以使电子设备执行更复杂的任务,并存储更多资料。

3.促进新应用和服务的发展:更大的记忆体容量将使开发人员能够开发新的应用和服务,例如大数据分析、人工智慧等。

总体而言,记忆体单颗晶片容量的提升是未来记忆体发展的重要趋势,将对电子设备和应用产生深远的影响。

| 图一 : 主要记忆体类型在容量和速度速度方面的表现。(请用T1.xlsx档案制作) |

|

配合运算速度的高频记忆体需求

目前DDR5的频率可达6400 MT/s比DDR4高出约50%,主要得益於其采用了新的传输协议。DDR5的传输协议可以同时传输两个资料字节,从而提高了传输速率。DDR6和DDR7的标准尚未正式发布,但根据预测,DDR6的单颗晶片速度将比DDR5高出约50%,达到8000 MT/s至12000 MT/s。DDR7的单颗晶片速度将比DDR6高出约50%,达到12000 MT/s至18000 MT/s。

在HBM方面,HBM2e的单颗晶片速度比HBM2高出约25%,主要得益於其工作频率更高。HBM2e的工作频率为1250 MHz,而HBM2的工作频率为1000 MHz。

在未来,随着制程技术和传输协议的不断发展,各类记忆体的单颗晶片速度将继续提升。而记忆体单颗晶片速度的提升,将带来以下好处:

1.提高电子设备的性能:更高的记忆体速度可以使电子设备执行更复杂的任务,并处理更大的资料量。

2.降低功耗:更高的记忆体速度可以使记忆体控制器工作在更低的电压下,从而降低功耗。

3.促进新应用和服务的发展:更高的记忆体速度将使开发人员能够开发新的应用和服务,例如高性能计算、人工智慧等。

总体而言,记忆体单颗晶片速度的提升是未来记忆体发展的重要趋势,将对电子设备和应用产生深远的影响。

万无一失的可靠度需求

可靠度是评估电脑记忆体的一个关键指标,特别是在数据中心、企业级伺服器和关键任务应用中。记忆体的可靠度影响到整个系统的稳定性和数据的安全性。以下是几个主要的可靠度相关方面:

1.错误更正代码(ECC)

ECC记忆体:专为检测和修正常见的数据腐败问题设计。这对於保证数据完整性尤其重要,避免了数据损坏和系统崩溃的风险。

2.耐用性和寿命

耐用性:尤其是在非挥发性记忆体(如SSD)中,记忆体单元可以承受的写入次数有限,因此提高耐用性是记忆体技术创新的重点。

寿命:随着时间的推移,记忆体元件会因为物理疲劳和其他因素而老化。技术创新旨在延长记忆体的使用寿命。

3.数据保护和安全

数据保护:防止数据丢失和故障的技术(如RAID技术)是评估记忆体可靠性的一个重要方面。

安全:记忆体技术的发展同样集中於增强数据安全性,如加密技术的整合,以防止数据被未授权访问。

4.环境适应性

温度和环境影响:记忆体在不同的温度和环境条件下的性能表现也是其可靠性的重要指标。对於特定应用,如航天或军事用途,记忆体必须能在极端条件下可靠运作。

这些可靠性特点对於确保系统的整体健康和防止数据损失至关重要,并对选择适用於特定应用的记忆体产品提供了重要的叁考。

系统级记忆体整合方案

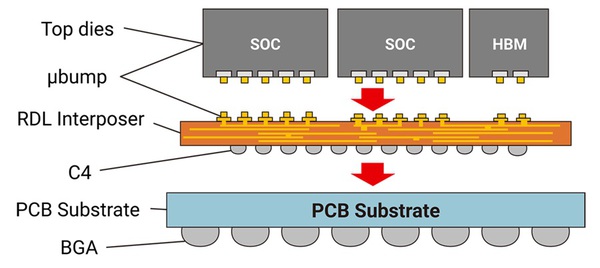

为了使记忆体应用达到更高的性能(低延迟、容量堆叠)、更低的功耗和更小的物理空间需求,系统级整合技术也是一种主要的解决方案。简单而言,系统级记忆体整合可分成直接将晶粒堆叠在系统单晶片(SoC)中,或利用封装技术堆叠晶片与连接基板(SiP),或者结合以上两种的CoWoS(3D IC)封装技术。

不同的记忆体整合在一个晶片上,需要有一个设计平台,例如??创科技开发的异质整合平台MemorAiLink,提供多样化的记忆体选择和完整的记忆体介面 IP 服务。该平台旨在最隹化系统单晶片(SoC)的整体效能和成本,并缩短产品上市时间。

所以,系统级的记忆体整合种类也有非常多元的发展,主要还是看应用上的需求,在伺服器、AI PC或各类边缘运算上的记忆体整合都可能采用不同的创新模式,来满足其设计理念。在此就以目前最受瞩目的CoWoS来说明其技术应用:

| 图二 : TSMC的一型CoWoS-R先进封装制程示意图 (Source:TSMC官网) |

|

CoWoS(Chip-on-Wafer-on-Substrate)是一种先进的封装技术,具有以下优势:缩短线路长度:CoWoS技术可以将多个晶片堆叠在一起,缩短晶片之间的线路长度,从而提高传输速度和降低功耗。提高散热效率:CoWoS技术可以利用矽中介层(Interposer)将晶片与基板隔开,从而提高散热效率。提高设计灵活性:CoWoS技术可以将不同类型的晶片整合在一起,例如CPU、GPU、记忆体等,提高系统的整合度和灵活性。因此,CoWoS技术非常适合用於记忆体的整合。

目前,CoWoS技术主要应用於高性能计算(HPC)、人工智慧(AI)等领域。但在未来,随着CoWoS技术的成本下降和成熟度提高,有??在更广泛的领域得到应用,包括消费类电子产品、物联网(IoT)等。总体而言,CoWoS技术有??成为未来记忆体整合的主要技术之一。随着CoWoS技术的不断发展,记忆体将更加高效、可靠、低功耗,并在更广泛的领域得到应用。

结语

记忆体的种类繁多,为了特定系统的实践应用,不外??容量、速度与可靠度三项指标,这三项指标理想上必须做到互相平衡的状态,也就会是系统运作上的最隹记忆体解决方案。至於低功耗与低延迟的要求,这是基本的环保与品质概念,当然是做到相对越低越好。以上种种指标,促成了挥发性或非挥发性记忆体不断创新且多元发展,也暗示了很难有单一种类记忆体来通吃市场的可能性。