科技進步,一日千里,一轉眼個人電腦市場的CPU速度競賽已經堂堂邁入GHz大關,對消費者來說,相同的荷包預算可以買到愈來愈快的CPU,但對主機板的設計工程師來說,卻是面臨愈來愈大的挑戰,特別是在CPU的電源供應設計上。

VRM是Intel公司制訂的CPU電源需求規格,包括了VID的電壓定義、CPU電壓需求的穩態容忍誤差與暫態容忍誤差等等,因此從CPU電源設計的角度上來看,電力轉換器的性能必須滿足VRM的規範才算合格,而不同的CPU所需求的VRM版本也有不同。VRM8.x的CPU在市場上已經是主流規格很久了,VRM9.0的CPU則是開始如雨後春筍般的出現,並有可能取代VRM8.x的CPU而成為市場主流,不過在尚未非常普及之前,其穩定性與性能表現都需要在大量生產後的實際驗證才能證實。在此新舊規格交替之際,使用VRM9.0的控制IC會有複雜、高成本的問題,而VRM8.x的控制IC在市場上選擇多、價格便宜、穩定性高,而且可以延續過去的設計經驗,因此如何使用VRM8.x的PWM IC來設計滿足VRM9.0 CPU的電源供應,成為相當有競爭力的解決方案。

CPU電源系統架構的演進

由於新一代CPU對電源的需求愈來愈多,也愈來愈苛,CPU的電源供應設計也面臨更多的挑戰;從過去CPU演進的趨勢與特點可以發現,CPU的電源電壓需求愈來愈低,而且在CPU追求速度狂飆的趨勢之下,電流的需求也愈來愈大,這些特點都反映在CPU的電源設計上,而我們也可由此來瞭解一下電源系統架構的演進,(圖一)畫出了幾種常見的架構。

早期的CPU電流需求不大,電源系統只要一顆LDO就可解決,然而LDO的缺點在於效率差,所損耗的能量在電流需求增加時也愈明顯,且散熱也是相當頭疼的問題,因此切換式的電源設計開始成為主流。

要採用切換式的電源設計最簡單的架構就是Buck架構,或是稱為降壓式轉換器,由於設計簡單,而且整個效率、性能表現都凌駕於前一代的LDO電源系統之上,因此立刻成為最為普遍廣泛的設計。Buck Converter的架構也成為未來CPU電源系統的基本架構,所有的新設計與技術都是以Buck為基礎來進行改良的。

由傳統的Buck Converter演進到Synchronous Buck架構,主要是基於效率的考量,其差異是將Buck中的飛輪二極體改為MOSFET,而從控制上的角度來看,這個MOSFET的切換動作恰好和原來的MOSFET形成互補,而效率提高的主要原理是要利用下臂MOSFET的導通壓降低於原來採用二極體時的壓降。不過原來的二極體並不見得一定要拿掉,因為在上下臂交替切換的休時時間(Dead Time)中,還是需要二極體來負責電流轉移的工作,這個二極體可以用下臂MOSFET的Body Diode,但壓降較大,如果有外加一個Schottky Diode,那麼在休息時間的二極體壓降損耗又可以再降低。

事實上從電力電子技術的角度來看,一旦Converter的架構確定了,系統性能的表現會受到選用元件特性相當大的影響,因此讀者會發現電源設計的焦點會開始放在元件的選擇之上,甚至元件的ESR、ESL以及寄生電容等平常不是很重要的參數,在CPU的電源系統設計上,反而成為整體性能表現,甚至於成敗的重要關鍵。

當單純Synchronous Buck架構也不敷使用時,Power Device的併聯技術開始廣泛的應用,包括MOSFET、Schottky Diode、電感、電容等。元件併聯的優點主要有二,第一個是分擔電流,因此元件的電流額定可以少一半,而元件上ESR所產生的損失也會少一半;第二個是元件的放置和線路的Layout會比較有彈性,這一點對電容器在電源系統中所扮演的角色更為重要,也對轉換器的輸出特性有顯著的影響。

Multi-Phase技術則是對新一代CPU電源需求所提出的解決方案,基本的原理也是併聯,不過不是功率元件的併聯而是整個電源模組的併聯。Multi-Phase最大的優點除了使用多組電源模組分擔負載電流之外,是利用不同電源模組間PWM信號的相位位移來達到降低輸出漣波的目的,這個特性對於現在CPU的核心電壓都低於2V以下來說是相當重要的,一方面可以更容易符合電壓誤差的規範,另一方面也可減少輸出濾波器的大小。然而應用Multi-Phase的技術會使得控制系統變得複雜,而且牽涉到Current Sharing的問題,因此要採用這樣的解決方案,會在成本上付出比較大的代價,至少在現階段Multi-Phase的控制IC剛問世不久的時期內會是如此。

CPU電源設計架構選擇

在面對目前需求大電流的CPU場合,大概有下列三種的電源設計選擇:

使用一組Synchronous Buck架構,配合Power Device的併聯使用

此架構是延續Synchronous Buck的架構,因此PWM IC與控制回路的架構也都相同,不需大幅地改版之前的設計,成本與過去類似。在電源轉換的部份,利用MOSFET/Schottky元件的併聯使用,可以有效的降低導通損失,並一起分擔負載電流的大小。但是,隨著電流需求的提高,元件的切換損失會成為主要的功率損失來源,在輸出濾波器的部份,電感的併聯也可降低因ESR造成的損失,輸出電容器的ESR直接影響到負載調整率和暫態特性。在輸出電壓要求愈來愈低時,電源電路的佈線也變得更為敏感,直接影響電源轉換系統的性能。

使用Multi-Phase技術,採用Multi-Phase整合控制IC

這是目前這個產業中最新的解決方案,目前比較常見的設計是兩個與三個Phase的設計。使用Multi-Phase技術的優點是輸出電壓與電流的漣波會衰減不少,因此在輸出濾波器的設計上,元件的值會比單純的Synchronous Buck小,這表示電容的成本可以節省,同時多組的電源模組也可達到分擔負載電流的目的。但是在成本方面,採用Multi-Phase整合控制IC會比一般的Synchronous Buck的PWM IC貴上許多。

使用Multi-Phase技術,採用Synchronous Buck控制IC加上額外的電流控制回路

如果考慮到Multi-Phase整合控制IC的價格太高,但是又想引入Multi-Phase的技術,那麼另外一個方式是從技術著手,可以Synchronous Buck的控制IC來作為個別電源轉換模組的控制核心,然後再加上另外設計的電流控制回路來完成電流分配(Current Sharing)的功能。不過這樣的設計對於工程師來說會是一個蠻大的挑戰,尤其在電流控制回路與相位差的設計部份,完成的系統會比較複雜,而且元件和走線會佔比較大的PCB面積。

對於上面的三種解決方案來說,第三種因為控制技術上過為複雜,因此即使成本上有優勢,也不建議使用。第一種或第二種方案則是比較適當的選擇,雖然使用Multi-Phase的整合控制晶片時所需的電容法拉值可以減少,不過在控制晶片的部份,價格會高出蠻多的,因此整體比較的結果,第一個方案會是比較經濟實惠的方案,特別對於低價的電腦市場,這樣的解決方案是更具有吸引力的。

部份讀者可能會關心的是,從散熱的觀點來比較這兩種方案的實用性;根據筆者的實測經驗和資訊,兩者在大電流(負載約40A)的工作條件下,使用Surface Mount的MOSFET,溫度都會高達100oC左右,兩者的溫度差則大約差10oC左右(Multi-Phase較低)。這樣的結果其實也是可以預測的到的,因為就MOSFET來說工作電流還是那麼大,因此導通損失是差不多的,而個別MOSFET的切換頻率其實也差不多,因此切換損失也是差不多,所以整個MOSFET上所消耗的功率也是接近的。

不過這樣的溫度其實還是有降低的空間,舉例來說,如果MOSFET是採用TO220包裝並加上散熱片,那麼對散熱的效果會大有幫助,如果再加上風扇的協助導熱,MOSFET的溫度會降低更多。事實上,從電力電子技術的角度來看,在45A這樣的電流應用之下,採用Hard Switching技術架構的Buck Converter,要完全靠PCB的銅箔來散熱已經是愈來愈不可能的了,如果不引入Soft Switching的技術,MOSFET加散熱片或加上額外的風扇來處理散熱的問題會是必然的趨勢。

VRM8.x到VRM9.0的VID轉換

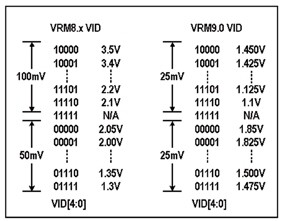

除了考慮大電流的需求必須在電力轉換架構上做改變之外,在此VRM8.x與VRM9.0的規格交替之際,VID所定義的電壓範圍不同也造成了沿用既有VRM8.x規格的PWM IC至VRM9.0系統上的限制,但是透過控制IC外部迴授電路的調整,VRM8.x的VID設定可以調整到符合VRM9.0的VID電壓設定。在介紹實際的電路應用設計之前,我們先來比較一下VRM8.x和VRM9.0的電壓設定值的差別到底在哪裡,透過下面(圖二)中的圖示會比較容易瞭解。

| 《圖二 VRM8.x與VRM9.0的VID對應電壓設定比較》 |

|

從圖中可以清楚的比較出來VRM8.x和VRM9.0的的VID電壓對應值的差異,主要包括了兩個部份:

1.定義的電壓範圍不同。VRM8.x是從1.3V~3.5V,而VRM9.0則是從1.1V~1.85V

2.電壓步階(Voltage Step)不同。VRM8.x的步階在VID4=1時是100mV,在VID4=0時是50mV(註:VID4即為五個VID位元的Msb),而對VRM9.0而言,在所有的範圍內都是25mV。

瞭解VRM8.x和VRM9.0的VID差異之後,接下來要看的是如何做簡單的線性轉換,(圖三)簡單的畫出了轉換的流程,參考這個圖會比較清楚轉換的關係。

1.首先看VRM8.x的VID對應電壓表的部份,我們會發現在VID4=1時,定義電壓的範圍是2.1V~3.5V,這個部份的電壓在VRM9.0中是完全沒有用到的,因此這個部份可以直接刪除。對VRM8.x的PWM IC而言,VID4可以直接接地,此時VID電壓表只包含了16個值,由VID0~VID3來定義。

2.在16個電壓值的部份,電壓步階都是50mV,為了要達到VRM9.0的電壓步階都是25mV的目的,我們可以加入一個新的VID5,用來定義這些電壓值是否在加上25mV的步階。如圖二中STEP 1的部份所示,當VID5=1時,原來的電壓值保持不變(由VID0~3)定義,當VID5=0時,原來的時再加上25mV。因此我們又可以得到5個VID定義的32個電壓值,而且是25mV的電壓步階。

3.如此一來,這些電壓值的範圍為1.3V~2.075V,和VRM9.0的電壓範圍差異只剩下一個Offset,這個Offset的值是225mV(2.075-1.85=0.225),接下來就是把電壓表中的每一個值都減掉225mV就可以了,如圖二中的STEP 2所示,因此我們可以得到完全吻合VRM9.0的電壓設定。唯一的例外是11111在VRM9.0中是定義為「No CPU」,而我們由VRM8.x轉換過來的VID電壓表中是1.075V。

4.最後還有一件事要做的就是把VID0~3與VID5重新排序,以符合VRM9.0的VID順序。原來的VID0~3更名為VID1~4,而VID5更名為VID0,這樣的結果就會和VRM9.0的VID順序吻合了。

電路上的實現

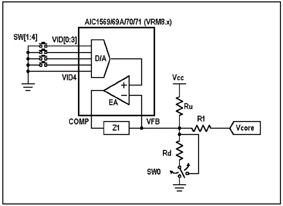

在電路上要實現的功能主要包括了「+25mV」與「-225mV」兩個部份,要如何做呢?我們可以從Buck Converter控制回路中的誤差放大器(Error Amplifer)動作原理來看。通常在PWM IC中的誤差放大器一支輸入接腳是參考電壓(Reference Voltage),也就是前面提到由VID設定,經過DAC(Digital/Analog Converter)轉換的參考電壓,另一隻腳則是迴授電壓的輸入,如(圖四)所示。

對誤差放大器來說,在控制系統中所扮演的角色是要維持兩支輸入接腳的電壓相同,因此只要適當的調整迴授的電壓比例就可以達到調整輸出電壓的目的。(圖五)說明了調整迴授電壓的兩種方式。

在圖五中,R1是原來迴授控制器(由誤差控制器和Z1, Z2組成)中的Z1,我們只要另外加上一個電阻,一端連接VFB接腳,另一端連接至接地點或是一個大於Vcore的電壓源,就可以利用分壓的原理達到調整輸出電壓的目的。以接一個電阻下地的例子來說,Vcore一定會大於VFB,因此我們可以出在R1上所需的25mV電壓差。同樣的,在接一個電阻到電壓源的部份,Vcore一定是小於VFB,因此也可以設計出225mV的電壓差。兩個電阻Rd和Ru的值算出來後,利用重疊原理,就可以完成電路的實現。詳細的阻值設計和分析可以參考本文最後之參考文章[1]。最後整個電路的架構如(圖六)所示。

| 《圖六 VRM8.x VID轉換至VRM9.0 VID電路架構》 |

|

如圖六所示,Ru電阻的效果是將Vcore電壓減少225mV,而Rd則是根據SW0的選擇來決定是否將Vcore提高25mV,因此整體而言,要完成VID的轉換只需多加上兩個電阻和一個DIP Switch,就成本上來說的確是非常經濟實惠的。不過這樣的應用也有一些小問題是需要注意到的,主要是在設計Ru和Rd的值時,會受到VID設定的影響,因此在不同的電壓設定時會有一些誤差,不過這個誤差還不至於差到25mV的一半,因此仍然是可以接受的解決方案。如果要深究這個問題,其實還是有辦法解決的,因為其實這樣的VID轉換原理是在控制R1電阻上的電壓降,而R1的端電壓差是由Vcc/Gnd與Vcore決定的,因為Vcore改變,影響了R1上的電流大小,所以才會造成R1端電壓差的變化,因此要完整解決這個問題的方法,可以採用在VFB注入電流,並控制此電流源的大小,這樣R1電阻上的電壓差就不會受到Vcore的影響,單純地由注入電流的大小和R1的阻值來決定。這個電流源的設計只需一個LM358和幾個電阻就可以完成[2]。

結論

應用VRM8.x的PWM控制IC來滿足VRM9.0的CPU需求充滿了許多不同的挑戰,包括除了電力轉換器的架構必須加強以滿足更大的電流需求外,在功率元件的選取、驅動電路的設計等方面都需重新檢討,以確保電源的供應滿足VRM9.0的需求。然而其中最令人頭疼的還是VID的轉換問題,因為大部份VRM8.x PWM IC的DAC是內建於IC之中,而且DAC輸出的Vref信號也無法提供外部電路使用,因此只能從迴授控制系統來著手。然而這些問題在沛亨半導體都已經有提供完整的Total Solutions,包括高達45A的High Current Demo Board、Application Note與完整的技術支援,有興趣的讀者可以直接與該公司聯絡。

[1]Silvan Ho, "A novel, cost-effective technique for converting VRM8.x VID to VRM9.0 compatible VID", Application Note AN00-SR03EN, Analog Integrations Corporation.

[2]詳細應用技術資料可與沛亨半導體(AIC)產品應用課工程師聯絡,電話(03)5772500 ext881,地址:新竹科學工業園區工業東九路9號4F。