電子裝置系統中,除了邏輯運算元件與感測元件(包括各類電源控制與I/O收發控制)外,記憶體元件也是其中不可或缺的關鍵零組件。根據不同的應用需求,所需要的記憶體型式類別也會有所差別,所以記憶體的發展也是五花八門,各種讀取技術、材料規格、揮發性、非揮發性,乃至於同質、異質的嵌入整合或系統封裝都不斷地推陳出新。

然而記憶體發展軌跡也可以說只是隨著越來越龐大的運算與感測功能而亦步亦趨,所以其應用發展的關鍵指標就會以容量、速度為重點來觀察。由於配合系統發展,當容量與速度越來越大、越來越快,此時各種數據交錯複雜、訊號強弱不一,且環境干擾頻繁,因此記憶體的可靠度也是未來發展的關鍵指標。

無止盡的容量擴充需求

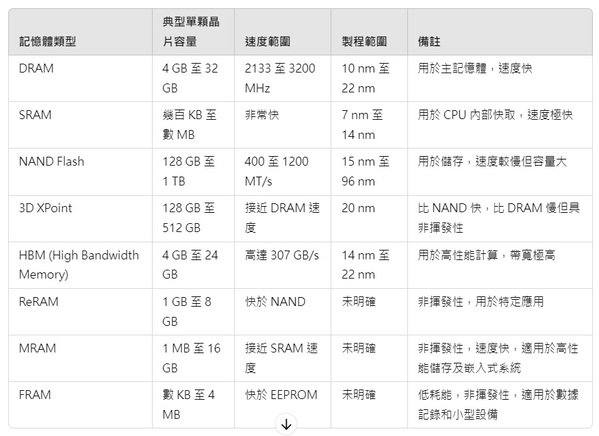

記憶體晶片的容量隨著製造技術的進步而持續增加,其中以DRAM的單顆晶片容量發展速度最快,近年來平均每年翻倍。NAND Flash的單顆晶片容量發展速度也很快,但略低於DRAM。SRAM和HBM的單顆晶片容量發展速度相對較慢。

DRAM的單顆晶片容量不斷提升,主要得益於製程技術的進步。製程技術的進步使得晶片上的晶體管尺寸更小,從而可以容納更多的晶體管。

NAND Flash的單顆晶片容量不斷提升,主要得益於3D NAND技術的應用。3D NAND技術將NAND Flash的儲存單元堆疊在多層中,從而提高了空間利用率。

SRAM和HBM的單顆晶片容量發展速度相對較慢,主要原因是其對性能和功耗的要求更高。SRAM需要保證高速的存取速度,HBM需要保證高頻寬和低功耗。因此,SRAM和HBM的製程技術需要更加成熟,成本也更高。

在未來,隨著製程技術的不斷進步,各類記憶體的單顆晶片容量將繼續提升。預計到2030年,DRAM的單顆晶片容量將達到128GB,NAND Flash的單顆晶片容量將達到32Tb,SRAM的單顆晶片容量將達到1Gb,HBM的單顆晶片容量將達到128GB。

記憶體單顆晶片容量的提升,將帶來以下好處:

1.降低記憶體成本:單顆晶片容量越大,生產記憶體的成本就越低,從而降低記憶體的價格。

2.提高電子設備的性能:更大的記憶體容量可以使電子設備執行更複雜的任務,並存儲更多資料。

3.促進新應用和服務的發展:更大的記憶體容量將使開發人員能夠開發新的應用和服務,例如大數據分析、人工智慧等。

總體而言,記憶體單顆晶片容量的提升是未來記憶體發展的重要趨勢,將對電子設備和應用產生深遠的影響。

| 圖一 : 主要記憶體類型在容量和速度速度方面的表現。 |

|

配合運算速度的高頻記憶體需求

目前DDR5的頻率可達6400 MT/s比DDR4高出約50%,主要得益於其採用了新的傳輸協議。DDR5的傳輸協議可以同時傳輸兩個資料字節,從而提高了傳輸速率。DDR6和DDR7的標準尚未正式發布,但根據預測,DDR6的單顆晶片速度將比DDR5高出約50%,達到8000 MT/s至12000 MT/s。DDR7的單顆晶片速度將比DDR6高出約50%,達到12000 MT/s至18000 MT/s。

在HBM方面,HBM2e的單顆晶片速度比HBM2高出約25%,主要得益於其工作頻率更高。HBM2e的工作頻率為1250 MHz,而HBM2的工作頻率為1000 MHz。

在未來,隨著製程技術和傳輸協議的不斷發展,各類記憶體的單顆晶片速度將繼續提升。而記憶體單顆晶片速度的提升,將帶來以下好處:

1.提高電子設備的性能:更高的記憶體速度可以使電子設備執行更複雜的任務,並處理更大的資料量。

2.降低功耗:更高的記憶體速度可以使記憶體控制器工作在更低的電壓下,從而降低功耗。

3.促進新應用和服務的發展:更高的記憶體速度將使開發人員能夠開發新的應用和服務,例如高性能計算、人工智慧等。

總體而言,記憶體單顆晶片速度的提升是未來記憶體發展的重要趨勢,將對電子設備和應用產生深遠的影響。

萬無一失的可靠度需求

可靠度是評估電腦記憶體的一個關鍵指標,特別是在數據中心、企業級伺服器和關鍵任務應用中。記憶體的可靠度影響到整個系統的穩定性和數據的安全性。以下是幾個主要的可靠度相關方面:

1.錯誤更正代碼(ECC)

ECC記憶體:專為檢測和修正常見的數據腐敗問題設計。這對於保證數據完整性尤其重要,避免了數據損壞和系統崩潰的風險。

2.耐用性和壽命

耐用性:尤其是在非揮發性記憶體(如SSD)中,記憶體單元可以承受的寫入次數有限,因此提高耐用性是記憶體技術創新的重點。

壽命:隨著時間的推移,記憶體元件會因為物理疲勞和其他因素而老化。技術創新旨在延長記憶體的使用壽命。

3.數據保護和安全

數據保護:防止數據丟失和故障的技術(如RAID技術)是評估記憶體可靠性的一個重要方面。

安全:記憶體技術的發展同樣集中於增強數據安全性,如加密技術的整合,以防止數據被未授權訪問。

4.環境適應性

溫度和環境影響:記憶體在不同的溫度和環境條件下的性能表現也是其可靠性的重要指標。對於特定應用,如航天或軍事用途,記憶體必須能在極端條件下可靠運作。

這些可靠性特點對於確保系統的整體健康和防止數據損失至關重要,並對選擇適用於特定應用的記憶體產品提供了重要的參考。

系統級記憶體整合方案

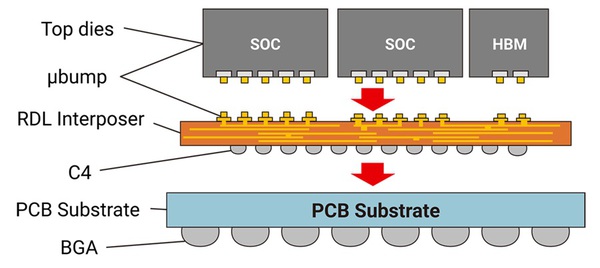

為了使記憶體應用達到更高的性能(低延遲、容量堆疊)、更低的功耗和更小的物理空間需求,系統級整合技術也是一種主要的解決方案。簡單而言,系統級記憶體整合可分成直接將晶粒堆疊在系統單晶片(SoC)中,或利用封裝技術堆疊晶片與連接基板(SiP),或者結合以上兩種的CoWoS(3D IC)封裝技術。

不同的記憶體整合在一個晶片上,需要有一個設計平台,例如鈺創科技開發的異質整合平台MemorAiLink,提供多樣化的記憶體選擇和完整的記憶體介面 IP 服務。該平台旨在最佳化系統單晶片(SoC)的整體效能和成本,並縮短產品上市時間。

所以,系統級的記憶體整合種類也有非常多元的發展,主要還是看應用上的需求,在伺服器、AI PC或各類邊緣運算上的記憶體整合都可能採用不同的創新模式,來滿足其設計理念。在此就以目前最受矚目的CoWoS來說明其技術應用:

| 圖二 : TSMC的一型CoWoS-R先進封裝製程示意圖 (Source:TSMC官網) |

|

CoWoS(Chip-on-Wafer-on-Substrate)是一種先進的封裝技術,具有以下優勢:縮短線路長度:CoWoS技術可以將多個晶片堆疊在一起,縮短晶片之間的線路長度,從而提高傳輸速度和降低功耗。提高散熱效率:CoWoS技術可以利用矽中介層(Interposer)將晶片與基板隔開,從而提高散熱效率。提高設計靈活性:CoWoS技術可以將不同類型的晶片整合在一起,例如CPU、GPU、記憶體等,提高系統的整合度和靈活性。因此,CoWoS技術非常適合用於記憶體的整合。

目前,CoWoS技術主要應用於高性能計算(HPC)、人工智慧(AI)等領域。但在未來,隨著CoWoS技術的成本下降和成熟度提高,有望在更廣泛的領域得到應用,包括消費類電子產品、物聯網(IoT)等。總體而言,CoWoS技術有望成為未來記憶體整合的主要技術之一。隨著CoWoS技術的不斷發展,記憶體將更加高效、可靠、低功耗,並在更廣泛的領域得到應用。

結語

記憶體的種類繁多,為了特定系統的實踐應用,不外乎容量、速度與可靠度三項指標,這三項指標理想上必須做到互相平衡的狀態,也就會是系統運作上的最佳記憶體解決方案。至於低功耗與低延遲的要求,這是基本的環保與品質概念,當然是做到相對越低越好。以上種種指標,促成了揮發性或非揮發性記憶體不斷創新且多元發展,也暗示了很難有單一種類記憶體來通吃市場的可能性。