量子电脑可??在特定应用领域带来巨变,包含材料合成、药物开发、网路安全等等。在量子电路的运算模型中,量子逻辑闸(简称量子闸)利用少数量子来进行基本运算,与传统数位电路里的逻辑闸雷同。量子是量子电路的基本构件。全球正在努力开发具备不同类型量子位元的量子运算平台,期??能将应用从实验室扩展到全球。

其中一项前景看好的量子运算技术透过超导电路运行。Anton Poto?nik是深耕量子运算领域的imec资深研究员,他表示:「超导量子位元的能量状态相对容易操控,经过这几年,研究人员已能将越来越多的量子进行耦合,进而实现更进阶的量子纠缠这是量子运算发展的其中一大支柱。除此之外,全球各地的研究团队已经公开展示超导量子位元的优异性能,包含维持量子态长达数百微秒的相干时间,以及达到一定水准的闸保真度(gate fidelity),两者都是量子运算的重要指标。」

相干时间提供我们有关维持量子态(亦即资料保存)的时间资讯;闸保真度则量化了理想的逻辑闸与其在实体量子电路对应的物理闸之间的运算误差。

大型量子电脑的发展阻碍:变异度问题

目前为止,刚刚提到的量子运算效能只能在实验室看到成果,利用双角蒸镀法(double-angle evaporation)与剥离成形(lift-off)技术来制出最关键的元件结构:约瑟夫森接面(Josephson junction)。

Anton Poto?nik解释:「基本上,超导量子位元是非线性LC谐振电路,内含一个非线性电感(L)与一个电容(C)。约瑟夫森接面作为非线性且非散热的电感元件,能让我们操控量子位元的能量状态,例如代表|0?与|1?的叠加态。为了把能耗降到最低,也就是尽可能地延长相干时间,约瑟夫森接面与电容的结构内部必须避免各个介面产生瑕疵。在任一介面存在原子大小的瑕疵都有可能导致量子位元损失能量。因此,双角蒸镀法与剥离成形是较为理想的制程方案,它们能制出接近无瑕的介面。」

尽管如此,这些制程技术有一大缺点,那就是难以实现量子位元数量的规模化。蒸镀接面在约瑟夫森效应下产生的超导电流存在一定的变异度,这就阻碍了大规模量子运算。此外,制程技术也会限制超导材料的选择,进而阻碍量子位元进一步改良。

替代方案:CMOS相容制程

imec博士研究员Jeroen Verjauw表示:「imec团队已经探索了超导电路的替代制程方案,主力放在所谓的覆盖式约瑟夫森接面(overlap Josephson junction),仅用与CMOS相容的材料与技术制成,藉此发挥先进CMOS制程所具备的可靠度与再现性(reproducibility)优势,以控制量子位元变异度并实现规模化。」

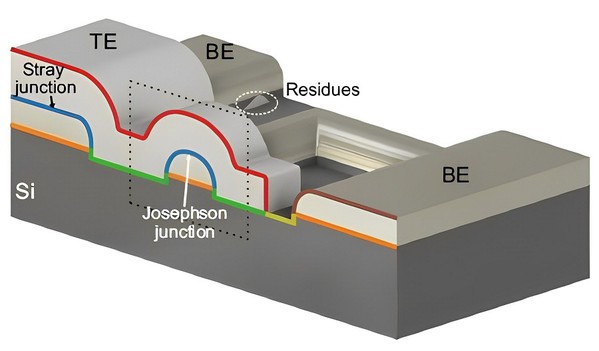

覆盖式接面包含下层(BE)与上层(TE)两个电极,中间以绝缘层薄膜分隔。这些电极经过两次图形化处理,期间导入一次真空制程,真空时会自然生成金属氧化物,後续进行氩气(Ar)蚀刻时必须移除。

| 图一 : 覆盖式接面的截面示意图:上下层电极之间的重叠区域会定义出约瑟夫森接面(以及寄生杂散接面)的图形。侧壁会因为蚀刻制程而出现残留物。绿色那层标示了经过氩气蚀刻制程後产生的受损多晶矽层。 |

|

Jeroen Verjauw指出:「不过,氩气蚀刻制程有一定的风险,之前就传出会造成能量耗损。」

量子运算生力军:CMOS制程登场

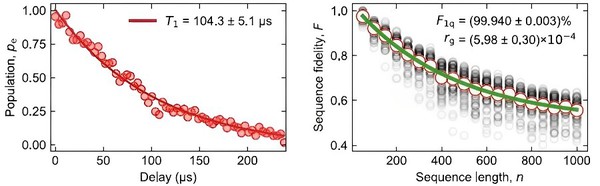

imec研究员Tsvetan Ivanov表示:「我们的实验室展示了超导量子位元的优异效能,相干时间长达数百微秒,平均闸保真度达到99.94%,与其他先进量子晶片效能相当。不同的是,这是首次透过CMOS相容技术来获得进展,像是溅镀沉积与蚀刻制程。改良目前的覆盖式接面制程就能取得这些突破性成果,具体作为包含简化制程步骤与减少介面数量藉此降低能耗损失的风险,还有优化氩气蚀刻制程,并且仅用铝(Al)来制作电极。」

| 图二 : (左)量子位元能量释放的量测结果;(右)平均闸保真度(gate fidelity)与平均闸错误率(error per gate)。 |

|

三大发展目标:进入12寸晶圆厂、降低损耗、提升再现性

imec此次发表的研究成果目前仅在实验室的测试基板上获得验证。Tsvetan Ivanov表示:「虽然如此,此次展示的制程方法仍是重要的里程碑,预告着未来超导量子电路有??进入12寸晶圆CMOS制程。我们很快就能将这些超导电路的制程技术转移至imec的12寸晶圆厂。我们亟欲验证上述的量子态维持时间能否在大尺寸晶圆上达到相同结果。」

Jeroen Verjauw接着说道:「为了研究能耗来源,我们还设计了测试晶片。首批研究结果显示,能量损失主要源於元件结构的表面,而非接面的那层。这项发现令人振奋,因为只要锁定应用导入专用的表面处理技术,就有可能改善问题。最後,我们的制造方案提供了在大尺寸晶圆上大规模制造量子位元的方法,减缓量子位元频率等变异度问题。」

但在实际应用超导量子电脑之前,仍有一些问题需要解决。Anton Poto?nik总结:「超导量子位元(毫米等级)与像是半导体自旋量子位元(奈米等级)相比,仍旧相对较大。我们正在针对元件微缩进行研究,也在努力研发演算法。目前我们做出的量子位元还不尽理想,所以要从理论出发,持续开发具备更能容许损耗与误差的演算法,同时发展量子错误更正协定。此外,我们还会需要可规模化且经过精密校正的仪器来连接持续增加的超导量子位元,进而进行操控与读取有用数据。」

结语

imec量子运算研究计画主持人Kristiaan De Greve认为,此次的研究成果是迈向超导量子位元规模化的重要里程碑,凭藉业界标准制程所具备的操控与准确度优势,将能克服关键挑战。他表示:「未来很可能需要成千上百万个量子位元来构成量子运算处理器,所以突破变异性与产量的限制会是关键。也因此,imec投入大量资源来了解这些发展限制并订定相关标准,同时善用我们在先进制程管制方面的经验,引进创新的解决方案。」

imec量子运算研究计画组长Danny Wan最後补充:「imec量子运算研究计画的成员全都希??能将量子运算带出实验室,扩及全球,不论是采用超导体或半导体。此次刊载於《NPJ Quantum Information》的研究成果大大助长了信心,证实我们走在正确的道路上。」

(本文由imec提供;作者Jeroen Verjauw为imec博士研究员、Tsvetan Ivanov为imec研究员、Anton Poto?nik为imec资深研究员、Danny Wan为imec量子运算研究计画组长、Kristiaan De Greveimec为imec量子运算研究计画主持人;编译/吴雅婷)