台積電本週於舊金山舉行的IEEE國際電子元件會議(IEDM)上,發表了其下一代名為N2的2奈米電晶體技術,也是台積電全新的電晶體架構-環繞閘極(GAA)或奈米片(NanoSheet)。目前包含三星也擁有生產類似電晶體的製程,英特爾和台積電,以及日本的Rapidus都預計在2025年開始量產。

|

| (TSMC) |

根據台積發表內容,與N3(3奈米)製程相比,新技術在提升15%密度的同時,提供了高達15%的速度提升,或30%的能效提升。

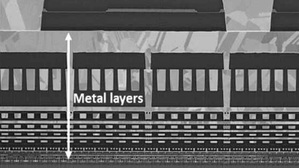

台積電表示,N2是「四年多努力的成果」。現今的電晶體,鰭式場效電晶體(FinFET),其核心是垂直的矽鰭片。奈米片或環繞閘極電晶體則是以一堆狹窄的矽帶取代。

這種差異不僅可以更好地控制通過元件的電流,還可以讓工程師通過製造更寬或更窄的奈米片來生產更多種類的元件。FinFET只能通過增加元件中鰭片的數量來提供這種多樣性,例如具有1個、2個或3個鰭片的元件。但奈米片為設計者提供了介於這些之間的漸變選項,例如相當於1.5個鰭片,或任何更適合特定邏輯電路的選項。

台積電的奈米片技術稱為Nanoflex,允許在同一晶片上構建具有不同奈米片寬度的不同邏輯單元。由窄元件製成的邏輯單元可以構成晶片上的通用邏輯,而具有更寬奈米片、能夠驅動更多電流和更快切換的邏輯單元則可以構成CPU核心。

奈米片的靈活性對處理器主要的片上記憶體SRAM產生了特別大的影響。幾代以來,這個由6個電晶體組成的關鍵電路,其縮小速度一直不如其他邏輯電路。但N2似乎打破了這種縮放停滯的趨勢,產生了迄今為止密度最高的SRAM單元:每平方毫米38兆位元,比之前的N3技術提升了11%。N3相較於其前身僅提升了6%。