厚翼科技(HOY Technologies,簡稱 HOY)日前發佈最新「記憶體測試電路開發環境-BARINS 3.0」,開放使用者自定義Cell Library(元件庫)裡Cell的行為。讓BRAINS學習如果遇到使用者定義的Cell行為,決定記憶體時鐘(Memory Clock)由哪一個時鐘路徑提供,可大幅降低使用者比對記憶體落在時鐘域(Clock Domain)的比對時間,並提供最佳化的記憶體測試電路、大幅縮短測試時間,降低測試費用。

|

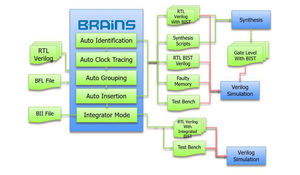

| BRAINS操作流程圖 |

深度學習(deep learning)是在人工智慧(Artificial Intelligence, AI)領域中的一個新興話題,也是成長快速的領域,而AI將引發記憶體測試需求,現已有許多晶片供應商對深度學習的興趣不斷增加,意味著系統單晶片(SoC)對於記憶體的需求量將會大增,進而帶動記憶體測試需求。

厚翼科技最新「記憶體測試電路開發環境-BARINS 3.0」內建數個已知Gate Cell的行為,在Auto Identification後段,進入Auto Clock Tracing之前,BRAINS會開始建立所有Memory的Hierarchy並找出共同的Top Hierarchy。

對照其他記憶體測試開發工具而言找出共同的測試開發工具而言找出共同的Top Hierarchy在複雜的電路中會花費很長的執行時間,以BRAINS3.0而言,但若電路設計沒有大幅更改,之後就可直接使用第一次搜尋的結果,可節省三倍的執行時間。