根据ISO 11898标准,控制器区域网路(Controller Area Network ; CAN)广泛实现在工业与汽车应用。相关CAN协定如 DeviceNet 或 CANOpen 有赖于内建错误检查机制与差动信令技术。电流隔离(Galvanic isolation)可进一步提升稳定性,以额外的传播延迟为代价避免高压暂态状况。即便使用电流隔离,仍可透过最佳化CAN节点组态达到最大资料速率与距离。

传播延迟有何影响?

传播延迟会影响节点之间的并行传输与仲裁。仲裁有赖于CAN信令机制;逻辑0值为支配位元(汇流排线之间的差动电压);逻辑1为闲置位元(全输出高阻抗),这表示支配位元会覆写闲置位元。资料传输时所有节点监控着汇流排上是否发生支配位元覆写,而停止时传送闲置位元意味着其它节点可赢得汇流排仲裁(如图一,节点A所示)。

传播延迟必不可过大,或者要在其他节点支配状态传输之前得以监控汇流排状态。如图二,节点A与B的往返时间甚为关键,以TPropAB 加上 TPropBA表示,或等于通过导线与收发器延迟时间的两倍,如果有,还包括电流隔离带来的延迟。相较于光耦合器,数位隔离器更能降低传播延迟。然而系统容许固定且有限的传播延迟,是以电流隔离的配置将会减低最大导线距离。

传播延迟补偿机制

补偿电流隔离造成的传播延迟可藉由调整CAN控制器的一些特定参数达成。首先参照CAN控制器时脉设定鲍率预定标器(baud rate prescaler;BRP)之值,从而定义出时间刻段(time quantum;TQ)以分割位元时间。如图三所示,以TQ为单位将资料分成三或四个段落,其中一TQ头段用来同步(SYNC),若干长度用于传播延迟(PROP)与相位段(PS1 与PS2),而PS2与总TQ指定了取样点位置。

步骤一:匹配时脉、预定标器与资料速率

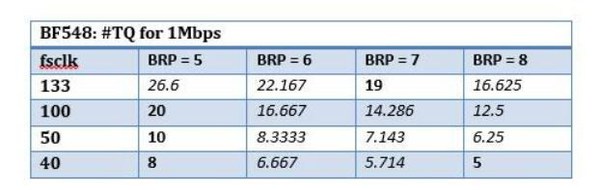

首先要在给定的资料速率条件下找出可能的时脉与BRP设定组合使得TQ为整数。如表一所示,此为ADI内建CAN控制器之ADSP-BF548 Blackfin 微处理器在1Mbps资料速率之下的时脉(fsclk)/BRP组合与对应的TQ。其中TQ为整数,而时脉与TQ以粗体字表示。

| 表一: 1Mbps资料速率条件下之时脉与BRP组合 |

|

步骤二:位元端组态

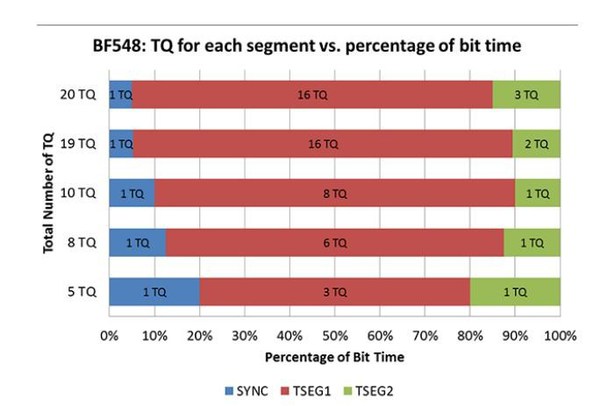

接下来则是定义位元段组态,使其取样点尽量延迟。对于表一的各种选项,SYNC段都必须具有一个TQ,而TSEG2 (PS2)段必须适用CAN控制器处理时间(对于BF548而言小于1TQ,在BRP大于4条件下),TSEG1 (PROP + PS1)段最大为16TQ。

| 图三: 1 Mbps资料速率条件下最大传播延迟所适用的BF548处理器位元段设定 |

|

如图三所示,此为ADSP-BF548处理器在1Mbps条件下各种组态与其最迟取样点。除了5TQ之外所有组态都至少达到85%取样点,其中最佳组态是在10TQ,所适用时脉为50MHz,BRP = 5。

步骤三:计算汇流排长度

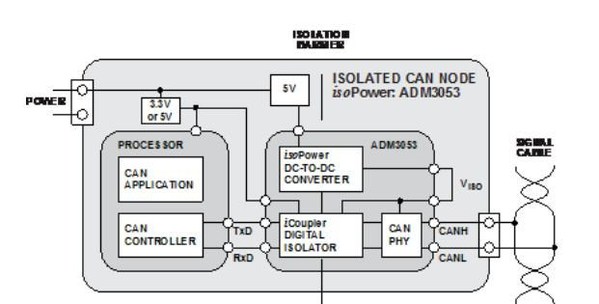

最终则是在所应用的CAN收发器与隔离器最佳组态之下确定最大的传播延迟与决定资料线长度。如图四所示,处理器最佳化组态可达到900ns的传播延迟上限。

| 图四: 使用具备集成隔离电源ADM3053的隔离式区域网路节点 |

|

如图四所示,美商亚德诺(ADI)的ADM3053 晶片整合了CAN收发器,数位隔离器与隔离电源。具备包含隔离器(节点间500 ns)的250 ns回路延迟。假设资料线传播延迟为5 ns/m,意味着以BF548处理器实作汇流排长度可达40公尺(此为根据 ISO 11898标准 1 Mbps条件下之最大值)。

结论

电流隔离提升了稳定性却也造成双向传播延迟,又因两个节点之仲裁而倍增。为了补偿这种效应,可对CAN控制器组态加以配置以适用最大可能的传播延迟,如此一来即使在隔离节点上也能达到令人满意的资料速率与汇流排长度。 (本文作者Conal Watterson为ADI公司资深应用工程师)