就以往的IC製程來說,工廠所能生產的IC尺寸其實都不大。也由於製程較寬的緣故,能夠整合在一起的零組件並不多。一般來說,會先將大尺寸IC排除,而把其餘的小尺寸IC兜在一起。隨著整個製程技術愈趨精良,IC的尺寸也較以往縮小許多,於是IC設計業者開始思考如何把一些主要的IC整合在一起,系統單晶片(System on Chip;SoC)設計趨勢於是逐漸形成。

更由於當前熱門話題--資訊家電(Information Appliance;IA)對於產品講究輕薄短小的需求影響,使得SoC技術領域成為IC設計業者兵家必爭之地。與IC設計業共存亡的EDA產業,亦在此風潮的推波助瀾之下,後勢看漲。對於IC設計業者來說,選擇符合本身需求的EDA工具,是掌握市場契機的重要關鍵;而對EDA廠商來說,具備提供量身訂作的設計服務,方能獲得客戶的青睞與支持。這兩者間的良性互動,也是SoC發展成功與否的不二法門。

製程技術演進與模組化

系統單晶片,顧名思義就是將原本基板上的獨立模組整合一起,像是記憶體或其他較小的核心電路,例如以前的8048、8049或8086等。以手機來說,一個小小的晶片中就包含了許多的模組,如微處理器、傳輸所需媒介(如硬碟所用之DSP)、記憶體、介面(I/O)電路等,全部要放入一個小小的晶片裡,這也就是SoC最簡單扼要的定義。

SoC,系統單晶片,可以被看成是一個完整的系統,系統中涵蓋了CPU、記憶體、輸入/輸出(I/O)裝置及控制時間(Timing Control)流程等功能的模組。能夠將以往各自獨立於基板上的功能模組整合在一起,主要可歸功於製程技術的途破演進,過去製程仍寬的時候,所有的功能模組在基板上各自分開、獨立運作,所需基板體積亦大。如今製程技術演進已趨成熟,各模組間的尺寸差異也縮小到一定程度,原本大尺寸的關鍵零組件已不復見,取而代之的是體積尺寸相仿的模組。設計人員於是開始把關鍵模組試著整合在一起。

模組化與製程轉化難題

而當大多數模組達到一定的製程水準之後,電路設計是否成為一個主要的關鍵?其實並不一定。因為目前大部分都已經是模組化,差別只是在於各家的製程不同,倘若該模組被別家公司所採用,則採用的公司就必須將此模組中原有的舊製程,移轉成該公司自己的新製程,這是一個較為麻煩的過程!

而且,一個模組或許會賣給1~2家公司,也可能賣給數十家公司。舉例來說,ARM是一家生產CPU Core的公司,而Motorola、TI、Ericsson或Siemens等公司會來購買他們的產品;由於ARM和其他公司的製程未必相同,因此就必須有一個轉換模組內部製程的動作,這個過程極為耗時。也因此,目前許多業者已經在思考要建立一個設計製程的標準,適用於各家公司,藉以減去轉移製程的麻煩;不過目前為止仍是一個理想,短期之內還無法達成。

形式不同 功能各異

通常電路設計的模組可概分為「Soft Module」和「Hard Module」兩種。

Soft Module:

主要是以描述的方式將電路圖畫出來。以描述的方式將某個模組與電路相湊合,由於並非實際畫出電路圖,當中所有的設計概念,包括傳輸時可能產生的時間差都是想像的,因此還必須經過將此設計概念轉換成Hard Module的手續,較為耗時,所需的動作相對也較繁瑣,不易操作。

Hard Module:

和Soft Module最大的差異點,在於Hard Module乃是真正在設計後做出一個實體來。由於已經將設計概念落實化,因此有其一定的規格存在;並省略掉設計不符需求的考量,其操作步驟亦較Soft Module來得容易。

一般來說,IC設計業者此兩種Module均有提供,視客戶的需求而定。例如,智原公司Soft Module和Hard Module便兩者兼備。Soft Module因為只需提供設計概念,因此價錢較Hard Module低。對於IC設計人員來說,Hard Module較易上手,所需時間亦較Soft Module減少許多,雖其價錢比Soft Module昂貴,卻可以省去許多負荷。

模組整合 效能提升

以往各個不同作用的模組,獨立放在印刷電路板(PCB)上時,模組間用來連結的媒介是一種金箔製品,但金箔在傳送訊號的時候,速度並不快。現在我們把模組全部整合在同一個晶片裡,縮短模組與模組間的傳送距離後,訊號傳送的速度也就相對加快,功能則不會受到影響。

唯一需要注意的問題是以往IC各自獨立時,金箔面積大,不太需要考慮到電流的影響。如今由於IC都整合在一起,金箔相對變小,電流過大可能會導致金箔破裂,因此需要建立一些緩衝(Buffer)來把大電流改成小電流。至於SoC所擁有最大的優點,就是體積小及省電。而當前正熱門的IA及可攜式產品如行動電話等來說,輕薄短小和低耗電量是最必須的考量。

IC設計模式現況與趨勢

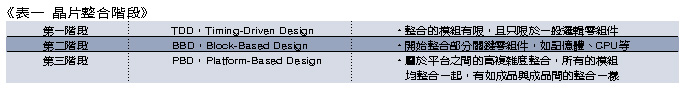

IC設計在初期的設計模式特點為各自獨立的Block,因此只需要處理好個別的Block即可,此階段稱為TDD(Timing-Driven-Design)。之後由於模組逐漸被整合在一起,如記憶體、CPU等,大的Block必須作一整合的動作,此階段稱為BBD(Block-Based Design),目前大多數業者皆可達到此階段。

最後,就是到達所謂平台(Platform)階段,為一較為複雜的整合,稱之為PBD(Platform-Based Design),屬於成品與成品間的高度整合度,目前尚無業者達到此階段,但成為未來趨勢已是必然(表一)。

SoC設計所面臨的問題

無法避免的物理現象:

由於製程變得越來越小,IC幾何大小已經明顯縮減許多,以往不需去注意的問題或物理現象漸漸浮上檯面。例如,在駕駛一輛大卡車時,路面上的小坑洞其實是會被忽略的,因其所能影響的程度還太小,不至於構成大威脅。反之,如果是駕駛一部50CC的小機車時,縱使是路面上的小水窪也可能對駕駛者構成某種程度的威脅。載距變小,所需面臨的現實環境問題當然相對增加,因此許多EDA設計人員的當務之急,便是找出更多不為人知的物理現象問題,以提供更完整的解決方案。

全方位設計人員難尋:

| 《表一 晶片整合階段。 》 - BigPic:685x95 | 資料來源:Cadence |

|

以往的設計人員只需要專注於某一方面的設計,現在則必須對其他部分的設計也要有一定程度上的了解。目前解決這個問題的方法有二種:一是購買該部分已經開發出的成品;另一方法就是找到會設計的人才。然而,無論是購買成品或是培養人力,都需要耗費一段不算短的時間。倘若採用已經設計好的解決方案,則無可避免地必須增加一道將其原有製程轉換成目前所用製程的手續;之後,還需找出合適的溝通介面,測試彼此間的訊號是否相容,過程十分非常耗時耗力。因此許多業者正積極規劃,希望能夠合作制訂一個全球共通的標準,但仍未達成。

協同設計工具因運而生:

在設計完硬體工具後,EDA設計人員還須設計一些讓程式進行的軟體,讓SoC設計人員能把軟體放到電腦中去模擬。因此,現在的設計人員必須做到硬體與軟體整合模擬的工作,而不再像以往只需設計硬體,單單傳送數位訊號的模擬即可。硬體同時也必須執行一些軟體程式,配合硬體的訊號,同時測試結果。因此出現了一個新的名詞「System Level Design」--系統層級設計。協助此種設計的工具則稱之為Co-Simulate Tool,也就是整合硬體和軟體的協同設計工具。

| 《圖二 EDA業者網站—益華網站。 》 | 資料來源:http://www.cadence.com |

|

類比和數位整合困難重重:

前面所討論的皆屬於數位(Digital)訊號的部分,現在如果把類比(Analog)訊號一併整合進來,將是更浩大、更難臻完善的理想,因為牽涉到更為複雜的問題。例如,高頻線路會產生干擾,EDA設計人員就必須針對此部分,模擬出在何種情形下會出現何種程度的干擾現象,還要考量設計時的頻寬問題。因此在類比與數位的整合部分,將是EDA設計人員所面臨最大的挑戰。目前來說,要做到完全整合,仍是一項「不可能的任務」。

此外,由去年年底開始,許多的晶圓廠紛紛將原本的0.25微米製程,調整為0.13或0.18微米製程,這對於設計人員來說,所面臨的最大問題為其運算部分的Timing架構會不同,連帶也會影響到系統(System)端的Timing問題。

| 《圖三 EDA業者網站—明導資訊。 》 | 資料來源:http://www.mentor.com |

|

IC設計趨勢與EDA工具

IC設計的演進正邁向一個新階段,而「工欲善其事,必先利其器」,EDA工具就扮演非常重要的角色,以下將針對SoC的設計演進及各階段所需工具做一概述:

第一階段:模擬、佈局工具

早期製程仍大時,晶片中所能置入的電晶體數量十分有限,最多只能放進大約20萬個邏輯閘,但現在卻已可以放入400~500萬個邏輯閘。同樣地,過去做IC設計也比現在容易許多,因為所要畫的電路圖並不多,因此IC設計人員通常會把所有的電路圖都畫出來,直接送去模擬、測試該電路圖可不可行。在當時,主要工具是用來模擬邏輯閘,然後再將電路圖轉成光罩,因此所需工具有二個:模擬電路圖的模擬工具(Simulation Tool)和製作光罩的佈局工具(Place & Route Tool)。

第二階段:合成工具

然而,不可避免的是電路圖也可能畫錯,所需時間也可能很長。許多設計人員於是想到,如果不必親自去畫電路圖,一定可以節省不少時間,於是有了合成工具(Synthesis Tool)。合成工具最大的功能在於只需描述各個模組的功能為何,卻不需親自畫出電路圖。舉例來說,如果要做一個計時器,只要把計時器所需的功能概念告訴合成工具,模組有幾個Pin腳,每一個Pin腳的功能又是什麼,合成工具便會自動將電路圖畫出。其高達100%準確度和時間短的優勢,著實提供給IC設計人員很大的協助。以目前來說,已是很普遍的協助設計軟體。

第三階段:電路切割工具

時至今日,當有更多的電路可以被整合一起時,合成工具儼然已成為必備的工具之一,同時也成為當前各EDA業者亟欲發展的現階段課題。面對愈來愈多、愈來愈複雜的電路圖,設計人員必須將其做一分隔(Partition),我們把這類工具稱為電路切割(Design Planning)工具。電路切割工具可以把一個模組中的不同電路依照其功能不同,預先分隔成幾個部分,讓其獨立的電路各自運作完成之後,再將其整合一起。如此一來,便能夠分工合作且齊頭並進,省去許多時間,使設計流程更具時間效益。

國內EDA發展現況與趨勢

愈來愈多的客戶需求,及受整體大環境的影響,促使台灣業者也積極朝向SoC之路前進。因此,用來輔助IC設計的EDA產業地位也蓬勃發展。EDA可稱為是一個標準範本,讓許多設計人員可以依循其中的捷徑走,而省去多數耗時費力的麻煩。對於設計者來說,一個適當而功能強大的EDA輔助工具,可以協助他們在最短時間內設計出最佳的IC產品。

一般來說,我們將IC設計大概分成合成、佈局及實體驗證三部分。EDA業者亦針對此部分各自推出不同的設計服務。以國內業者而言,新思科技(Synopsys)在合成階段的著墨最多,也最為成功;前達科技(Avant!)則是專攻於佈局階段;而明導資訊(Mentor)則是注重在光罩出去前的實體驗證部分,至於益華電腦(Candence)今年則力推提供整段製程的解決方案(圖一)。

IC設計和EDA產業之間,其實可說是相輔相成的關係。IC設計業者採用EDA協助工具,縮短其設計時程,就等於降低了成本。對於業者來說,當然是大利多,在邁向SoC的上,這樣的衣存關係也將更為明顯。SoC目前或許還屬於口號階段,但卻是業者亟欲達到的目標,也是未來業者生存必須之路徑。