前言

低端柵極驅動器IC是專用放大器,普遍用於電源設計中,根據來自PWM控制器的輸入信號開關接地參考MOSFET和 IGBT。對於低於100~200W的低功率轉換器,這些驅動器可以成功地集成到PWM控制器中以減少元件數,只要滿足一定條件便沒有問題。這些條件包括:MOSFET開關速度足夠快,讓開關損耗在可接受的範圍內;較高驅動電流脈衝產生的雜訊不會干擾控制功能;以及PWM IC的板上散熱易於管理。另一方面,在較高功率的轉換器中,一般採用單獨的驅動器IC以提供更大的驅動功率或更方便地管理雜訊和散熱。

此外,通過對控制器採用更低的電源電壓,以及採用較高電壓來驅動功率開關,可以提高電源效率,而柵極驅動器IC能夠很好地完成這種電平轉換工作。

為節約成本,有時也採用分立式元件來搭建簡單的柵極驅動電路,在不需要具有先進功能及性能的驅動器IC時,這樣做是可行的。不過,這種方案有不少局限性。例如,如果選定NPN/PNP射極跟隨器的輸出級,偏置電路的設計就必須謹慎,當電晶體的輸出飽和電壓高至快速開關電壓時,會導致輸出電壓的擺幅減小。如果在輸出端改用PMOS/NMOS反向器,控制邏輯必須適應這種邏輯轉換,而且當驅動器改變狀態時一般有部分擊穿。利用上述兩種技術的任一種,這種低增益級都需要輸入快速邊緣來產生快速的切換,需要更多的電路來執行電壓級轉換等功能,而元件數的增加對空間、裝配時間及可靠性都有不良影響。

柵極驅動器IC能夠解決上述大部分問題。它們集成有致能和欠壓鎖定(UVLO)等功能,可以輕鬆地在啟動、關斷和發生故障等最棘手的工作條件下控制功率開關。很小的邏輯門就能夠很容易地驅動高阻抗輸入,而且由於驅動器IC包含有帶正回授的高增益電路,故只要輸入電壓超過臨界值,輸出總是能夠快速切換。當IC需要設計以防止臨界值電壓隨過熱波動時,很容易通過在輸入端添加簡單的RC電路來插入一個固定延時。總而言之,IC驅動器能夠以超小封裝提供高性能和完善的功能-對2A驅動器,封裝尺寸小至2x2mm;對9A(或雙4A)驅動器,封裝尺寸小至3×3mm。

本文其餘部分將探討利用低端驅動器IC進行設計時的幾個重要考慮事項。首先,闡述了如何根據驅動器在電路中的作用來選擇其額定電流;其次,討論了一些特定功能可能在什麼地方有用,驅動器IC周圍通常需要哪些補償元件。最後,鑒於柵極驅動器IC很可能是電路中發熱最嚴重的元件,描述了簡單的熱性能評估方法。

驅動器大小的決定

使用低端驅動器的兩類常見開關是具有硬開關拓撲的初級端開關特徵的鉗位感應開關,以及同步整流。決定驅動器大小的標準各不相同,這裡做一個檢閱。

(圖一)所示為鉗位感應開關的理想導通波形,其特徵是漏源電流的上升和漏源電壓的下降之間沒有重疊。這產生最差情況的開關損耗,通常表示為整個轉換器開關時間TS上的平均功耗,即使實際功耗只發生在圖中的t2 & t3上。

(t2+t3)的長度取決於平均柵極驅動電流IG和MOSFET柵極穿越這些時間間隔所必需的電荷量,兩者都可以在 MOSFET規格中找到,或者是從總柵極電荷曲線上讀取。

關斷波形是(圖一)的鏡像圖形,可以採用類似的方法計算關斷開關損耗,並代入(公式一),求出該功率開關的總開關損耗。

從這些式子可明顯看出,在損耗時間間隔內,開關損耗與柵極驅動電流成反比。對於鉗位感應開關,開關損耗是決定柵極驅動器大小的主要指標。事實上,當它的輸出電壓接近工作範圍中間值時,最重要的驅動器特性是其輸出電流。

有不少供應商提供驅動器IC,標準大小有2A、4A和 9A,但不幸的是,測量這些電流的測試條件並不標準。對某些供應商,這是驅動某些已定義負載的近似峰值電流,對另一些供應商而言,它又是固定輸出電壓下的穩態電流,因此,兩款額定電流相同的驅動器可能具有截然不同的電流能力。若我們把輸出電壓範圍中間值下的穩態電流作為額定電流,則(表一)是個使用指南,顯示了當驅動器路徑上沒有外接電阻時,單位大小的驅動器提供或消除一定數量的柵極電荷的速度。這個表是通過(公式二)計算得出的,但考慮到實驗室測試條件的非理想化,乘以1.5的經驗系數。然而,這個系數仍然過於保守,因為即使沒有使用串聯柵極電阻時,功率開關的內部柵極阻抗也會減慢開關的速度。

(表一) 驅動器提供或消除一定數量的柵極電荷的速度

| |

|

Min. Switching Time (ns) |

|

| QG |

for Driver Current Rating |

| (nC) |

2A |

4A |

9A |

| 5 |

3.8 |

|

|

| 10 |

7.5 |

3.8 |

|

| 20 |

15? |

7.5 |

3.3 |

| 50 |

38? |

19? |

8.3 |

| 100 |

75? |

38? |

17? |

| 200 |

150? |

75? |

33? |

| 500 |

375? |

188? |

83? |

| 1000 |

750? |

375? |

167? |

當柵極驅動器與同步整流器(SR)一起使用時,大小標準又完全不同,由於體二極體在MOSFET溝道導通之前和之後都導通,故開關損耗可忽略不計。在這種情況下,所需要的驅動器電流取決於時序和防止由於dv/dt而導通。

為了防止擊穿導致不必要的功耗,必須在載入電壓之前完全關斷SR,一般是通過導通一個或多個初級開關來實現。為了確保這一條件得到滿足,同時讓SR盡可能長地保持導通狀態,以最大限度提高效率,必需知道需要多長時間來關斷SR。參考(圖二)中的MOSFET模型,可計算出關斷時間。

這裡,CGS=CISS-CRSS是MOSFET的線性柵源電容,CGDSR是低壓非線性柵漏電容或「密勒」電容CGD=CRSS。後者的選擇最好對應SR關斷期間電壓擺幅的中間值,VDD/2。這個值可從CRSS與電壓的關係曲線(若提供)讀取,也可以根據使用手冊給出的對應某些更高電壓VDS,SPEC的CRSS,SPEC值按照下式求出:

一旦SR完全被關斷,功率轉換器中的主要開關可導通,致使SR的漏源電壓急速上升。圖二顯示了這種情況,由CGD和CGS構成的電容性分壓器導致內部漏電壓增加-MOSFET短暫反嚮導通-除非驅動器吸入足夠多的電流使內部柵極節點保持在MOSFET的閾值電壓之下。這常常是決定SR驅動器大小的主要標準。在漏電壓剛開始上升時,CGD最大,所需吸入電流近似為:

如果一個較大的驅動器不能使用,而且它已經緊靠SR放置,避免因dv/dt導通的最終手段是通過減慢主要開關的導通速度來減小dv/dt,但遺憾的是這同時也增加了主要開關的開關損耗。

功能選擇

在選擇驅動器IC時,除了額定電流之外,設計人員還面臨著功能選擇的問題,也就是輸入邏輯及配置、輸入臨界值和封裝的選擇。對於單溝道驅動器,輸入形式包括反向、非反向、雙輸入和使能輸入等選項。要正確設置每一個MOSFET柵極控制信號的極性,通常需要在反向和非反向之間進行選擇,由單個控制輸出驅動時,不同開關有時選擇不同。如果兩種極性都需要,則雙輸入驅動器需要的不同元件更少,由於具有一個反向輸入,一個非反向輸入,故其可按二者中任一方式配置。若MOSFET開關時需要額外的控制,比如設置更高的UVLO閾值或啟動期間禁用SR一秒,使能輸入很有用。

驅動器可以帶有TTL 或 CMOS輸入電平。TTL「低」輸入定義為0.8V以下,「高」輸入定義為2.0V以上,與電源無關,故TTL臨界值近似恒定,總是保持在這兩個上下限之間。相反地,CMOS輸入閾值大約是電源電壓的40% 和 60%。TTL閾值更常見,在輸入信號 (比如來自低壓PWM控制器) 幅度較低時尤其有用。不過,CMOS具有更好的雜訊容限,故是嘈雜環境的首選。而且利用CMOS可以更精確地設置RC延時,因為其臨界值更接近電源電壓的一半。當需要精確時序時,輸入臨界值和傳播延遲的溫度穩定性也很重要。

大多數電源設計人員都很熟悉封裝的取捨問題,通常是在低成本的標準引腳封裝和尺寸更小、熱性能更佳的MLP封裝之間進行權衡,後者一般帶有裸露的散熱片幫助散熱。

補償元件

在利用驅動器IC進行設計時,有兩個補償元件十分重要:旁路電容和串聯柵極電阻。由於驅動器產生短電流脈衝,故需要阻抗極低的電源來提供最大電流,這通常是通過緊鄰驅動器放置一對旁路電容來實現,而驅動器本身也應該盡可能靠近功率開關放置以儘量減小這一電流回路的漏電感 (stray inductance)。這種較大的電容一般是電解電容器或另一種ESR值較低的電容器,其電容值是有效負載電容的2到10倍,可利用總柵極電荷通過下式求得:

其次,陶瓷旁路電容一般是該值的十分之一。當採用相同的電壓源對靈敏的控制電路進行供電時,良好的習慣是:在供電線路上串聯數歐姆的電阻,把驅動器部分和控制部分隔離開來。

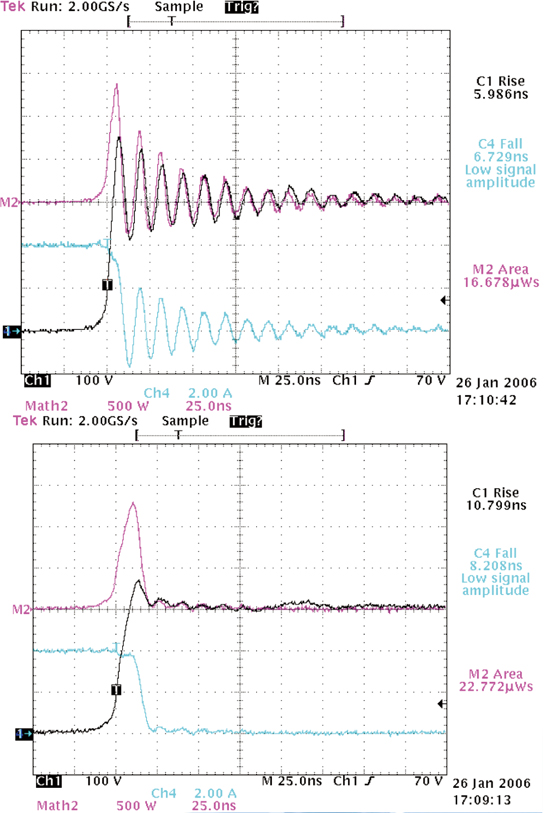

在驅動同步整流器時,驅動器和功率開關之間的串聯柵極電阻往往被忽略,但在實際中常常使用2到20歐姆的這樣一個電阻,原因有三:第一,可抑制功率開關柵極電容和柵極驅動回路漏電感之間的振鈴電流,如(圖三)所示,因為過多的振鈴電流會增加EMI,並因快速切換開關而增加損耗。其次,可減慢開關速度,從而降低EMI,不過會導致更高的開關損耗。第三個可能的原因是,使用一個串聯柵極驅動電阻可以把驅動器的柵極驅動損耗部分轉移到該外接電阻上,而總的柵極驅動損耗保持不變。

| 《圖三 在驅動器和功率開關間使用串聯柵極電阻的波形變化》 |

|

如上所述,對於具有控制良好的輸入閾值的驅動器IC,可以利用串聯電阻外加驅動器輸入端的小接地電容,在控制路徑上插入固定延時。

如(圖四)所示,在增加柵極驅動變壓器和若干其他元件之後,低端驅動器還可以用於驅動高端 (浮動) 開關,作為高壓驅動器IC的一種替代方案。這樣做的主要原因是,越過隔離邊界,縮短傳播延遲,實現更穩健的驅動電路。

| 《圖四 使用低端驅動器來代替高端驅動器的電路圖示》 |

|

熱設計

由於驅動器IC的功耗相當顯著,故應該關注熱設計問題。這是一個兩步過程:首先估算驅動器的功耗,然後計算結溫,確保其在設計限制範圍內。

對於這裡討論的簡單柵極驅動電路 (控制驅動和非諧振),與功率MOSFET 或 IGBT每週期開/關有關的總柵極驅動損耗可從開關的資料表給出的總柵極電荷曲線求得,即讀取對應所選柵極驅動電壓VDD的總柵極電荷QG,然後按下式計算:

這一功耗與串聯柵極驅動電阻的值無關,但會影響與驅動電路的其他串聯電阻相比驅動器IC所消耗的功率多少。事實上,驅動器IC功耗所占比例正好是它的有效輸出阻抗與驅動回路中所有阻抗總和之比,該值在導通和關斷時不同。要進行計算,估算驅動器的有效輸出阻抗的最簡單方法是:電源電壓的一半除以穩態源或二分之一電源電壓下的輸出鉗位吸入電流。其他應該計入內的回路電阻還有開關的外部和內部串聯柵極電阻,大容量旁路電容的ESR。因為這些電阻中有部分無法精確獲知,按照(公式八)求得的總柵極驅動功耗可以作為驅動器IC功耗的上限,或者計算值可以使用部分經驗值。

一旦確定了驅動器IC的功耗,資料表提供的無論何種熱參數都應用來估算最大結溫。結環熱阻JA是最常用的參數,但很遺憾它只在某些指定熱設計中很精確,比如PCB構建、散熱和氣流。在無頂部散熱器的低氣流中,大部分功耗集聚在PCB中。這時,如果結到引腳或結到電路板的熱阻給定,且若設計限制了PCB的最大工作溫度,假設引腳溫度等於最大板溫,則可求出工作結溫的上限:

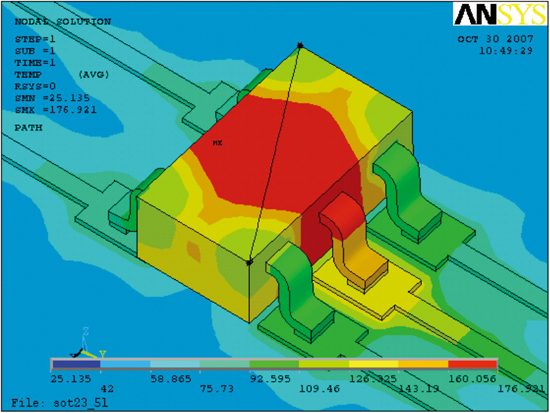

若結溫過高,重新選擇改進估算,提供更冷卻或選擇阻抗更低的驅動器。驅動器供應商要獲得更好的結果 (以及資料表提供的某些熱參數),對封裝和熱環境進行有限元分析是一種好方法,如圖五所示。

| 《圖五 一顆?SOT23-5封裝驅動IC進行有限元之分析結果》 |

|

小結

本文給出電源設計中如何利用低端柵極驅動器IC的設計指南。其中包括如何選擇適當的驅動器額定電流及功能,驅動器需要哪些支援元件,以及如何估算損耗和結溫。在開關電源設計中,通過正確運用柵極驅動器IC,能夠提高效率、減小尺寸並簡化設計。

參考文獻

[1] Balogh, L. “Design and Application Guide for High Speed MOSFET Gate Drive Circuits,” Power Supply Design Seminar SEM-1400, Topic 2, Texas Instruments Literature No. SLUP169.

--作者Van Niemela任職於快捷半導體公司功率類比設計部—