前言

在即將進入的2008年,電子產業將會何去何從呢?在2007年12月4日於矽谷舉辦的ConfigCon會議中,即以「YouTube世代的多媒體解決方案」為題,清楚指出個人化及高品質(HD)多媒體的應用將是未來市場發展的主流趨勢,並從市場、應用、設備、軟體及晶片技術等多個面向分別剖析必須克服的挑戰與解決途徑。

就市場面來看,包括ARC International執行長Carl Schlachte、Sling Media公司技術長Bhupen Shah和Intel架構師Jeffrey Hoffman皆在演說出指出,今日消費者對多媒體應用的期待是要能夠不受時間的限制(Anytime)、隨時可以使用(Anywhere)、各種設備皆能滿足需求(Any device),而且能利用各種的網路來實現(Any network)。

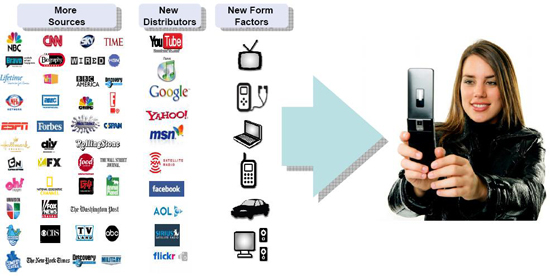

Carl指出,今日多媒體的傳播環境已產生巨幅的變化。除了既有的專業製播單位外,包括平面傳媒及個人都已成了網路化多媒體的創作來源;網路媒介的普及和寬頻的環境,也造就了YouTube、Google、Yahoo、flickr等新興的媒體中心;在設備端也不斷增加新的播放設備,除了電視、電腦外,連汽車和手持設備都強調數位多媒體的應用,而最終的目標是實現高品質的視訊多媒體手機。

| 《圖一 今日媒體革命下有更多的內容、媒體和設備,並往手機集中發展 》 | 資料來源:ConfigCon 2007,ARC |

|

對於這個娛樂革命的潮流,In-Stat首席分析師Gerry Kaufhold進一步剖析表示,使用者將自製內容上傳到網路上的型式,對於既有的通訊服務商及內容供應商造成極大的衝擊。今日高品質的錄影機已相當普及,甚至只要使用手機或數位相機,即能隨時隨地錄製生活中的影像,加上後製編輯工具及上傳管道的便利性,讓所有人都能成為節目製作人。在此同時,線上媒體的出現則創造了數億台低功耗高效能可攜式多媒體裝置需求商機。

率先上市才能獲利生存

面對這場多媒體的革命,半導體產業是否已做好因應的準備了呢?ARC總裁Carl指出,隨著應用類型的大幅增加,晶片的設計必須在技術的核心基礎上,去改善使用者的經驗、提升設備的可攜性,並加速產品的上市時程,然而目前能滿足這些消費者需求的設計並不多。他認為今日的多媒體晶片方案必須克服幾項重大的挑戰,包括支援廣泛且不斷更新的多媒體格式、提供高品質的編解碼能力、適合多樣化的可攜式造型設計、延長電池的續航力,並能加速上市的時程。

Cadence Design Systems公司副總裁Aurangzeb Khan也認為,無線和消費性電子是促進半導體產業成長的動力。目前各種應用與技術在無線及消費性電子市場出現巨大的匯流效應,為了在小型化的可攜設備中實現多樣化的功能,半導體產業已投入龐大的研發資源,並朝向系統化的設計方法去發展,以期做到最佳化的效能、高度的整合性與彈性,而且能將功耗降到最低。Aurangzeb指出,這種系統導向的設計已非個別公司能夠完成,而需要靠整個產業鏈的合作才行。

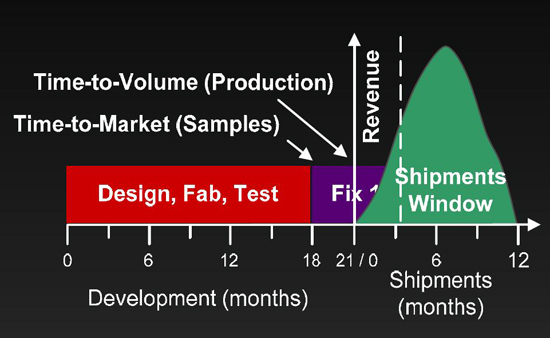

Aurangzeb明白表示,在產品生命週期短促的消費性市場中,只有率先上市的廠商才能獲利生存。今日的電子產品從設計、製造、測試到完成樣品,必須在18個月之內完成,並在樣品推出後的3個月內達到量產目標,而實際的出貨生命週期往往只有1年的時間。他指出只要晚了別人3個月上市,大約會損失5億美元的商機;若晚了半年才上市,整體的獲利大約就會損失31%。

| 《圖二 今日電子產品的開發與生命週期 》 | 資料來源:ConfigCon,Cadence |

|

從SD到HD的挑戰

整合性IP開發工具

因此,Carl認為,半導體的設計必須與消費者的需求緊密連結,這得從三大方向著手:(1)強化使用經驗;(2)提升可攜性;(3)加速上市時程。要滿足這些條件,今日的晶片設計必須在效能、彈性及功耗上獲得突破,這得採取創新的技術架構才做得到。ARC提出的做法是一套整合性的IP開發途徑,也就是以異質多核心的硬體處理架構為基礎,搭配視訊、影像及音訊的編解碼軟體IP,以及能加速設計的開發工具,讓多媒體晶片能夠支援多重格式、多樣化的設備,並具有高品質的編解碼能力。

可攜式設備邁向HD高畫質

目前一般手機或數位相機的攝影功能最多只能支援到QCIF或CIF的解析度,所能播放的視訊品質也只能達到標準解析度(SD)的程度。然而,ARC CTO辦公室Eugene Metlitski博士指出,高解析度(HD)的內容已愈來愈普及,市場上專業及一般消費性設備都開始被要求能支援HD的製作或播放,這也對小型化的可攜式設備帶來極大的設計挑戰。

表一 SD與HD的應用領域與支援規格 <資料來源:ConfigCon 2007,ARC>

應用領域 |

SD |

HD |

DVD

Blu-Ray, HD DVD

CH-DVD |

MPEG-2 |

MPEG-2

VC-1

H.264

AVS |

PVR, Cameras |

MPEG-4 |

H.264,VC-1 |

網路視訊 |

RealVideo 7/H.263+

On2 TrueMotion VP6 |

RealVideo 10

On2 TrueMotion VP7 |

監視系統 |

MJPEG,MPEG-4 |

MJPEG,MIPEG2K,H.264 |

Eugene博士表示,SD是一個發展10年以上的成熟領域,在音訊上要求立體聲和多聲道,視訊上則要能支援D1的規格。目前SD仍是重要的內容規格,晶片廠商也還致力於提升其運算和功耗上的效率。不過,HD對內容品質的要求比SD高出許多,不論是音訊或視訊內容,都需要更高的取樣速率及位元速率,也需要更多的記憶體容量及處理器資源。以視訊內容為例,HD的資料內容龐大,其訊框資料比SD多出6至8倍,資料傳輸率需要90~120 Mbps,HD的位元速率更可高達100 Mbps以上。

視訊高階編碼的技術難題

設計者總希望影音處理能以更高的壓縮率來獲得不失真的品質,而且能以更少的處理資源來達成複雜的運算。然而,現實上總是有其侷限,Eugene博士即指出,多媒體設備的處理資源與通訊頻寬是主要的限制所在。視訊的高階編碼更是主要的瓶頸所在,舉例來說,若以32位元RISC來進行H.264的HD編碼,會需要18 GHz的時脈頻率才做得到,但這在現實上是不可行的;在嵌入式運用中要求最小的時脈頻率,在可攜式設備上更要求需以200 MHz以下的時脈頻率來達成。

目前的多媒體設計方案主要採取兩種途徑,一是採用硬連線(Hardwired)的專屬加速器來提升運算效能,但此方式只能支援固定的功能,難以滿足持續演進的多媒體規格標準;另一種方式是採用通用型DSP來提供可程式性,但此方式也有侷限性,通常會有晶粒太大、功耗較高的問題,而且目前仍缺乏對高解析度應用的支援。Eugene博士表示,必須設計出平衡架構的平行運算系統,才有可能在可攜式的嵌入式環境中實現HD的編解碼需求。

異質多核心平台特色

ARC CTO辦公室Akash Deshpande博士進一步指出這個HD多媒體開發平台的特色如下:

- ●透過RISC/SIMD/Logic等異質多核心來達成高效能的處理能力;

- ●透過動態電壓頻率調整(DVFS)和多重電源域(power domain)等技術來大幅降低系統功耗;

- ●利用可組態能力來縮小晶片尺寸;

- ●使用可重覆利用的模組化IP建置區塊及scale-aware拓樸設計工具來滿足延展性需求;

- ●使用開放、多工具設計流程來清楚掌握整個系統的運作行為,以降低設計的複雜度;

- ●由於具有軟體可編程性,因此能因應新技術規格而立即更新版本;

- ●提供預驗證合格的解決方案元件、設計自動化和多團隊合作機制,有助於加速上市時程;

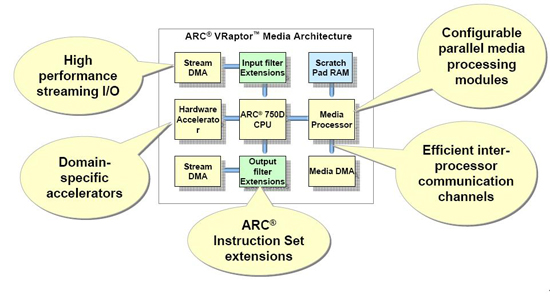

為了兼具執行效能、可程式性以及低功耗特性,ARC提出一套異質、平行、可延展及多核心的系統架構,稱為VRaptor。在此架構中包括了三種不同類別的處理器核心:第一類是ARC的可組態32位元RISC核心和多種特殊SIMD多媒體處理器,針對解塊低通濾波器(low-pass deblocking filters)和圖素轉換等提供最佳化功能;第二類為硬體加速器,例如熵編解碼器(Entropy encode/decode)以及運動估算(Motion Estimation)等,在執行多媒體處理工作上,比一般用途可編程核心的效率更高;第三類包括高速DMA控制器,能解決CPU在處理多媒體編解碼所涉及的複雜資料移動。

| 《圖三 ARC Vraptor多核心媒體處理架構示意圖 》 | 資料來源:ConfigCon,ARC |

|

ARC首席架構師暨愛丁堡大學資訊系教授Nigel Topham博士指出,透過這種異質核心架構,用戶能夠根據其需求做彈性的可配置設計。以HD的設計來說,其運動向量範圍遠大於SD,因此其運動估算的執行動輒會需要1 Gbps ~1.5 Gbps的記憶體頻寬;運動補償(Motion Compensation)也會需要用掉500 Mbps的記憶體頻寬。對於這類耗費大量運算資源的動作,在異質核心架構中可選用硬體加速器來提升效率;至於需考慮設計彈性的功能,則可利用軟體方式來進行。

Nigel博士表示,媒體的編解碼其實具有高度的平行性,可透過平行運算來做到最佳化的資源分配。以圖素轉換為例,其控制簡單,極適合使用一般性的SIMD指令集;相較之下,低通濾波器也具平行性,但控制上較為複雜。因此,多核心的平行運算架構會是多媒體處理的最可行作法。

以ARC的視訊子系統方案為例,其最高階的AV417V若採用130nm製程,以10.27mm2的晶片面積即可以200MHz的速度執行D1/30fps的H.264 BP編碼,並達到10Mbps視訊串流位元速率;或是以160 MHz執行D1/30fps的H.264 BP解碼,也能達到1.5Mbps視訊串流位元速率,且其功耗在100mW左右。

NoC為SoC效能決定關鍵

要在SoC中實現複雜且高速的異質核心平行運算,處理單元內部通訊(Inter-Processor Communication;IPC)的機制已成了決定性的關鍵。Nigel博士指出,多核心架構中必須採用分享式記憶體和密合的快取途徑,也就是得避免高速通訊中發生快取上的延遲,這對記憶體架構是很大的挑戰;另一個需求則是透過NoC(Network-on-chip)的通訊架構來加速訊息的傳遞。

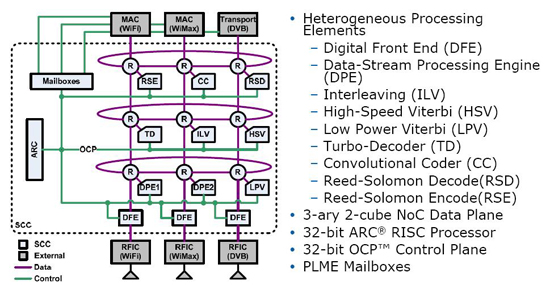

Intel架構師Jeffrey則從無線通訊的角度來剖析SoC互連性的問題。他認為今日有太多的無線技術,如WiFi a/b/g/n、WiMAX、3G、UWB、Bluetooth、DTV、GPS、NFC等,當要整合在一起時,就會出現RF干擾和尺寸過大等問題。然而,今日的無線技術其實採用了許多相同的演算方法,如FIR/IIR、相關性(correlation)、通道估算(Channel estimation)、QAM mapping、Interleaving、常規編碼(Conventional Coding)、Randomization等,這些演算法都能透過DSP來運算。

因此,透過晶片資源的分享,無線晶片有機會做得更小、更有效率,也更有彈性,而且能改善共存性。不過,Jeffrey也指出,記憶體架構與互連性將是設計上的主要關鍵。就互連性考量,相較於Full Matrix、Split Matrix、Sparse Matrix等互連方式,NoC能提供最小功耗及最大彈性。對此,Intel提出3-ary 2-cube的NoC架構,能夠有效進行資訊流與資源的分享,適用於Wi-Fi、WiMAX和DVB-T的MAC設計當中。其中也利用到ARC的32-bit RISC,用來與MAC交換管理與控制訊息。

| 《圖四 Intel提出3-ary 2-cube的NoC架構 》 | 資料來源:ConfigCon 2007,Intel |

|

低功耗設計之解決途徑

在實現HD可攜式多媒體應用的同時,另一個不能忽視的問題則是電池續航力的問題。如果一台PMP或手機能支援高品質的視訊內容,但很快就會把電力消耗殆盡,這樣的產品也無法獲得消費者的認同。因此,低功耗設計已成了可攜式及行動設備的主要課題。

就多媒體處理而言,ARC提出一項動態編碼(Dynamic encoding)技術。Nigel博士解釋說,視訊編碼是一項重複性的工作,藉由執行一組演算法而將數位視訊串流或數位靜態影像編碼成H.264 BP、MPEG4-SP/ASP、H.263 profile 0和JPEG等格式。動態編碼技術會依CPU的時脈及運算的複雜度來持續評估系統資源,並調配運用不同處理資源及編碼方式,以達到最佳結果。例如,動態編碼允許設計業者根據手機的電力狀態(充飽電或者即將耗盡電力)來調整編碼程序,以達到功率最佳化的效果。

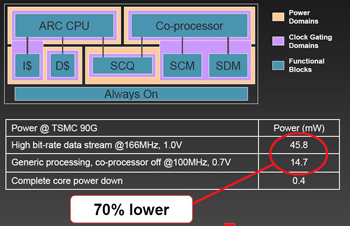

就晶片設計的低功耗設計方法學上,ARC也提出一套整合軟硬體和EDA設計流程、函式庫的Energy PRO電源管理技術。Nigel博士指出,Energy PRO運用了今日先進的低功耗技術,例如採用時脈閘(clock gating)技術,能在處理單元閒置時關閉時脈,以便將功耗減少至額定功耗(Nominal Consumption)的10%以下。此外,採用多重電源域(power domain)技術能讓裝置於閒置時可選擇性的關閉,讓整體功耗降至幾乎等於零;在僅需要運用部分功能時,則可採用動態電壓頻率調整(DVFS)技術,將功耗減少約75%。

| 《圖五 ARC Energy PRO能大幅降低功耗 》 | 資料來源:ConfigCon 2007,Cadence |

|

Energy PRO能在SoC上實現智慧型的功率管理,讓每一個邏輯或記憶體元件不論何時都僅耗用維護執行效率所需的最低功率。它提供一個硬體介面,讓設計業者將低功率技術延伸到SoC的其他部分,以協調整體SoC的功率管理,發揮這項技術的最大效益。在軟體方式,Energy PRO亦提供一個軟體API,讓設計工程師利用Energy PRO的功率控制功能。Energy PRO API軟體可以與多種作業系統相容,或者直接應用於裝置而不需要額外的作業系統。ARC的MetaWare工具可以為Energy PRO提供程式設計支援。

產業性的低功耗規範

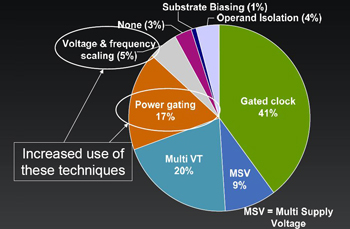

針對低功耗設計,Cadence副總裁Aurangzeb以更全面的角度提出他的看法。他指出目前的SoC設計強調將電源最佳化的方法學整合進來,採用的技術包括時脈閘(Gated clock)、電源閘(Power Gating)、電源關斷(PSO)、多供應電壓(MSV)和DVFS等等。其中又以DVFS和Power Gating等技術愈來愈受到重視。這些技術的使用確實能有效降低電源的消耗。

| 《圖六 今日常見的低功耗設計策略 》 | 資料來源:ConfigCon 2007,Cadence |

|

Aurangzeb表示,就EDA的角度來看,在邏輯上的設計流程雖具有連貫性,但對功耗控制來說卻是獨立的,EDA在這方面的支援就顯得支離破碎。因此Cadence與二十多家業者共同成立PFI(Power Forward Initiative),目的是致力於推動通用功率格式(Common Power Format;CPF),以建立結合貫穿設計、設計實現與設計驗證等流程的電源設計規格。

CPF是在設計過程初期詳細定義節約功耗技術的標準化格式。通過在整個設計過程中保存低功耗設計意圖,該解決方案避免了費力的人工作業,大大降低了與功耗相關的晶片故障,並在設計過程初期提供功耗的可預測性。目前PFI已在2006年末將其制定的CPF 1.0規範捐給業界Si2聯盟的LPC(Low Power Coalition)組織,並由LPC負責CPF的推進。LPC已經審核了CPF 1.0,按照Si2標準化進程,已將CPF暫時批准為Si2規格。

| 《圖七 ARC International執行長Carl Schlachte》 |

|

結論

在本次會議中,可以感受到數位多媒體應用正以各種型式進入到每個人的生活當中,然而在技術的實現上卻仍有許多瓶頸需要克服。以HD高解析度視訊來說,對於可攜式嵌入式設備的運算資源將造成很大的挑戰,必須提出創新的處理架構才有可能實現。

ARC的可組態、異質多核心架構為此需求提供了一個途徑。透過有效的平行運算及資源分配,此一多核心平台有助於在效能、彈性與低功耗等要求中取得一個平衡點。然而,此架構對於業界來說仍然相當新穎,預估市場仍需跨越一段學習曲線,而這也是這類廠商致力於發展完善且便利的開發工具的主要原因。

(作者為電子技術資深自由作家,聯絡方式:ou.owen@gmail.com )