頻率合成器在無線通訊系統中,扮演著一個重要的角色,無論是發射機、傳輸機,都需要頻率合成器來產生本地震盪頻率。舉凡手機應用GSM 900MHz與DCS 1800MHz的工作頻率,藍芽(Bluetooth)和無線區域網路WLAN IEEE802.11 b/g工作在2.4GHz的頻段,或是UMTS/WCDMA工作在2.1GHz的頻段。這些系統都需要相當精確的高頻時脈產生器,但是一般而言用於產生時序脈波的石英振盪器通常無法達到那麼高的頻率,所以使用鎖相迴路(Phase Lock Loops, PLL)將頻率倍頻上去達到所需之規格。鎖相迴路頻率合成器可分成整除數頻率合成器(Integer-N Frequency Synthesis)以及除小數頻率合成器(Fractional-N Frequency Synthesis)。相較於整除數頻率合成器,除小數頻率合成器的優點在於可使用較高的參考頻率(Reference Frequency)、迴路頻寬(Loop Bandwidth)以及有較高的頻率解析度(Frequency Resolution),其中迴路頻寬越高鎖定速度(Settling Time)越快。

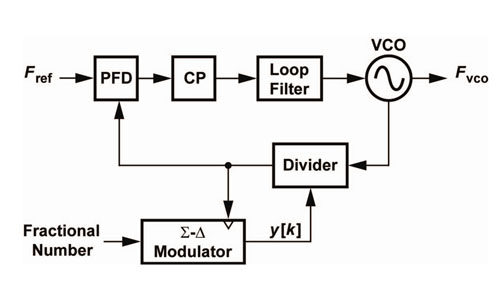

《圖一 傳統的除小數頻率合成器》

|

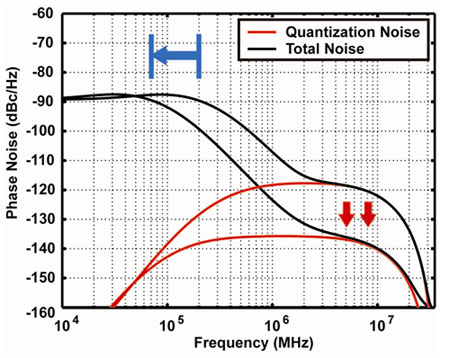

早期除小數頻率合成器是利用累加器(Accumulator)產生溢位訊號來控制除頻器(Divider)產生小數之除數。然而,在這種架構下溢位訊號為規律的控制訊號,如此會產生小數突波(Fractional Spur)。為了克服這個問題,傳統的除小數頻率合成器通常是使用三角積分調變器(Delta-Sigma Modulator)來控制除頻器,如圖一。三角積分調變器的輸入為一個小數值,而輸出則是一序列的整數,其平均值等於輸入的小數值。輸出的訊號內包含了量化誤差(Quantization Error),由於此量化誤差(又稱量化雜訊)的頻譜具有高通的特性,經過鎖相迴路電路的低通閉迴路(Close Loop)後會被過濾一部份。在設計這類頻率合成器時須注意高通的量化雜訊是否太大。有時為了衰減量化誤差會設計較低的閉迴路頻寬,如圖二。但這樣卻會造成鎖定時間變長以及電壓控制震盪器的相位雜訊效應變大。

《圖二 減少頻寬可降低相位雜訊》

|

《圖三 藉由補償電路降低量化雜訊》

|

為減少量化誤差又不影響迴路頻寬大小,在除小數頻率合成器中常會再加上補償電路(Compensation Circuit),如圖三。常見的補償電路比如:DAC 、多相位振盪器(Multiphase VCO)等等。此架構是使用延遲元件(Delay Cell)產生相位的補償來減少量化誤差。由於在實際電路中拉線不對稱、寄生效應、溫度及製程變異等影響會造成一些非線性的現象,像是延遲元件(Delay Cell)不匹配、充電泵(Charge Pump)不匹配等,都會造成迴路頻帶內的相位雜訊(In-Band Phase Noise)和突波(Spurs)增加。本文著重於增進三角積分調變的除小數頻率合成器的線性度,在此架構中會使用動態器件匹配技術電路 (Dynamic Element Matching)和偏移電流(Offset Current)的技巧來增進電路線性度,改善迴路頻帶內的雜訊和突波。

使用多相位補償的除小數頻率合成器

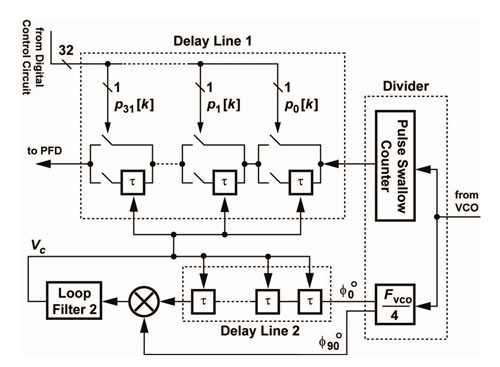

《圖四 除小數頻率合成器電路》

|

此為設計一個操作在UMTS/WCDMA 2.1GHz頻段的除小數頻率合成器。整個除小數頻率合成器電路。如圖四所示。輸入的參考頻率訊號為35MHz,輸出為2.1GHz。其架構主要包括:延遲線路1(Delay Line 1)、相頻偵測器(Phase Frequency Detector, PFD)、電流幫浦(Charge Pump, CP)、迴路濾波器1(Loop Filter 1)、電壓控制震盪器(Voltage Control Oscillator, VCO)、除頻器 (Divider)、延遲鎖定環(Delay-Locked Loop)和數位控制電路(Digital Control Circuit)。其中由延遲線路1、延遲鎖定環和數位控制電路所形成的相位補償電路就是用來減少量化雜訊的設計。圖五為相位補償電路。

《圖五 相位補償電路》

|

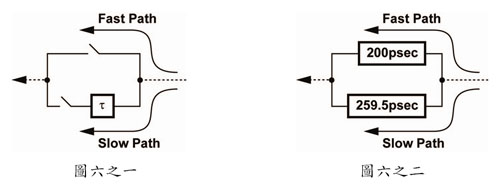

《圖六 延遲單元》

|

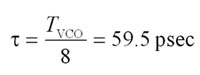

延遲線路1由三十二個延遲單元(Delay Unit)串聯而成,圖六之一為延遲單元的示意圖。為延遲元件的延遲時間。當控制訊號pi[k]=0時,輸入訊號將走快途徑(Fast Path);當控制訊號pi[k]=1時,輸入訊號將走慢途徑(Slow Path)。而數位訊號pi[k]則由數位控制電路所產生。延遲元件的總數是由三角積分調變器的量化誤差以及延遲元件的延遲時間來決定,在稍後介紹數位控制電路的段落中會做更詳細的解釋,這裡則先介紹延遲元件的延遲時間。由於設計以衰減量化誤差至原本的1/8倍為目標,如此可減少約18dB的高通相位雜訊,又因為頻率合成器是操作在2.1GHz的頻帶,所以延遲元件之延遲時間為

《公式一 》  |

此延遲時間是用電壓控制震盪器和延遲鎖定環來控制,如圖五。因為頻率合成器的輸出頻率Fvco會隨所選定的頻帶(Channel)而改變,因此為了產生Tvco/8使用了延遲鎖定環。電壓控制震盪器的輸出先降頻至Fvco/4再取0o和90o相位的訊號做鎖定,如此先降頻的動作可以減低功率的損耗,又取0o和90o相位的訊號做鎖定可以減少延遲鎖定環中所須的延遲元件。

實際上要產生一個59.5psec的延持時間在0.18m製程中是有困難的,幸而所須的59.5psec僅是一個相對值,比如走快途徑時有200psec的延遲,而走慢途徑有259.5psec的延遲也是可以的,見圖六之二。因此,也可以設計更小的延遲時間<59.5psec。但是,並不表示元件的延遲時間越短越好。理論上若是設計更小的延遲時間來做相位補償則量化雜訊會更少,但是這樣延遲元件的數量會更多,會耗費能量以及晶片面積。而且實際電路中延遲元件的不匹配會抵消原本理想中的衰減量,甚至是產生頻帶內雜訊及突波雜訊。

《圖七 數位控制電路》

|

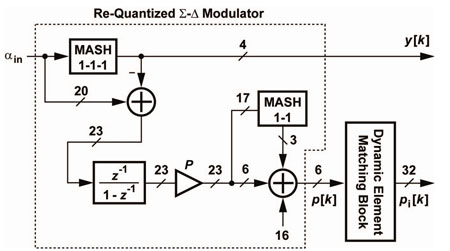

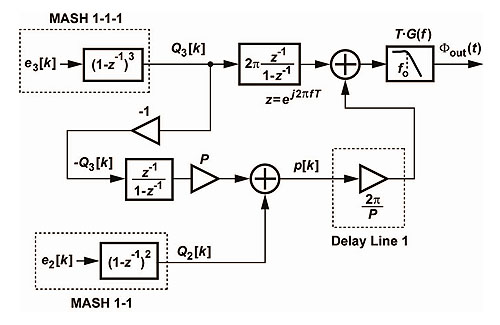

圖七為數位控制電路。數位控制電路主要包含三角積分調變器、積分器、乘法器、加法器以及動態器件匹配技術電路。第一個三角積分調變器MASH 1-1-1的輸出用來控制除頻器的除數;第二個三角積分調變器MASH 1-1的輸出則控制延遲線路1中延遲單元走快路逕的總數;動態器件匹配技術電路的輸出則指定延遲線路1中那些延遲單元操作在快路徑。當y[k]決定除頻器的除數時,除法器的輸出訊號會產生。如圖八之一較大的相位量化誤差。此較大的量化誤差可在數位控制電路中計算得到,再送進第二個三角積分調變器做再量化(Re-Quantization)得p[k]訊號,p[k]控制延遲線路1的總延遲時間。若讓除頻器輸出訊號先經過延遲線路1做相位補償則可以減少量化誤差,如圖八。

《圖八 相位補償示意圖》 - BigPic:599x233  |

《圖九 數位電路的數學模型》

|

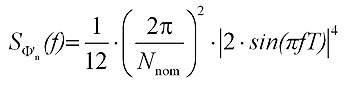

圖九是數位電路的量化誤差數學模型。MASH 1-1-1輸入in,輸出為

《公式二 》  |

Q3[k]為MASH 1-1-1的輸出量化誤差,將此量化誤差值積分後輸入MASH 1-1得

《公式三 》  |

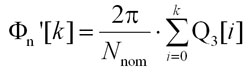

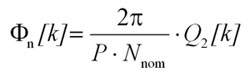

Q2[k]為MASH 1-1的輸出量化誤差。由於y[k]控制除頻器的除數,因此除頻器輸出訊號的相位量化誤差

《公式四 》  |

其頻譜為

《公式五 》  |

其中

《公式六 》  |

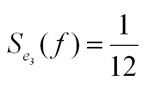

假設e3為白雜訊則

《公式七 》  |

由公式五~七可得除頻器輸出訊號的相位雜訊

《公式八 》  |

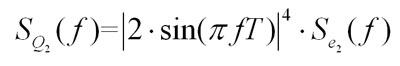

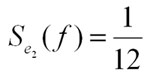

p[k]控制延遲線路1的總延遲時間,因此除頻器的輸出訊號經過延遲線路1後的相位量化誤差為

《公式九 》  |

P為Tvco/的比例,工作中為8。公式九的頻譜為

《公式十 》  |

其中

《公式十一 》  |

假設e2為白雜訊(white noise)則

《公式十二 》  |

由公式十~十二可得延遲線路1輸出訊號的相位雜訊為

《公式十三 》  |

T為參考訊號(Fref)的週期。從公式13中可以看到在做補償前後量化誤差的能量差(1/P)2,即在理想情況下使用延遲元件做相位補償時頻率合器輸出訊號的量化相位雜訊可減少約18dB。

圖十為除小數頻率合成器的數學模型,圖中可以看到數位控制電路產生的量化誤差對頻率合成器輸出訊號的相位雜訊影響。數位控制電路產生的量化誤差對頻率合器輸出訊號的影響為

《公式十四 》  |

G(f)為頻率合成器的閉迴路轉移函數。

《圖十 除小數頻率合成器的數學模型》

|

《圖十一 》  |

接下介紹延遲單元的個數是如何取得的。延遲單元的個數正比於MASH 1-1-1所產生的量化誤差,並跟單位元件之延遲時間成反比,即

《公式十五 》  |

用CppSim[5]模擬數位控制電路,得到p[k]的輸出範圍介於+16~-16之間,如圖十一,因此在延遲線路1中使用了三十二個延遲單元。

由於在實際電路中拉線不對稱及製程變異等影響會使延遲元件產生不匹配的情形,增加迴路頻帶內的相位雜訊和突波。為了改善這些非理想情形,在架構中使用了動態器件匹配技術電路來增進電路的線性度。動態器件匹配技術電路有許多種,比如DWA(Data weighted algorithm)、Tree Structure、Scrambling等。參考DWA的方式,因為DWA能實現一階的不匹配雜訊整型且比較容易實作。圖十二為使用動態器件匹配技術電路前後延遲元件不匹配對頻率合成器輸出訊號的影響。

《圖十二 相位雜訊示意圖》  |

相頻偵測器及充電泵

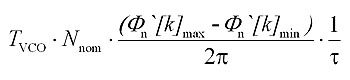

如圖十三,相頻偵測器及電流幫浦的非裡想效應會使除小數頻率合成器中產成迴路頻帶內的相位雜訊或是造成馬刺突波的現像。如圖十四之一和圖十四之二分別為理想的充電泵和充電泵有10%的不配時除小數頻率合成器的輸出訊號相位雜訊。

《圖十三 》  |

《圖十四 相位之補償示意圖》 - BigPic:579x256  |

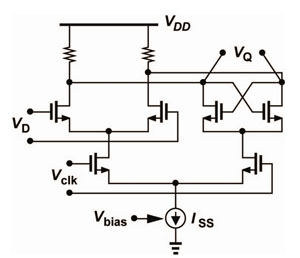

《圖十五 相頻偵測器》  |

為了改善電路的線性度而使用偏移電流,偏移電流的目地是為了使相頻偵測器輸出訊號Dn有固定的方波長度,而只有Up的方波長度會改變,如此可使相頻偵測器及充電泵操作時避開非線性區。相頻偵測器的電路圖及操作方式如圖十五所示。

圖十六為電流幫浦的電路圖,為了加快電流幫浦的切換充放電速度,選用此電路架構可使電流源一直保持在導通狀態,充電泵的左側為複製電路(Dummy Circuit),這樣的做法也可以減少電荷分享的效應(Charge Sharing)。使用NMOS和PMOS組成的傳輸閘(Transmission Gate)可減少電荷注入效應(Charge Injection)。在線路cpout和ref中間有個增益為1的運算放大器,是為了讓兩點的電壓相同,這樣也可以減少電荷分享的效應。

《圖十六 》  |

除頻器及電壓控制震盪器

《圖十七 》  |

《圖十八 》  |

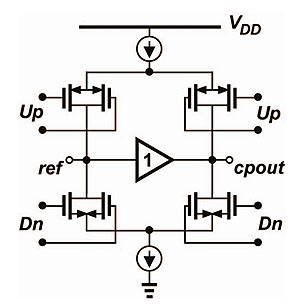

除頻器,採用Pulse-Swallow Counter架構,如圖十七。可以實現57到72的整數除數。Prescaler部份,因為是輸入電壓控制振盪器的高頻訊號,約為2.1GHz左右,所以採用操作速度較快的Current Mode Logic(CML)的D-Latch,如圖十八。

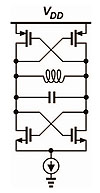

《圖十九 》  |

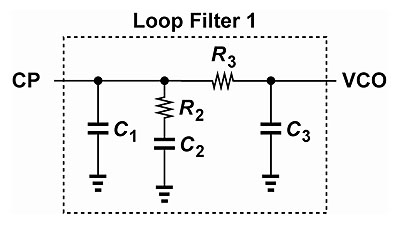

電壓控制震盪器架構如圖十九所示。電壓控制震盪器的振盪頻率操作在2.1GHz,Kvco設計在200MHz。壓控震盪器是採用電感-電容槽的架構,為了節省面積,使用對稱式的電感來實現。利用調整可變電容的電容值來改變其震盪頻率,注意這裡輸出端的寄生電容負載也同樣影響著震盪頻率,所以在設計時需要將寄生的負載也考慮進去以免頻率可調範圍跑出設計範圍之外。另外為了補償可能因製程變異而造成的頻率飄移,加入了三組開關電容,以三位元的數位訊號控制負載電容的大小,以達到消除製程變異影響的目的。迴路濾波器1為三階被動式RC濾波器,如圖二十。各被動元件之參數見圖二十一。

一

《圖二十 》  |

《圖二十一 》  |

頻率合成器之量測結果

《圖二十二 》

|

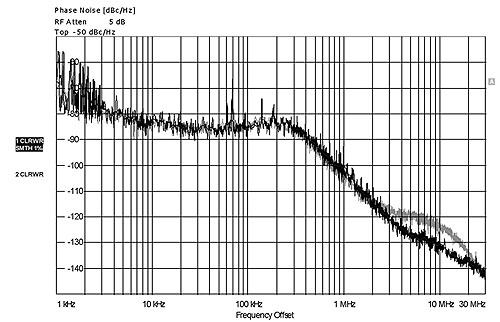

《圖二十三 》

|

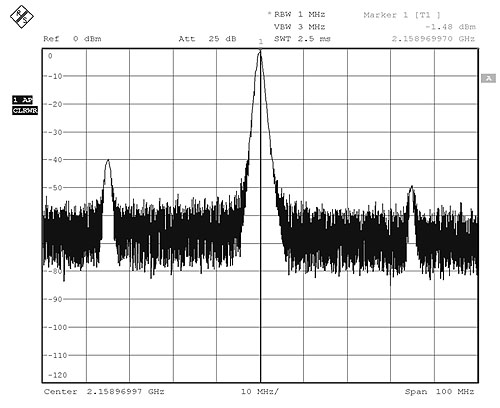

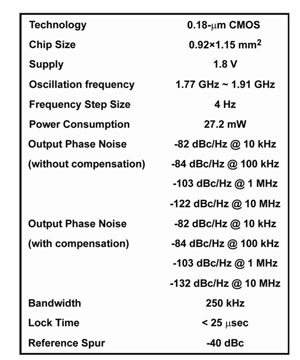

本頻率合成器是設計操作在UMTS/WCDMA 2.1GHz頻段的除小數頻率合成器,使用台積電0.18m的製程。圖二十二為量測的頻率合成器鎖定時之輸出訊號頻譜圖,其操作頻率為2.15GHz。圖二十三為量測的輸出訊號之相位雜訊頻譜(Phase Noise Spectrum),分別測試了兩種情況,第一為沒有使用多相位補償技術的情形,第二則是使用多相位補償技術的情況。從圖中可發現在距中心頻率10 MHz處之相位雜訊可得10dB之增益。整個除小數頻率合成器所消耗之電量為27.2 mW。頻率合成器之鎖定時間少於25 sec。圖二十四為量測結果的整理。

《圖二十四》  |

結語

本文實現了一個除小數頻率合成器,使用三角積分調變器來控制除數並利用延遲元件產生相位的補償來減少量化雜訊。由於在實際電路中拉線不對稱、寄生效應、溫度及製程變異等影響會造成一些非線性的結果,在此頻率合成器中使用了動態器件匹配技術電路和偏移電流的技巧來增進電路線性度,改善迴路頻帶內的雜訊和突波。本文使用台積電0.18m的製程設計了一個操作在UMTS/WCDMA 2.1GHz頻段的除小數頻率合成器。量測的結果發現使用延遲線路做相位補償可以減少約10dB的相位量化雜訊。

<作者李泰成為美國加州大學洛杉磯分校電機博士,現任台灣大學電子工程研究所副教授;陳兆人為國立台灣大學電子工程碩士,現為台灣大學電子工程研究所專任研究助理>

參考文獻

[1] Tom A. D. Riley, Miles A. Copeland and Tad A. Kwasniewski, “Delta-Sigma Modulation in Fractional-N Frequency Synthesis”, IEEE J. Solid-State Circuits, vol.28, no.5, pp. 553-559, May 1993.

[2] E. Temporiti, G. Albasini, I. Bietti, R. Castello, and M. Colombo, “A 700-kHz Bandwidth Sigma-Delta Fractional Synthesizer with Spurs Compensation and Linearization Techniques for WCDMA Applications”, IEEE J. Solid-State Circuits, vol. 39, no. 9, pp. 1446-1454, Sep. 2004.

[3] Chun-Huat Heng and Bang-Sup Song, “A 1.8-GHz CMOS Fractional-N Frequency Synthesizer With Randomized Multiphase VCO”, IEEE J. Solid-State Circuits, vol.38, no.6, pp. 848-854, June 2003.

[4] Sudhakar Pamarti, and Ian Galton, “A Wideband 2.4-GHz Delta-Sigma Fractional-N PLL with 1-Mb/s In-Loop Modulation,” IEEE J. Solid-State Circuits, vol. 39, pp. 49-62, Jan. 2004.

[5] Michael H. Perrott, “Fractional-N Frequency Synthesizer Design Using The PLL Design Assistant and CppSim Programs” , http://www-mtl.mit.edu/~perrott , July 24, 2004

[6] Rex T. Baird and Terri S. Fiez, "Linearity Enhancement of Multibit AY, A/D and D/A Converters Using Data Weighted Averaging", IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-I1 ANALOG AND DIGITAL SIGNAL PROCESSING, VOL 42, NO. 12, DECEMBER 1995

[7] Ian Galton, "Spectral Shaping of Circuit Errors in Digital-to-Analog Converters" , IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: ANALOG AND DIGITAL SIGNAL PROCESSING, VOL. 44, NO. 10, OCTOBER 1997

[8] Robert Adams, Khiem Q. Nguyen, and Karl Sweetl, "A 113-dB SNR Oversampling DAC with Segmented Noise-Shaped Scrambling" , IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 33, NO. 12, DECEMBER 1998

[9] Thomas A.D. Riley, Norman M. Filiol, Qinghong Du and Juha Kostamovaara, "Techniques for In-Band Phase Noise Reduction in Delta-Sigma Synthesizers," IEEE Trans. Circuits Syst. II, Vol. 50, No.11, pp. 794-803, Nov. 2003.